QuartusII设计流程与仿真指南

需积分: 5 185 浏览量

更新于2024-07-09

收藏 3.07MB PDF 举报

"QuartusII应用向导,涵盖了从建立工作库、创建工程、设置编译选项、进行时序仿真到引脚设置和硬件验证的全过程。"

在电子设计自动化(EDA)领域,Altera公司的Quartus II是一款广泛使用的FPGA(Field-Programmable Gate Array)设计软件。本章节主要介绍了如何使用Quartus II进行基本的设计流程,特别是针对VHDL语言的项目。

首先,设计流程始于创建工作库文件夹和编辑设计文件。这包括在本地计算机上新建一个文件夹来组织所有相关的设计文件,接着使用Quartus II输入源程序,这是设计的核心部分,由VHDL代码构成,描述了硬件逻辑。完成代码编写后,需要将文件保存到刚才创建的文件夹中。

接下来是创建工程,这是Quartus II项目管理的基础。用户需打开软件并新建工程管理窗口,然后将设计文件添加到工程中,选择适合的FPGA目标芯片。在选择芯片后,还需要对工具进行一些基本设置,比如配置器件的工作模式,以满足特定的应用需求。

在编译前,需要进行一系列的设置。这包括指定FPGA的目标芯片型号,确定配置器件的工作方式(如静态或动态配置),选择编程方式(如JTAG或串行配置),以及设定目标器件引脚端口的状态,确保设计能正确映射到硬件。此外,还需要确认使用的VHDL语言版本,以确保软件能正确解析代码。

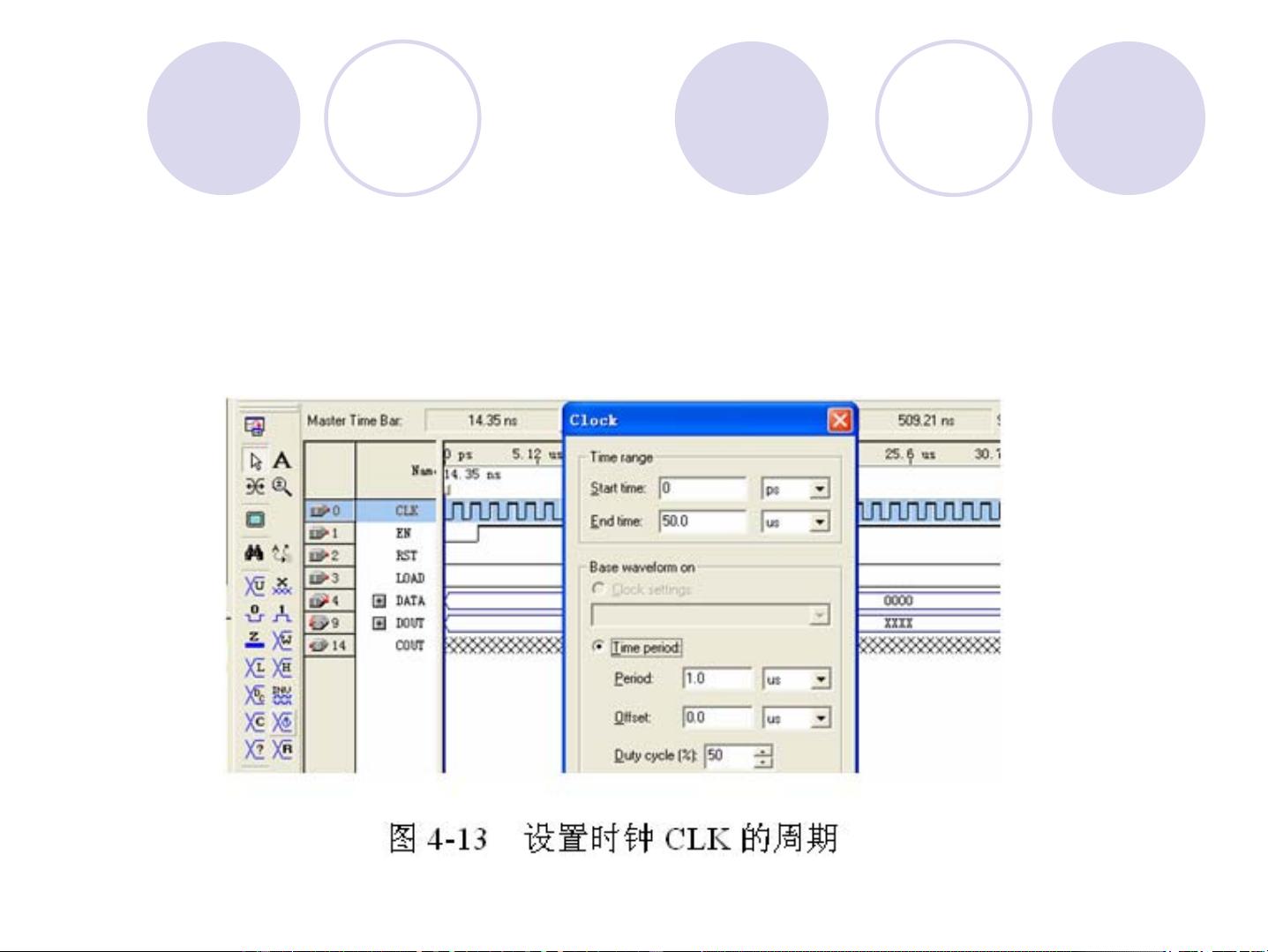

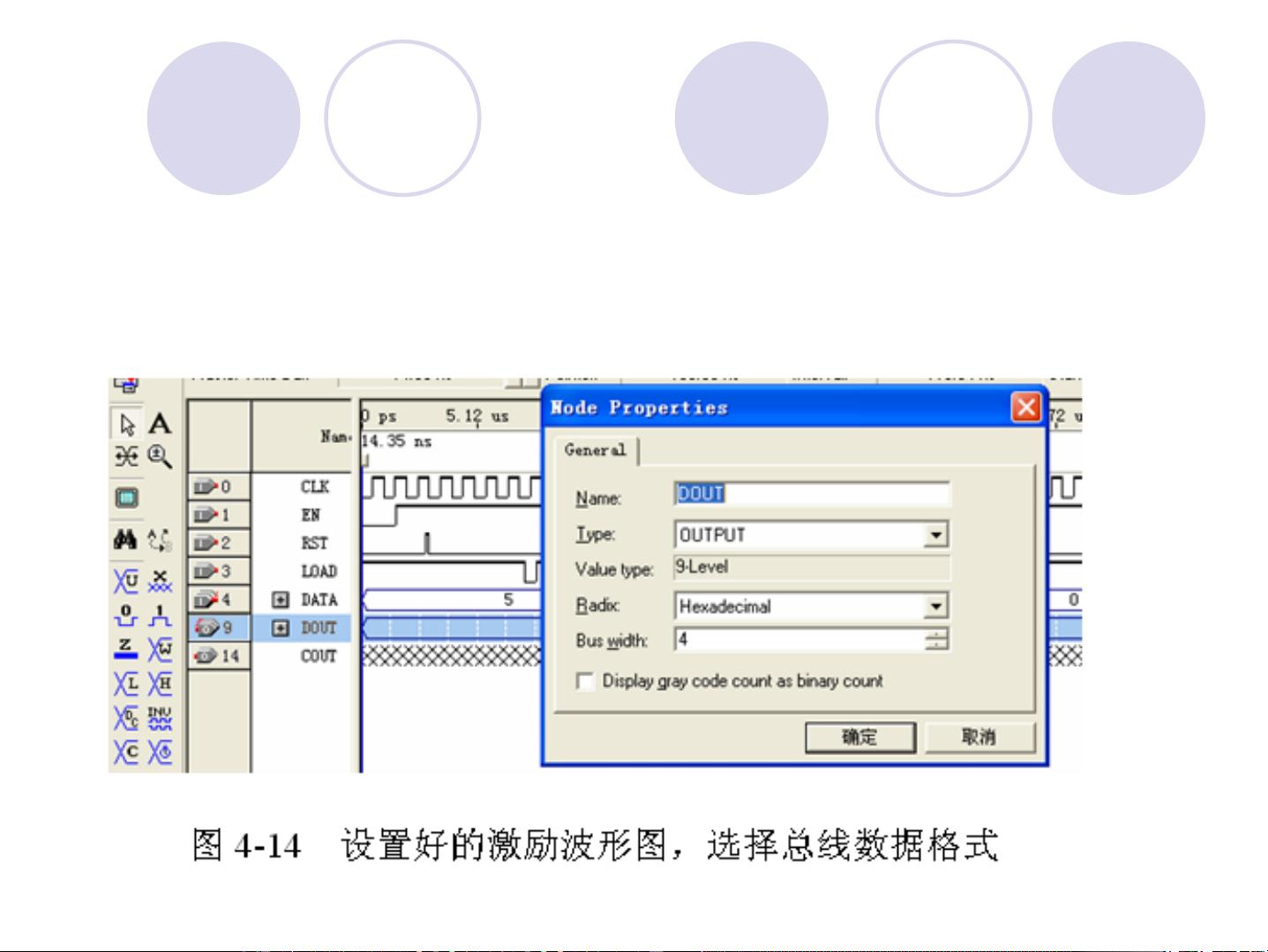

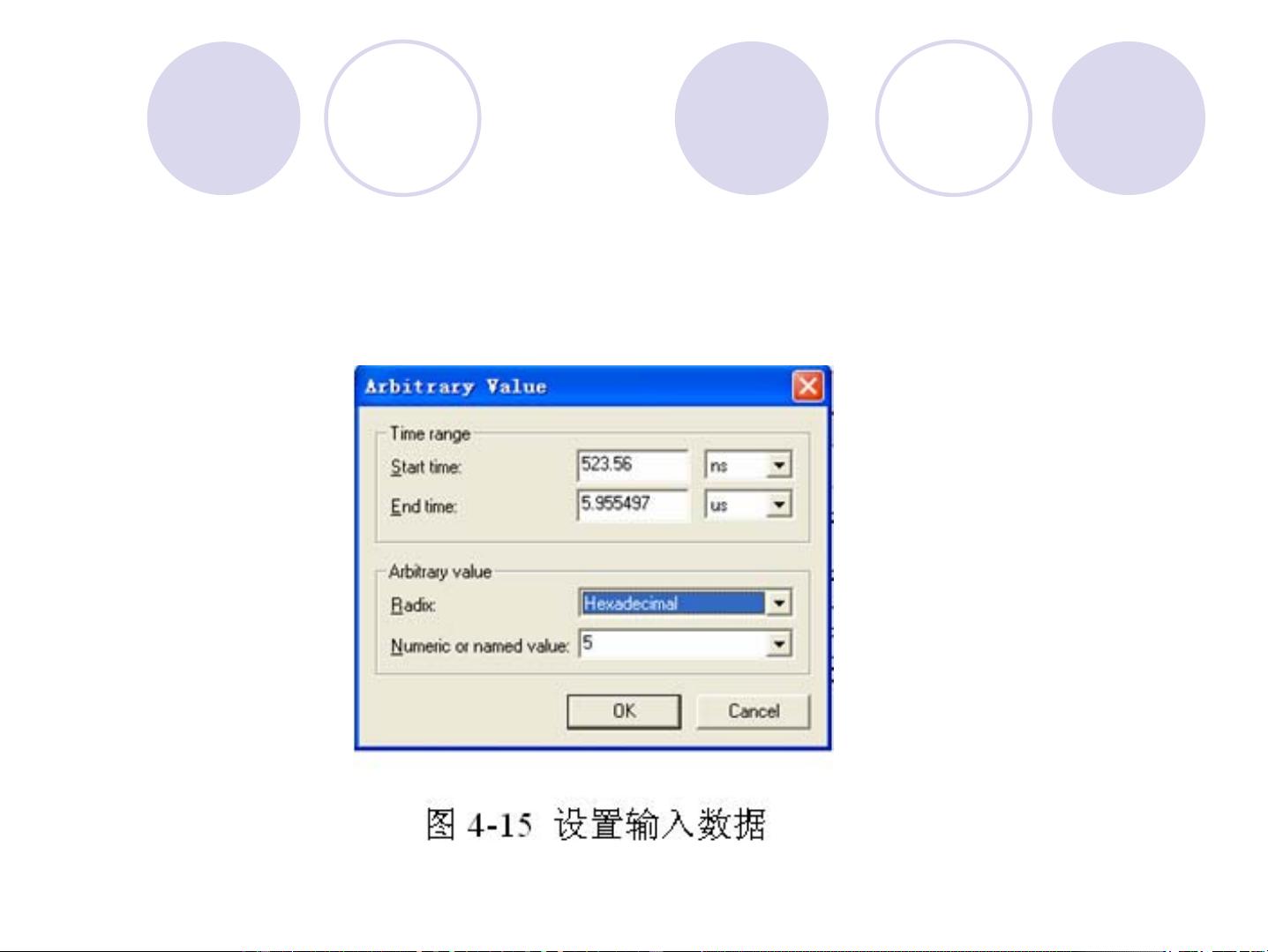

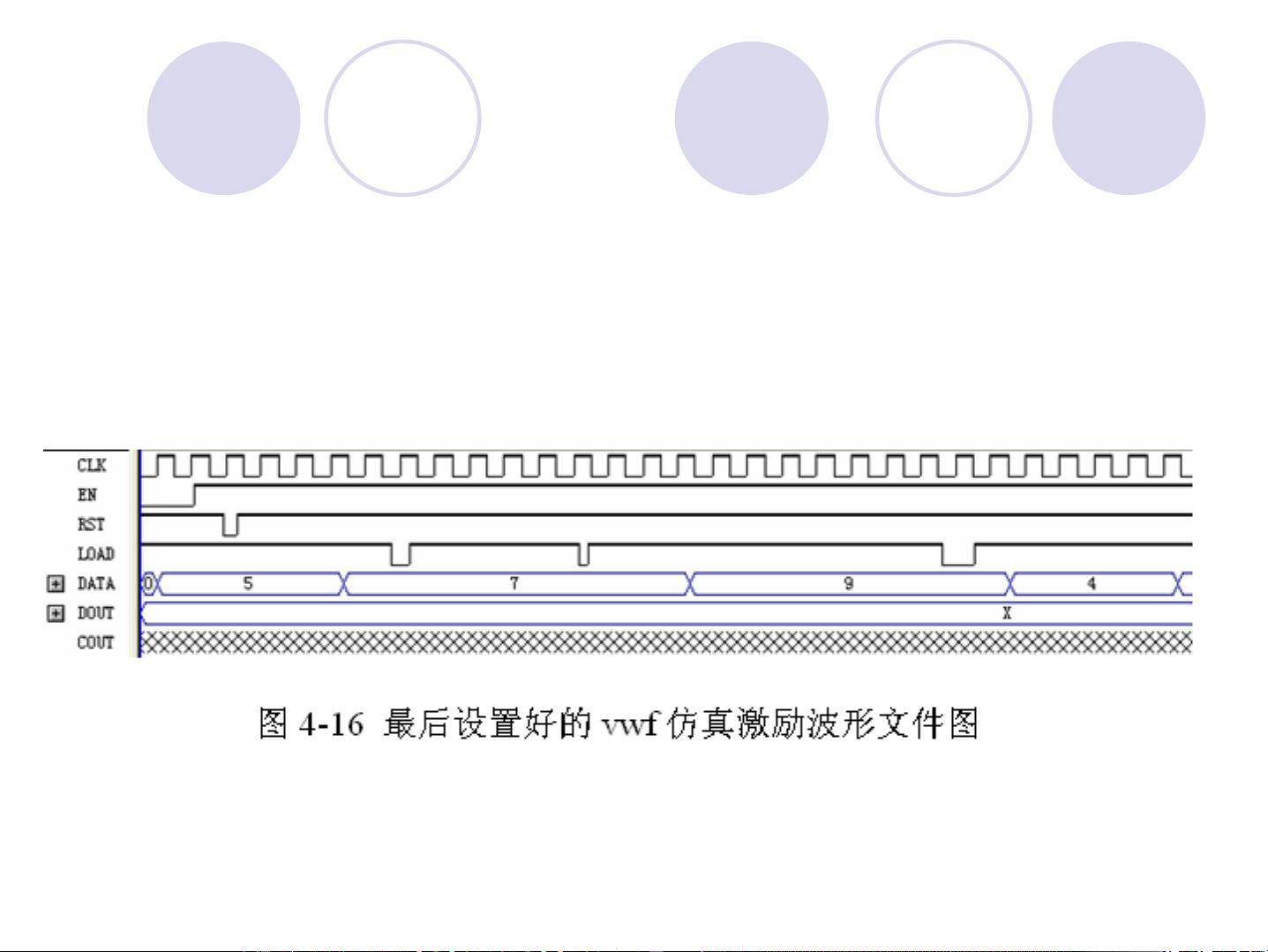

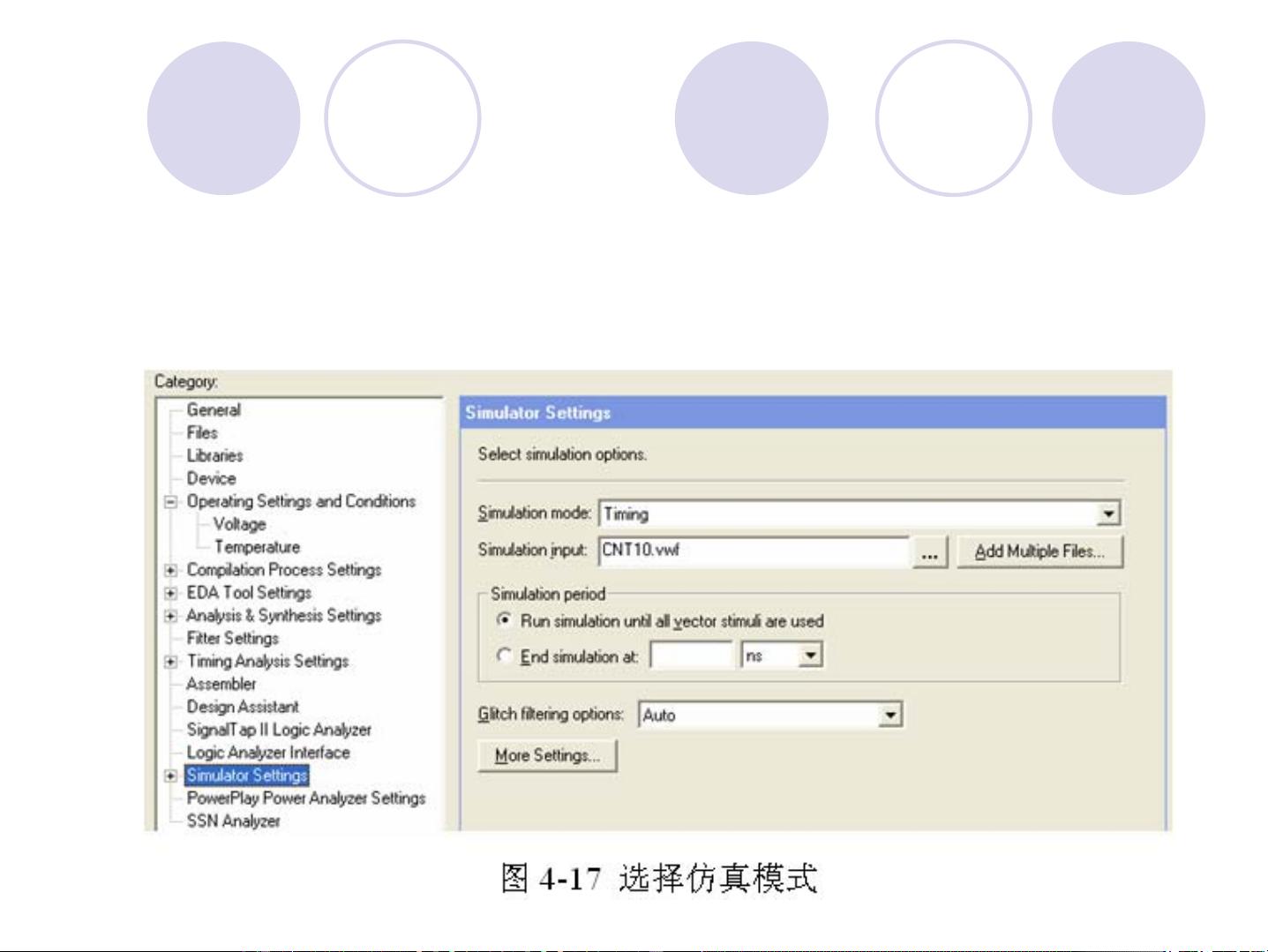

之后,执行全程编译,这是将VHDL代码转化为硬件描述的过程,Quartus II会进行语法检查、逻辑综合、布局布线等一系列操作。编译完成后,可以通过时序仿真来验证设计的功能。时序仿真是模拟设计在实际运行中的行为,通过打开波形编辑器,设置仿真时间范围,保存波形文件,并将设计的信号节点添加到波形窗口,设定输入激励信号,设置总线数据格式和参数,最后调整仿真器参数,启动仿真并分析输出结果。

在确保设计功能正确无误后,进入硬件相关的设置。引脚锁定是将设计中的逻辑功能分配到FPGA的具体引脚,确保硬件连接正确。这一过程通常包括手动或自动分配,以及后期的引脚约束检查。完成引脚设置后,需要将编译产生的文件下载到FPGA中。这可以通过AS模式编程或者JTAG间接模式进行,前者适用于已焊接到电路板上的器件,后者则适用于开发阶段的调试。

Quartus II提供了从设计输入、编译、仿真到硬件实现的完整流程,使得FPGA开发变得更加高效和便捷。掌握这些步骤对于理解和使用Quartus II进行FPGA设计至关重要。

2021-09-30 上传

2008-09-02 上传

146 浏览量

2021-10-06 上传

2011-03-28 上传

点击了解资源详情

198 浏览量

2022-06-12 上传

2023-04-04 上传

carylu2017

- 粉丝: 0

- 资源: 12

最新资源

- 单片机智能手表仿真protues

- xUnitTestOnReplit:xUnit测试重复

- MarksToAndroid,安卓或Java.zip

- contrastive-analysis--list:实时改变数值,进行对比储存列表里面的数据

- 医疗图标 .fig .xd .sketch .svg素材下载

- AD7708_C51,c语言的源码可以跨平台吗,c语言

- vuebersicht:用电子,TypeScript和Vue构建的Uebersicht的重新构想

- 易语言弹力按钮

- 确定颜色的位置 找到红色的区域 火焰识别

- BKAirMonitoringSystem

- 关于我自己

- RESTMock,.zip

- 免费开源!!Java Core Sprout:基础、并发、算法

- ericgautier_2_07012021:P2

- 【毕业设计】FPGA硬件实现触摸、显示屏控制系统(电路图、源代码、毕业论文)-电路方案

- container-ps:显示所有码头工人图像的小应用程序