没有合适的资源?快使用搜索试试~ 我知道了~

首页iPad Air 2 电路设计详解

iPad Air 2 电路设计详解

需积分: 50 15 下载量 154 浏览量

更新于2024-07-16

1

收藏 2.41MB PDF 举报

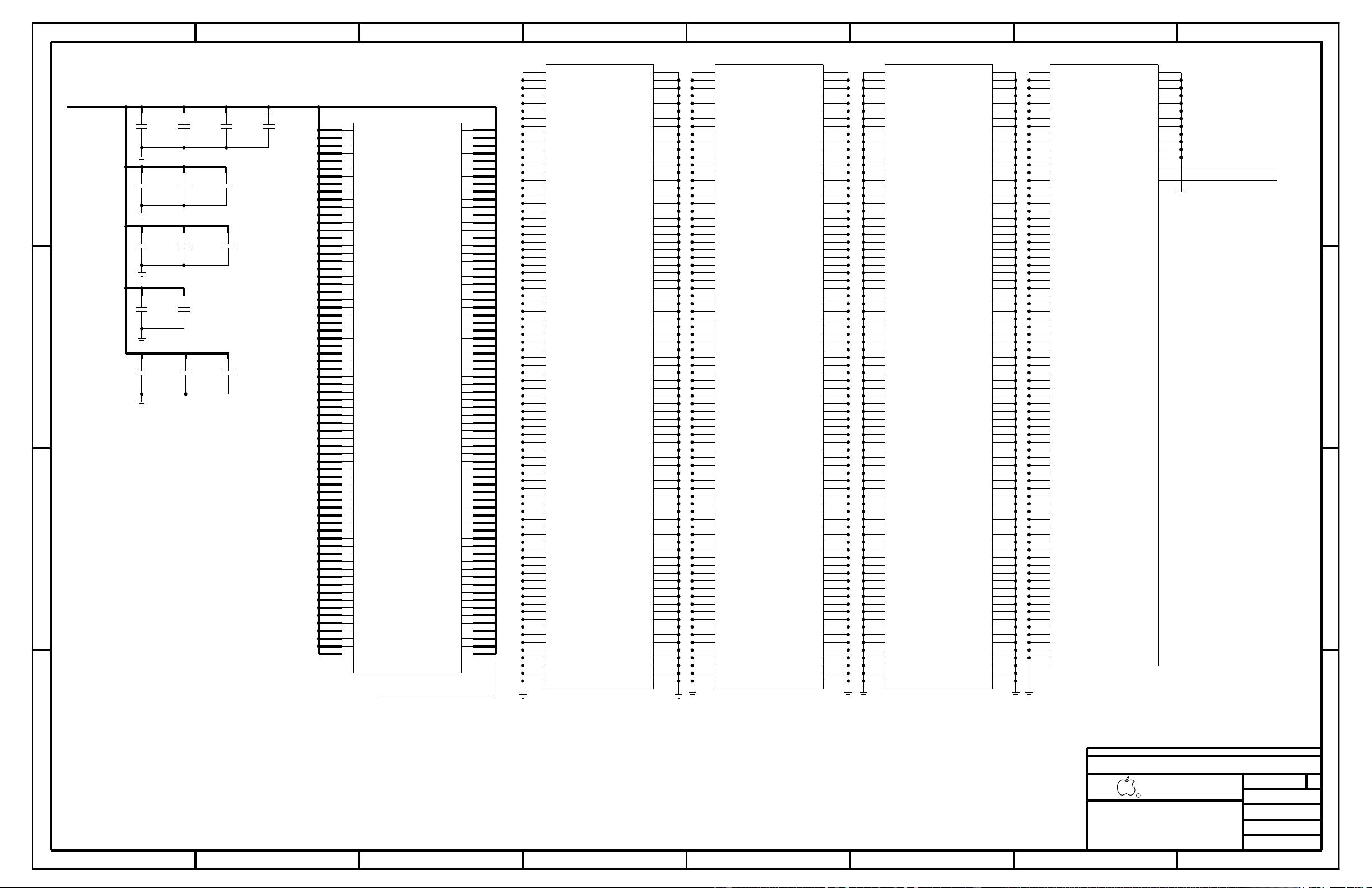

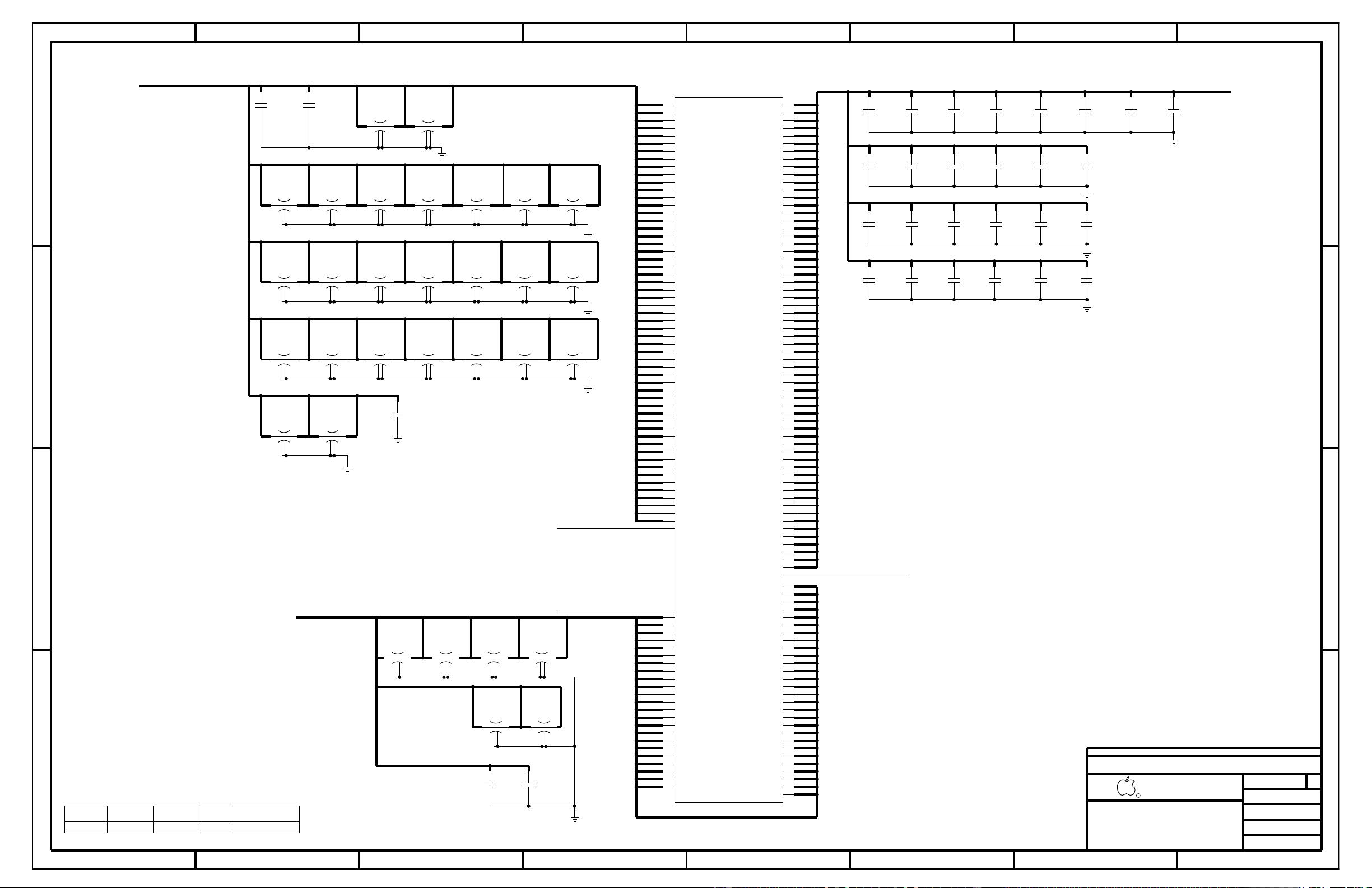

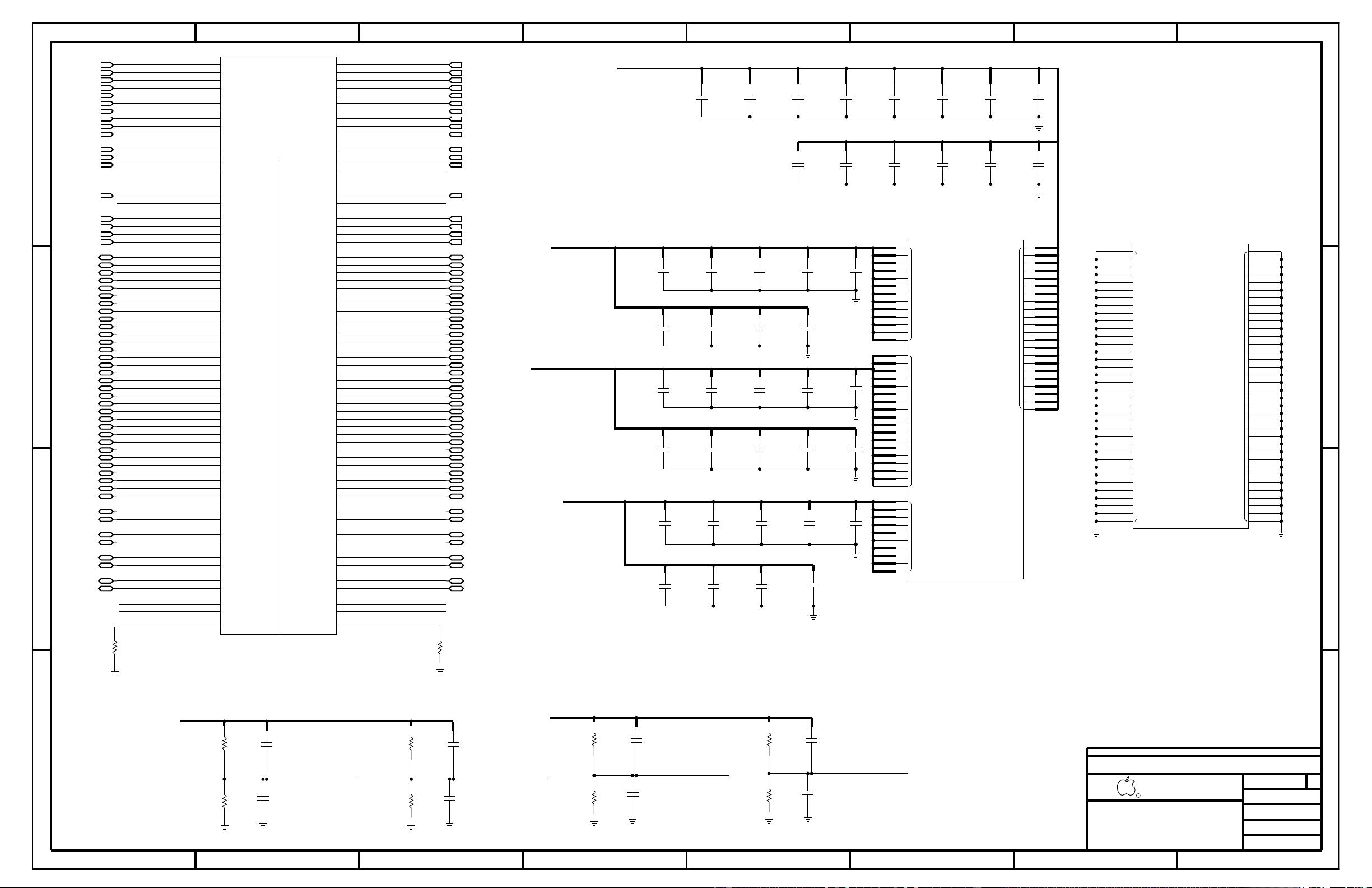

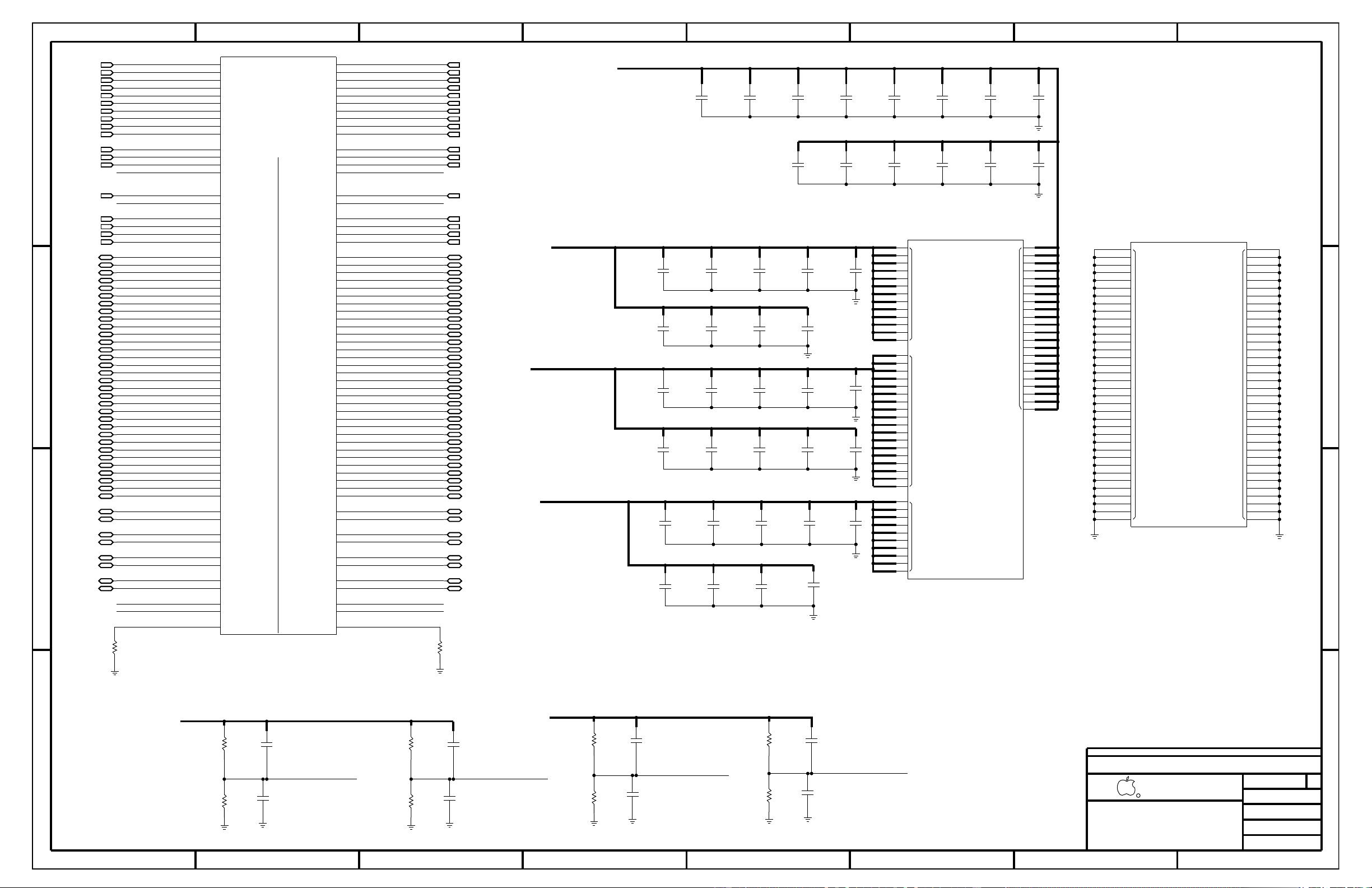

"ipad air2 电路原理图.pdf" 是一份详细展示苹果iPad Air 2内部电子结构的文档,不包含点位图和印刷电路板的图像。这份文档主要由表格和图表组成,用于列出各个组件、描述其功能、数量以及在电路板上的位置。

在电路设计中,原理图是至关重要的,它提供了设备内部所有电子元件的连接和工作方式的视觉表示。iPad Air 2的电路原理图会详细列出每一部分的元件,包括但不限于处理器、内存、显示驱动器、电源管理单元、无线通信模块等,并通过电路图符号表示它们之间的电气连接。

表格(TABLE_TABLEOFCONTENTS)部分可能包含以下内容:

1. **目录**:文档的结构和章节列表,帮助读者快速定位到特定部分,如电池管理、音频处理、传感器、无线通讯等章节。

2. **部件清单(BOM - Bill of Materials)**:详列了所有使用的电子元件,包括部件编号(PART#)、描述(DESCRIPTION)、数量(QTY)以及在电路板上的参考标识符(REFERENCEDESIGNATOR(S))。这对于维修、升级或分析设备性能至关重要。

3. **关键组件(CRITICAL)**:可能会标记出电路中的一些关键或敏感部件,这些部件对设备的整体功能或安全性有重大影响。

电路原理图中的每个元件都有一个参考设计ator,例如R1、C2、U3等,这在实际电路板上用于标识元件的位置。通过参考设计ator,技术人员可以理解每个元件如何与其它元件交互,以及如何解决可能出现的故障。

在iPad Air 2的电路设计中,我们可以预见到一些高级技术的应用,例如:

- **A8X芯片**:作为核心处理器,提供高性能计算能力。

- **M8协处理器**:负责运动数据的处理,如加速度计和陀螺仪的数据。

- **Retina显示屏**:高分辨率的显示技术,需要复杂的驱动电路。

- **Wi-Fi和蓝牙模块**:实现无线连接功能。

- **电源管理系统**:高效地管理电池的充放电,确保设备长时间运行。

- **音频编解码器**:处理声音输入和输出,确保高质量的音效体验。

- **各种传感器**:如环境光传感器、接近传感器、指纹识别传感器等,提供智能交互和安全保护。

了解这份电路原理图可以帮助电子工程师、维修技术人员和爱好者深入理解iPad Air 2的工作原理,进行故障排查、硬件升级或者定制化改造。不过,由于这份文档不含点位图,实际的电路板布局和元件位置无法直观看到,因此在实际操作时还需要结合其他参考资料。

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC

VDD_SOC_SENSE

SYM 10 OF 15

SYM 12 OF 15

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SYM 13 OF 15

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SYM 14 OF 15

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_CPU_SENSE

VSS_SENSE

SYM 15 OF 15

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

(VDD_SOC, 0.904V - 0.996V, 4.0A MAX, SOC PD PARTITIONS)

CRITICAL

4.3UF

X5R-CERM

4V

20%

0610

CRITICAL

4.3UF

X5R-CERM

4V

20%

0610

CRITICAL

4.3UF

X5R-CERM

4V

20%

0610

CRITICAL

4.3UF

X5R-CERM

4V

20%

0610

CRITICAL

1.0UF

X5R

6.3V

20%

0201-1

CRITICAL

1.0UF

X5R

6.3V

20%

0201-1

CRITICAL

1.0UF

X5R

6.3V

20%

0201-1

CRITICAL

1.0UF

X5R

6.3V

20%

0201-1

CRITICAL

1.0UF

X5R

6.3V

20%

0201-1

CRITICAL

1.0UF

X5R

6.3V

20%

0201-1

CRITICAL

0.47UF

201

CERM-X5R-1

4V

20%

CRITICAL

0.47UF

201

CERM-X5R-1

4V

20%

0.22UF

X5R

6.3V

20%

01005-1

0.22UF

X5R

6.3V

20%

01005-1

100PF

NP0-C0G

01005

5%

16V

OMIT_TABLE

TMKP88A0-N

FCBGA

OMIT_TABLE

TMKP88A0-N

FCBGA

OMIT_TABLE

TMKP88A0-N

FCBGA

OMIT_TABLE

TMKP88A0-N

FCBGA

OMIT_TABLE

TMKP88A0-N

FCBGA

SOC: SOC POWER AND GND

SYNC_DATE=N/A

SYNC_MASTER=N/A

PPVDD_SOC_SOC_SENSE

VOLTAGE=0.95V

TP_SOC_VSS_CPU_SENSE

TP_SOC_VSS_SENSE

=PP0V95_SOC

C1308

1

2

C1307

1

2

C1306

1

2

C1305

1

2

C1325

1

2

C1324

1

2

C1323

1

2

C1322

1

2

C1321

1

2

C1320

1

2

C1331

1

2

C1330

1

2

C1341

1

2

C1340

1

2

C1345

1

2

U0600

AL10

AL14

T9

M21

M23

M27

AB19

M29

M31

M33

M9

N10

N12

U10

N14

N16

N18

N20

AB21

N22

P11

P13

P15

P17

U12

P19

P21

P23

P9

R10

AB23

R12

R14

R16

R18

U14

R20

R22

T11

T13

T15

T17

L29

M28

U16

U18

AC20

U20

U22

V11

AL18

V13

V15

V17

V21

V23

V9

W10

AC22

W12

W14

AA10

W16

W20

W22

Y11

Y13

Y15

Y17

Y19

AD17

Y21

AA12

Y23

Y34

Y9

AD19

AD21

AD23

AD34

AE18

AE20

AA14

AC18

AE22

AF23

AH23

AH34

AK23

AL24

AL26

AL28

AL30

AL32

T19

AA16

J10

J12

J14

J16

J18

J20

J22

J24

J32

T21

K11

AA20

K13

K15

K17

K19

K21

K23

K25

K31

T23

K33

K9

AA22

L10

L12

L14

L16

L18

L20

L22

T34

L24

L26

L30

AB17

L32

M11

M13

M15

M17

M19

M25

U0600

A1

A21

A34

AF20

AF22

AF24

AF26

AF28

AF30

AF32

AF34

AF8

AG21

A39

AG23

AG25

AG27

AG29

AG3

AG31

AG33

AG35

AG9

AH10

A41

AH14

AH16

AH18

AH2

AH20

AH22

AH24

AH26

AH28

AH30

AA11

AH32

AH37

AH40

AH5

AH8

AJ11

AJ13

AJ17

AJ19

AJ21

AA13

AJ23

AJ25

AJ27

AJ29

AJ3

AJ31

AJ33

AJ35

AJ6

AJ7

AA15

AJ9

AK1

AK12

AK16

AK18

AK2

AK22

AK24

AK26

AK28

AA17

AA19

AA21

AA23

A22

AA25

AA27

AA29

AA31

AA33

AA35

AA9

AB1

AB10

AB12

A24

AB14

AB16

AB18

AB2

AB20

AB22

AB24

AB26

AB28

AB3

A26

AB30

AB32

AB34

AB37

AB40

AB8

AC1

AC11

Y5

AC17

A27

AC19

AC2

AC21

AC23

AC25

AC27

AC29

AC3

AC31

AC33

A29

AC35

AC7

AC9

AD1

AD10

AD12

AD16

AD18

AD2

AD20

A3

AD22

AD24

AD26

AD28

AD3

AD30

AD32

AD4

AD5

AD6

A31

AD8

AE11

AE13

AE17

AE19

AE21

AE23

AE25

AE27

AE29

A33

AE31

AE33

AE35

AE37

AE40

AE7

AE9

AF10

AF12

AF14

U0600

AK3

AK30

AK32

AK34

AK4

AK5

AK6

AK8

AL11

AL13

AL17

AL19

AL21

AL23

AL25

AL27

AL29

AL3

AL31

AL33

AL37

AL40

AL9

AM10

AM12

AM14

AM16

AM18

AM2

AM20

AM22

AM24

AM30

AM32

AM34

AM5

AM8

AN11

AN13

AN17

AN19

AN21

AN23

AN25

AN27

AN29

AN3

AN31

AN6

AN7

AP11

AP12

AP13

AP18

AP20

AP21

AP22

AP23

AP25

AP26

AP28

AP37

AP40

AR10

AR12

AR14

AR18

AR21

AR22

AR25

AR26

AR27

AR33

AR36

AT12

AT2

AT22

AT28

AT3

AT5

AT6

AU1

AU10

AU12

AU15

AU17

AU21

AU23

AU27

AU28

AU29

AU3

AU30

AU31

AU32

AU33

AU34

AU35

AU36

AU37

AU39

AU41

AU6

AU8

AU9

AV11

AV15

AV18

AV2

AV20

AV24

AV26

AV28

AV34

AV40

AV7

AV9

AW1

AW28

AW3

AW34

AW39

AW41

AW9

B11

B13

B17

B19

B2

B21

B27

B34

B36

B4

B40

B6

C1

C10

C14

C16

C20

C21

C23

C25

C27

C28

C30

C32

C34

C4

C41

C5

C7

D11

D21

D22

D24

D26

D27

D29

U0600

D31

D33

D34

D37

E11

E12

E15

E16

E17

E22

E24

E26

E27

E34

E4

E7

F11

F12

F14

F15

F16

F19

F26

F27

F28

F3

F30

F32

F34

F38

F40

F5

F6

F8

G11

G13

G15

G17

G19

G21

G22

G24

G25

G31

G32

G33

G34

G6

G7

H12

H14

H16

H18

H20

H26

H27

H28

H30

H4

H6

H8

J11

J13

J15

J17

J19

J29

J3

J30

J33

J5

J6

J7

J9

K1

K10

K12

K14

K16

K18

K2

K20

K22

K24

K26

K28

K3

K32

K37

K4

K40

K5

K6

K8

L11

L13

L15

L17

L19

L21

L23

L25

L31

L33

L4

L5

L7

L9

M10

M12

M14

M16

M18

M20

M22

M24

Y8

M30

M4

M5

M8

N11

N13

N15

N17

N19

N21

N23

N27

N29

N3

N31

N33

N35

N37

N40

N7

N9

P10

P12

P14

P16

P18

P2

P20

P22

P24

P26

P28

P30

P32

P8

R11

R13

R15

R17

R19

R21

R23

R25

U0600

R27

R29

R3

R31

R33

R35

R9

T1

T10

T12

T14

T16

T18

T2

T20

T22

T24

T26

T28

T3

T30

T32

T37

T40

T5

T8

U11

U13

U15

U17

U21

U23

U25

U27

U29

U3

U31

U33

U35

U6

U7

U9

V10

V12

V14

V16

V2

V20

V22

V24

V26

V28

V30

V32

V34

V4

V5

V6

V8

W11

W13

W15

W17

W19

W21

W23

W25

W27

W29

W3

W31

W33

W35

W37

W40

W6

W7

W9

Y10

Y12

Y14

Y16

Y20

Y22

Y24

Y26

Y28

Y30

Y32

AC13

M26

051-0301

B.0.0

13 OF 155

12 OF 73

62 70

70

70

72

SYM 9 OF 15

VDD_CPU

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_CPU

VDD_GPU

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_CPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_CPU

VDD_CPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_CPU

VDD_GPU

VDD_GPU

VDD_GPU

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_SRAM

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU_SENSE

VDD_SRAM_SENSE

VDD_SRAM

VDD_GPU_SENSE

VDD_CPU

VDD_CPU

VDD_CPU

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

TABLE_ALT_ITEM

(VDD_GPU 0.80V - 1.05V, 8.0A MAX, GPU LOGIC)

(VDD_SRAM 0.95V - 1.05V, 3.4A MAX, CPU AND GPU SRAM)

(VDD_CPU 0.775V - 1.05V, 13.4A MAX, CPU0-2 AND CPUB)

4V

CERM

15UF

0402

20%

4V

CERM

15UF

0402

20%

4V

CERM

15UF

0402

20%

CRITICAL

4.3UF

0610

X5R-CERM

4V

20%

CRITICAL

4.3UF

0610

X5R-CERM

4V

20%

CRITICAL

4.3UF

0610

X5R-CERM

4V

20%

CRITICAL

4.3UF

0610

X5R-CERM

4V

20%

CRITICAL

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

4.3UF

0610

X5R-CERM

4V

20%

CRITICAL

4.3UF

0610

X5R-CERM

4V

20%

4V

CERM

15UF

0402

20%

CRITICAL

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

1.0UF

0201-1

X5R

6.3V

20%

0.22UF

01005-1

X5R

6.3V

20%

0.22UF

01005-1

X5R

6.3V

20%

0.22UF

01005-1

X5R

6.3V

20%

0.22UF

01005-1

X5R

6.3V

20%

CRITICAL

0.47UF

0204

X5R

6.3V

20%

CRITICAL

0.47UF

0204

X5R

6.3V

20%

CRITICAL

0.47UF

0204

X5R

6.3V

20%

CRITICAL

0.47UF

0204

X5R

6.3V

20%

CRITICAL

0.47UF

0204

X5R

6.3V

20%

CRITICAL

0.47UF

0204

X5R

6.3V

20%

CRITICAL

7.5UF

CERM

4V

0402

20%

CRITICAL

4.3UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

7.5UF

CERM

4V

0402

20%

CRITICAL

4.3UF

CERM

4V

0402

20%

CRITICAL

4.3UF

CERM

4V

0402

20%

CRITICAL

4.3UF

CERM

4V

0402

20%

CRITICAL

4.3UF

CERM

4V

0402

20%

CRITICAL

4.3UF

CERM

4V

0402

20%

CRITICAL

4.3UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

100PF

01005

NP0-C0G

5%

16V

100PF

01005

NP0-C0G

5%

16V

OMIT_TABLE

TMKP88A0-N

FCBGA

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

0402

20%

4V

CRITICAL

7.5UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

7.5UF

CERM

4V

0402

20%

CRITICAL

1UF

CERM

4V

0402

20%

CRITICAL

4.3UF

CERM

4V

0402

20%

CRITICAL

4.3UF

CERM

4V

0402

20%

56PF

5%

01005

NP0-C0G

6.3V

220PF

01005

10V

10%

X7R-CERM

SOC: CPU, GPU, SRAM POWER

SYNC_DATE=N/A

SYNC_MASTER=N/A

?

C1410, ECT

RDAR://PROBLEM/16040051

138S00006

138S0835

PPVDD_CPU_SOC_SENSE

VOLTAGE=1.1V

PPVDD_SRAM_SOC_SENSE

VOLTAGE=3.3V

PPVDD_GPU_SOC_SENSE

VOLTAGE=1.1V

=PPVDD_GPU

=PPVDD_CPU

=PPVDD_SRAM

C1400

1

2

C1401

1

2

C1460

1

2

C1469

1

2

C1468

1

2

C1467

1

2

C1466

1

2

C1475

1

2

C1474

1

2

C1465

1

2

C1464

1

2

C1461

1

2

C1473

1

2

C1472

1

2

C1471

1

2

C1470

1

2

C1493

1

2

C1492

1

2

C1491

1

2

C1490

1

2

C1480

1

2

C1481

1

2

C1482

1

2

C1483

1

2

C1484

1

2

C1485

1

2

C1405

1

2

3

4

C1411

1

2

3

4

C1420

1

2

3

4

C1406

1

2

3

4

C1412

1

2

3

4

C1413

1

2

3

4

C1414

1

2

3

4

C1415

1

2

3

4

C1416

1

2

3

4

C1410

1

2

3

4

C1421

1

2

3

4

C1422

1

2

3

4

C1423

1

2

3

4

C1424

1

2

3

4

C1425

1

2

3

4

C1426

1

2

3

4

C1495

1

2

C1459

1

2

U0600

AB11

AD15

AF19

AB15

AF21

AF9

AG10

AG12

AG14

AG17

AG20

AG22

AD9

AG8

AH11

AB9

AH13

AH15

AH17

AH19

AH21

AH9

AJ10

AE10

AJ12

AJ14

AJ16

AC12

AJ18

AJ20

AJ22

AJ8

AK11

AK13

AE14

AK15

AK17

AK19

AK21

AC14

AK9

AL12

AL16

AL20

AL22

AE16

AL8

AC16

AC8

AD11

AD13

AE8

AF13

AF15

AF17

AB13

AA26

AA28

AF25

AF29

AA32

AF31

AG26

AG28

AG32

AG34

AH25

AH29

AC34

AH31

AJ26

AJ28

AA34

AJ32

AJ34

AK25

AK29

AK31

N28

AD25

N32

P25

P29

AB25

P31

R26

R28

R32

R34

T25

AD29

T29

T31

U26

U28

AB29

U32

U34

V25

V29

V31

AD31

W26

W28

W32

W34

Y25

AB31

Y29

Y31

AC26

AC28

AE26

AC32

AE28

AE32

AE34

N26

AA24

AA30

AD33

AE15

AE24

AE30

AF11

AF27

AF33

AG11

AG13

AG15

AB27

AG16

AG19

AG24

AG30

AH27

AH33

AJ15

AJ24

AJ30

AK10

AB33 AK14

AK20

AK27

AK33

AL15

N24

N30

P27

P33

R24

AC10

R30

T27

T33

U24

U30

V27

V33

W24

W30

Y27

AC15

Y33

AC24

AC30

AD14

AD27

N25

C1436

1

2

3

4

C1435

1

2

3

4

C1434

1

2

3

4

C1433

1

2

3

4

C1432

1

2

3

4

C1431

1

2

3

4

C1430

1

2

3

4

C1438

1

2

3

4

C1437

1

2

3

4

C1451

1

2

3

4

C1455

1

2

3

4

C1457

1

2

C1452

1

2

3

4

C1456

1

2

3

4

C1454

1

2

3

4

C1453

1

2

3

4

C1496

1

2

C1439

1

2

14 OF 155

B.0.0

051-0301

13 OF 73

62 70

62 70

62 70

72

72

72

IN

IN

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

DDR0

DDR1

(1 OF 3)

DDR1_ZQ

DDR1_VREF_DQ

DDR1_VREF_CA

DDR1_PDQS[3]

DDR1_PDQS[2]

DDR1_PDQS[1]

DDR1_PDQS[0]

DDR1_NDQS[3]

DDR1_NDQS[2]

DDR1_NDQS[1]

DDR1_NDQS[0]

DDR1_DQ[9]

DDR1_DQ[8]

DDR1_DQ[4]

DDR1_DQ[31]

DDR1_DQ[30]

DDR1_DQ[3]

DDR1_DQ[29]

DDR1_DQ[28]

DDR1_DQ[27]

DDR1_DQ[26]

DDR1_DQ[25]

DDR1_DQ[24]

DDR1_DQ[23]

DDR1_DQ[22]

DDR1_DQ[21]

DDR1_DQ[20]

DDR1_DQ[2]

DDR1_DQ[19]

DDR1_DQ[18]

DDR1_DQ[17]

DDR1_DQ[16]

DDR1_DQ[15]

DDR1_DQ[14]

DDR1_DQ[13]

DDR1_DQ[12]

DDR1_DQ[11]

DDR1_DQ[10]

DDR1_DQ[1]

DDR1_DQ[0]

DDR1_DM[3]

DDR1_DM[2]

DDR1_DM[1]

DDR1_DM[0]

DDR1_CS[1]

DDR1_CS[0]

DDR1_CKE[1]

DDR1_CKE[0]

DDR1_CKB

DDR1_CK

DDR1_CA[9]

DDR1_CA[8]

DDR1_CA[7]

DDR1_CA[6]

DDR1_CA[5]

DDR1_CA[4]

DDR1_CA[3]

DDR1_CA[2]

DDR1_CA[1]

DDR1_CA[0]

DDR0_ZQ

DDR0_VREF_DQ

DDR0_VREF_CA

DDR0_PDQS[3]

DDR0_PDQS[2]

DDR0_PDQS[1]

DDR0_PDQS[0]

DDR0_NDQS[3]

DDR0_NDQS[2]

DDR0_NDQS[1]

DDR0_NDQS[0]

DDR0_DQ[9]

DDR0_DQ[8]

DDR0_DQ[7]

DDR0_DQ[6]

DDR0_DQ[5]

DDR0_DQ[4]

DDR0_DQ[31]

DDR0_DQ[30]

DDR0_DQ[3]

DDR0_DQ[29]

DDR0_DQ[28]

DDR0_DQ[27]

DDR0_DQ[26]

DDR0_DQ[25]

DDR0_DQ[24]

DDR0_DQ[23]

DDR0_DQ[22]

DDR0_DQ[21]

DDR0_DQ[20]

DDR0_DQ[2]

DDR0_DQ[19]

DDR0_DQ[18]

DDR0_DQ[17]

DDR0_DQ[16]

DDR0_DQ[15]

DDR0_DQ[14]

DDR0_DQ[13]

DDR0_DQ[12]

DDR0_DQ[11]

DDR0_DQ[10]

DDR0_DQ[1]

DDR0_DQ[0]

DDR0_CS[1]

DDR0_CS[0]

DDR0_CKE[1]

DDR0_CKE[0]

DDR0_CKB

DDR0_CK

DDR0_CA[9]

DDR0_CA[8]

DDR0_CA[7]

DDR0_CA[6]

DDR0_CA[5]

DDR0_CA[4]

DDR0_CA[3]

DDR0_CA[2]

DDR0_CA[1]

DDR0_CA[0]

DDR0_DM[0]

DDR0_DM[1]

DDR0_DM[2]

DDR0_DM[3]

DDR1_DQ[5]

DDR1_DQ[6]

DDR1_DQ[7]

(2 OF 3)

VDDQ

VDDCA

VDD2

VDD1

(3 OF 3)

VSSVSS

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

SEG: OK TO FLOAT CKE AND CS PINSSEG: OK TO FLOAT CKE AND CS PINS

POR CAPS 6/11/2013

DDR0 AND DDR1 WERE SWAPPED INTENTIONALLY FOR ROUTING

1UF

402

10%

CERM

6.3V

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

1UF

402

CERM

10%

6.3V

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

CRITICAL

4V

CERM

15UF

0402

20%

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

1UF

402

10%

CERM

6.3V

1UF

402

10%

CERM

6.3V

CRITICAL

4.3UF

X5R-CERM

0610

4V

20%

CRITICAL

4V

CERM

15UF

0402

20%

1.0UF

0201-1

X5R

6.3V

20%

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

4V

CERM

15UF

0402

20%

0.1UF

X5R-CERM

01005

6.3V

20%

1.0UF

0201-1

X5R

6.3V

20%

1.0UF

0201-1

X5R

6.3V

20%

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

4V

CERM

15UF

0402

20%

CRITICAL

4.3UF

X5R-CERM

0610

4V

20%

0.1UF

X5R-CERM

01005

6.3V

20%

0.47UF

CERM-X5R-1

201

4V

20%

0.47UF

CERM-X5R-1

201

4V

20%

0.1UF

X5R-CERM

01005

6.3V

20%

0.1UF

X5R-CERM

01005

6.3V

20%

CRITICAL

4.3UF

0610

X5R-CERM

4V

20%

1.0UF

0201-1

X5R

6.3V

20%

0.1UF

X5R-CERM

01005

6.3V

20%

0.1UF

X5R-CERM

01005

6.3V

20%

0.1UF

X5R-CERM

01005

6.3V

20%

0.1UF

01005

X5R-CERM

6.3V

20%

OMIT_TABLE

CAPRI-DRAM

BGA-1

DRAM

OMIT_TABLE

CAPRI-DRAM

DRAM

BGA-1

OMIT_TABLE

CAPRI-DRAM

BGA-1

DRAM

100PF

NP0-C0G

5%

16V

01005

100PF

01005

16V

5%

NP0-C0G

100PF

01005

16V

5%

NP0-C0G

100PF

01005

NP0-C0G

5%

16V

100PF

25V

5%

C0G

0201

100PF

0201

C0G

5%

25V

100PF

0201

C0G

5%

25V

1.0UF

0201-1

X5R

6.3V

20%

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

4.3UF

X5R-CERM

0610

4V

20%

1UF

402

CERM

10%

6.3V

1UF

402

CERM

10%

6.3V

1.0UF

0201-1

X5R

6.3V

20%

1.0UF

0201-1

X5R

6.3V

20%

CRITICAL

4V

CERM

15UF

0402

20%

240

01005

MF

1%

1/32W

0.1UF

01005

X5R-CERM

6.3V

20%

0.1UF

01005

X5R-CERM

6.3V

20%

10K

1%

MF

01005

1/32W

10K

1/32W

MF

01005

1%

240

01005

1/32W

1%

MF

0.1UF

01005

X5R-CERM

6.3V

20%

0.1UF

01005

X5R-CERM

6.3V

20%

10K

MF

1%

01005

1/32W

10K

01005

MF

1%

1/32W

0.1UF

01005

X5R-CERM

6.3V

20%

0.1UF

01005

X5R-CERM

6.3V

20%

0.1UF

X5R-CERM

01005

6.3V

20%

4.7K

1%

1/32W

MF

01005

4.7K

01005

MF

1/32W

1%

4.7K

1%

1/32W

01005

MF

0.1UF

01005

X5R-CERM

6.3V

20%

4.7K

01005

MF

1%

1/32W

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

DDR: CHANNEL 0 AND 1

SYNC_DATE=N/A

SYNC_MASTER=N/A

DDR0_DQ<4>

DDR1_DQ<27>

DDR1_DQ<28>

DDR1_DM<1>

DDR1_DM<0>

DDR1_CSN<0>

DDR1_CKE<0>

DDR1_CA<9>

DDR1_CA<8>

DDR1_CA<7>

DDR1_CA<6>

DDR1_CA<5>

DDR1_CA<4>

DDR1_CA<3>

DDR1_CA<2>

DDR1_CA<1>

DDR1_CA<0>

DDR0_DQS_N<3>

DDR0_DQS_P<3>

DDR0_DQS_P<2>

DDR0_DQS_N<2>

DDR0_DQS_P<1>

DDR0_DQS_N<1>

DDR0_DQS_N<0>

DDR0_DQS_P<0>

DDR0_DQ<31>

DDR0_DQ<30>

DDR0_DQ<29>

DDR0_DQ<28>

DDR0_DQ<26>

DDR0_DQ<27>

DDR0_DQ<25>

DDR0_DQ<24>

DDR0_DQ<23>

DDR0_DQ<21>

DDR0_DQ<22>

DDR0_DQ<20>

DDR0_DQ<19>

DDR0_DQ<18>

DDR0_DQ<16>

DDR0_DQ<17>

DDR0_DQ<15>

DDR0_DQ<14>

DDR0_DQ<13>

DDR0_DQ<12>

DDR0_DQ<11>

DDR0_DQ<10>

DDR0_DQ<8>

DDR0_DQ<9>

DDR0_DQ<7>

DDR0_DQ<6>

DDR0_DQ<5>

DDR0_DQ<3>

DDR0_DQ<2>

DDR0_DQ<1>

DDR0_DQ<0>

DDR0_DM<3>

DDR0_DM<2>

DDR0_DM<1>

DDR0_DM<0>

DDR0_CSN<0>

DDR0_CKE<0>

DDR0_CK_N

DDR0_CK_P

DDR0_CA<8>

DDR0_CA<9>

DDR0_CA<7>

DDR0_CA<5>

DDR0_CA<6>

DDR0_CA<4>

DDR0_CA<3>

DDR0_CA<2>

DDR0_CA<0>

DDR0_CA<1>

DDR1_CK_N

DDR1_CK_P

DDR1_DQS_N<3>

DDR1_DQS_N<2>

DDR1_DQS_N<1>

DDR1_DQS_N<0>

DDR1_DQS_P<3>

DDR1_DQS_P<2>

DDR1_DQS_P<1>

DDR1_DQS_P<0>

DDR1_DQ<31>

DDR1_DQ<30>

DDR1_DQ<29>

DDR1_DQ<26>

DDR1_DQ<25>

DDR1_DQ<24>

DDR1_DQ<23>

DDR1_DQ<22>

DDR1_DQ<21>

DDR1_DQ<20>

DDR1_DQ<19>

DDR1_DQ<18>

DDR1_DQ<17>

DDR1_DQ<16>

DDR1_DQ<15>

DDR1_DQ<14>

DDR1_DQ<13>

DDR1_DQ<12>

DDR1_DQ<11>

DDR1_DQ<10>

DDR1_DQ<9>

DDR1_DQ<8>

DDR1_DQ<7>

DDR1_DQ<6>

DDR1_DQ<5>

DDR1_DQ<4>

DDR1_DQ<3>

DDR1_DQ<2>

DDR1_DQ<1>

DDR1_DQ<0>

DDR1_DM<3>

DDR1_DM<2>

=PP1V2_S2R_DDR

=PP1V8_S2R_DDR

=PP1V2_DDR_VDDQ

DDR0_ZQ_DRAM

PPVREF_DDR0_CA_DRAM

VOLTAGE=0.6V

=PP1V2_DDR_VDDQ

=PP1V2_S2R_DDR

PPVREF_DDR0_DQ_DRAM

PPVREF_DDR0_CA_DRAM

NO_TEST=TRUE

NC_DRAM_DDR0_CKE<1>

NO_TEST=TRUE

NC_DDR0_CS<1>

NO_TEST=TRUE

NC_DDR1_CS<1>

PPVREF_DDR1_CA_DRAM

PPVREF_DDR1_DQ_DRAM

DDR1_ZQ_DRAM

PPVREF_DDR1_CA_DRAM

VOLTAGE=0.6V

PPVREF_DDR0_DQ_DRAM

VOLTAGE=0.6V

NO_TEST=TRUE

NC_DRAM_DDR1_CKE<1>

=PP1V2_S2R_DDR

PPVREF_DDR1_DQ_DRAM

VOLTAGE=0.6V

C1626

1

2

C1625

1

2

C1620

1

2

C1607

1

2

C1606

1

2

C1605

1

2

C1603

1

2

C1666

1

2

C1665

1

2

C1669

1

2

C1668

1

2

C1660

1

2

R1699

1

2

C1696

1

2

C1697

1

2

R1696

1

2

R1697

1

2

R1698

1

2

C1694

1

2

C1695

1

2

R1694

1

2

R1695

1

2

C1692

1

2

C1693

1

2

C1690

1

2

R1692

1

2

R1693

1

2

R1690

1

2

C1691

1

2

R1691

1

2

C1646

1

2

C1645

1

2

C1642

1

2

C1640

1

2

C1628

1

2

C1629

1

2

C1600

1

2

C1616

1

2

C1608

1

2

C1649

1

2

C1648

1

2

C1601

1

2

C1602

1

2

C1615

1

2

C1611

1

2

C1610

1

2

C1656

1

2

C1655

1

2

C1643

1

2

C1676

1

2

C1675

1

2

C1636

1

2

C1635

1

2

U1600

H18

H19

J18

J19

K19

R18

R19

T19

T20

U18

M19

N19

L19

L18

L20

K20

L3

N2

G2

T4

H3

H4

R2

R3

R4

R5

T2

T3

E2

E3

E4

E5

J2

F2

F4

F5

G5

U2

V2

V3

V4

W2

W3

J3

Y3

Y4

J4

J5

K2

K3

P3

P4

L4

N3

G4

U3

K4

N4

G3

U4

P19

M4

U19

V17

W17

V16

W16

W15

V10

W10

W9

Y9

V8

W13

W12

W14

V14

Y14

Y15

C14

B12

B18

D9

C17

D17

B10

C10

D10

E10

B9

C9

B20

C20

D20

E20

B16

B19

D19

E19

E18

B8

B7

C7

D7

B6

C6

C16

B5

C5

D16

E16

B15

C15

C11

D11

D14

C12

D18

C8

D15

D12

C18

D8

W11

D13

W8

U1600

AA19

B13

Y19

Y5

Y6

C2

C3

G19

M2

P18

V11

W20

W21

AA18

AA20

P20

V20

V21

W19

Y11

Y18

Y20

Y21

AA21

AA4

AA5

B3

B4

E13

E21

M5

H20

K18

M18

N18

T18

V12

V13

V15

V9

Y17

A10

A12

E12

E17

F1

F3

H5

J1

K1

L2

N1

N5

A15

R1

W4

A16

A19

B14

C19

C21

D4

D6

U1600

A1

A18

AA1

AA2

AA3

AA6

AA7

B1

B11

B17

B2

B21

A2

C1

C13

C4

D1

D2

D21

D3

D5

E1

E14

A20

E15

E6

E7

E9

F18

F19

F20

F21

G1

G18

A21 G20

G21

H2

J20

K5

L5

M20

M3

N20

P2

A3

R20

T5

U1

U20

V18

V19

V5

V6

V7

W1

A4

W18

W5

W6

W7

Y1

Y10

Y12

Y13

Y16

Y2

A5

Y7

Y8

A6

A8

C1639

1

2

C1659

1

2

C1679

1

2

C1619

1

2

C1609

1

2

C1674

1

2

C1634

1

2

051-0301

B.0.0

16 OF 155

14 OF 73

14 15 72

15 72

14 15 72

14

14 15 72

14 15 72

14

14 14

14

14

14

14 15 72

14

IN

IN

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

DDR0

DDR1

(1 OF 3)

DDR1_ZQ

DDR1_VREF_DQ

DDR1_VREF_CA

DDR1_PDQS[3]

DDR1_PDQS[2]

DDR1_PDQS[1]

DDR1_PDQS[0]

DDR1_NDQS[3]

DDR1_NDQS[2]

DDR1_NDQS[1]

DDR1_NDQS[0]

DDR1_DQ[9]

DDR1_DQ[8]

DDR1_DQ[4]

DDR1_DQ[31]

DDR1_DQ[30]

DDR1_DQ[3]

DDR1_DQ[29]

DDR1_DQ[28]

DDR1_DQ[27]

DDR1_DQ[26]

DDR1_DQ[25]

DDR1_DQ[24]

DDR1_DQ[23]

DDR1_DQ[22]

DDR1_DQ[21]

DDR1_DQ[20]

DDR1_DQ[2]

DDR1_DQ[19]

DDR1_DQ[18]

DDR1_DQ[17]

DDR1_DQ[16]

DDR1_DQ[15]

DDR1_DQ[14]

DDR1_DQ[13]

DDR1_DQ[12]

DDR1_DQ[11]

DDR1_DQ[10]

DDR1_DQ[1]

DDR1_DQ[0]

DDR1_DM[3]

DDR1_DM[2]

DDR1_DM[1]

DDR1_DM[0]

DDR1_CS[1]

DDR1_CS[0]

DDR1_CKE[1]

DDR1_CKE[0]

DDR1_CKB

DDR1_CK

DDR1_CA[9]

DDR1_CA[8]

DDR1_CA[7]

DDR1_CA[6]

DDR1_CA[5]

DDR1_CA[4]

DDR1_CA[3]

DDR1_CA[2]

DDR1_CA[1]

DDR1_CA[0]

DDR0_ZQ

DDR0_VREF_DQ

DDR0_VREF_CA

DDR0_PDQS[3]

DDR0_PDQS[2]

DDR0_PDQS[1]

DDR0_PDQS[0]

DDR0_NDQS[3]

DDR0_NDQS[2]

DDR0_NDQS[1]

DDR0_NDQS[0]

DDR0_DQ[9]

DDR0_DQ[8]

DDR0_DQ[7]

DDR0_DQ[6]

DDR0_DQ[5]

DDR0_DQ[4]

DDR0_DQ[31]

DDR0_DQ[30]

DDR0_DQ[3]

DDR0_DQ[29]

DDR0_DQ[28]

DDR0_DQ[27]

DDR0_DQ[26]

DDR0_DQ[25]

DDR0_DQ[24]

DDR0_DQ[23]

DDR0_DQ[22]

DDR0_DQ[21]

DDR0_DQ[20]

DDR0_DQ[2]

DDR0_DQ[19]

DDR0_DQ[18]

DDR0_DQ[17]

DDR0_DQ[16]

DDR0_DQ[15]

DDR0_DQ[14]

DDR0_DQ[13]

DDR0_DQ[12]

DDR0_DQ[11]

DDR0_DQ[10]

DDR0_DQ[1]

DDR0_DQ[0]

DDR0_CS[1]

DDR0_CS[0]

DDR0_CKE[1]

DDR0_CKE[0]

DDR0_CKB

DDR0_CK

DDR0_CA[9]

DDR0_CA[8]

DDR0_CA[7]

DDR0_CA[6]

DDR0_CA[5]

DDR0_CA[4]

DDR0_CA[3]

DDR0_CA[2]

DDR0_CA[1]

DDR0_CA[0]

DDR0_DM[0]

DDR0_DM[1]

DDR0_DM[2]

DDR0_DM[3]

DDR1_DQ[5]

DDR1_DQ[6]

DDR1_DQ[7]

(2 OF 3)

VDDQ

VDDCA

VDD2

VDD1

(3 OF 3)

VSSVSS

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

DDR2 AND DDR3 WERE SWAPPED INTENTIONALLY FOR ROUTING

SEG: OK TO FLOAT CKE AND CS PINS SEG: OK TO FLOAT CKE AND CS PINS

6.3V

1UF

CERM

10%

402

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

6.3V

1UF

10%

CERM

402

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

20%

0402

15UF

CERM

4V

CRITICAL

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

6.3V

1UF

402

CERM

10%

6.3V

1UF

10%

CERM

402

20%

4V

CRITICAL

4.3UF

X5R-CERM

0610

20%

0402

15UF

CERM

4V

CRITICAL

20%

6.3V

X5R

1.0UF

0201-1

20%

6.3V

X5R

1.0UF

0201-1

20%

0402

15UF

CERM

4V

CRITICAL

20%

6.3V

0.1UF

01005

X5R-CERM

20%

6.3V

X5R

1.0UF

0201-1

20%

6.3V

X5R

1.0UF

0201-1

20%

6.3V

X5R

1.0UF

0201-1

20%

0402

15UF

CERM

4V

CRITICAL

20%

4V

CRITICAL

4.3UF

0610

X5R-CERM

20%

6.3V

0.1UF

01005

X5R-CERM

20%

4V

0.47UF

201

CERM-X5R-1

20%

4V

0.47UF

CERM-X5R-1

201

20%

6.3V

0.1UF

01005

X5R-CERM

20%

6.3V

0.1UF

01005

X5R-CERM

20%

4V

CRITICAL

4.3UF

X5R-CERM

0610

20%

6.3V

X5R

1.0UF

0201-1

20%

6.3V

0.1UF

01005

X5R-CERM

20%

6.3V

0.1UF

01005

X5R-CERM

20%

6.3V

0.1UF

X5R-CERM

01005

20%

6.3V

0.1UF

01005

X5R-CERM

OMIT_TABLE

CAPRI-DRAM

DRAM

BGA-1

OMIT_TABLE

CAPRI-DRAM

DRAM

BGA-1

OMIT_TABLE

CAPRI-DRAM

DRAM

BGA-1

100PF

01005

NP0-C0G

5%

16V

100PF

16V

5%

NP0-C0G

01005

100PF

5%

16V

01005

NP0-C0G

100PF

NP0-C0G

5%

16V

01005

220PF

10%

10V

X7R-CERM

01005

100PF

0201

25V

5%

C0G

100PF

25V

0201

5%

C0G

20%

6.3V

X5R

1.0UF

0201-1

20%

6.3V

X5R

1.0UF

0201-1

20%

4V

CRITICAL

4.3UF

0610

X5R-CERM

6.3V

1UF

402

CERM

10%

6.3V

1UF

CERM

402

10% 20%

6.3V

X5R

1.0UF

0201-1

20%

6.3V

X5R

1.0UF

0201-1

20%

0402

15UF

CERM

4V

CRITICAL

240

1%

MF

1/32W

01005

20%

6.3V

0.1UF

X5R-CERM

01005

20%

6.3V

0.1UF

X5R-CERM

01005

10K

01005

MF

1/32W

1%

10K

1%

01005

MF

1/32W

240

MF

1%

01005

1/32W

20%

6.3V

0.1UF

01005

X5R-CERM

20%

6.3V

0.1UF

X5R-CERM

01005

10K

01005

1/32W

1%

MF

10K

1/32W

1%

MF

01005

20%

6.3V

0.1UF

X5R-CERM

01005

20%

6.3V

0.1UF

X5R-CERM

01005

20%

6.3V

0.1UF

01005

X5R-CERM

4.7K

01005

MF

1/32W

1%

4.7K

1%

1/32W

MF

01005

4.7K

1/32W

MF

1%

01005

20%

6.3V

0.1UF

X5R-CERM

01005

4.7K

1/32W

1%

MF

01005

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

10 70

DDR: CHANNEL 2 AND 3

SYNC_DATE=N/A

SYNC_MASTER=N/A

PPVREF_DDR3_DQ_DRAM

VOLTAGE=0.6V

PPVREF_DDR2_DQ_DRAM

=PP1V2_S2R_DDR

NO_TEST=TRUE

NC_DRAM_DDR3_CKE<1>

DDR2_ZQ_DRAM

PPVREF_DDR2_DQ_DRAM

VOLTAGE=0.6V

PPVREF_DDR3_CA_DRAM

PPVREF_DDR3_DQ_DRAM

NO_TEST=TRUE

NC_DDR3_CS<1>

NO_TEST=TRUE

NC_DDR2_CS<1>

NO_TEST=TRUE

NC_DRAM_DDR2_CKE<1>

PPVREF_DDR2_CA_DRAM

PPVREF_DDR2_CA_DRAM

VOLTAGE=0.6V

=PP1V2_DDR_VDDQ

DDR3_ZQ_DRAM

=PP1V2_S2R_DDR

PPVREF_DDR3_CA_DRAM

VOLTAGE=0.6V

=PP1V2_DDR_VDDQ

=PP1V8_S2R_DDR

=PP1V2_S2R_DDR

DDR2_DQS_P<3>

DDR3_DM<1>

DDR3_DM<0>

DDR3_CSN<0>

DDR3_CKE<0>

DDR3_CA<9>

DDR3_CA<8>

DDR3_CA<7>

DDR3_CA<6>

DDR3_CA<5>

DDR3_CA<4>

DDR3_CA<3>

DDR3_CA<2>

DDR3_CA<1>

DDR3_CA<0>

DDR2_DQS_N<3>

DDR2_DQS_P<2>

DDR2_DQS_N<2>

DDR2_DQS_P<1>

DDR2_DQS_N<1>

DDR2_DQS_N<0>

DDR2_DQS_P<0>

DDR2_DQ<31>

DDR2_DQ<30>

DDR2_DQ<29>

DDR2_DQ<28>

DDR2_DQ<26>

DDR2_DQ<27>

DDR2_DQ<25>

DDR2_DQ<24>

DDR2_DQ<23>

DDR2_DQ<21>

DDR2_DQ<22>

DDR2_DQ<20>

DDR2_DQ<19>

DDR2_DQ<18>

DDR2_DQ<16>

DDR2_DQ<17>

DDR2_DQ<15>

DDR2_DQ<14>

DDR2_DQ<13>

DDR2_DQ<12>

DDR2_DQ<11>

DDR2_DQ<10>

DDR2_DQ<8>

DDR2_DQ<9>

DDR2_DQ<7>

DDR2_DQ<6>

DDR2_DQ<5>

DDR2_DQ<3>

DDR2_DQ<4>

DDR2_DQ<2>

DDR2_DQ<1>

DDR2_DQ<0>

DDR2_DM<3>

DDR2_DM<2>

DDR2_DM<1>

DDR2_DM<0>

DDR2_CSN<0>

DDR2_CKE<0>

DDR2_CK_N

DDR2_CK_P

DDR2_CA<8>

DDR2_CA<9>

DDR2_CA<7>

DDR2_CA<5>

DDR2_CA<6>

DDR2_CA<4>

DDR2_CA<3>

DDR2_CA<2>

DDR2_CA<0>

DDR2_CA<1>

DDR3_CK_N

DDR3_CK_P

DDR3_DQS_N<3>

DDR3_DQS_N<2>

DDR3_DQS_N<1>

DDR3_DQS_N<0>

DDR3_DQS_P<3>

DDR3_DQS_P<2>

DDR3_DQS_P<1>

DDR3_DQS_P<0>

DDR3_DQ<31>

DDR3_DQ<30>

DDR3_DQ<29>

DDR3_DQ<28>

DDR3_DQ<27>

DDR3_DQ<26>

DDR3_DQ<25>

DDR3_DQ<24>

DDR3_DQ<23>

DDR3_DQ<22>

DDR3_DQ<21>

DDR3_DQ<20>

DDR3_DQ<19>

DDR3_DQ<18>

DDR3_DQ<17>

DDR3_DQ<16>

DDR3_DQ<15>

DDR3_DQ<14>

DDR3_DQ<13>

DDR3_DQ<12>

DDR3_DQ<11>

DDR3_DQ<10>

DDR3_DQ<9>

DDR3_DQ<8>

DDR3_DQ<7>

DDR3_DQ<6>

DDR3_DQ<5>

DDR3_DQ<4>

DDR3_DQ<3>

DDR3_DQ<2>

DDR3_DQ<1>

DDR3_DQ<0>

DDR3_DM<3>

DDR3_DM<2>

C1726

1

2

C1725

1

2

C1720

1

2

C1707

1

2

C1706

1

2

C1705

1

2

C1703

1

2

C1766

1

2

C1765

1

2

C1769

1

2

C1768

1

2

C1760

1

2

R1799

1

2

C1796

1

2

C1797

1

2

R1796

1

2

R1797

1

2

R1798

1

2

C1794

1

2

C1795

1

2

R1794

1

2

R1795

1

2

C1792

1

2

C1793

1

2

C1790

1

2

R1792

1

2

R1793

1

2

R1790

1

2

C1791

1

2

R1791

1

2

C1746

1

2

C1745

1

2

C1742

1

2

C1740

1

2

C1728

1

2

C1729

1

2

C1700

1

2

C1716

1

2

C1708

1

2

C1749

1

2

C1748

1

2

C1701

1

2

C1702

1

2

C1715

1

2

C1711

1

2

C1710

1

2

C1756

1

2

C1755

1

2

C1743

1

2

C1776

1

2

C1775

1

2

C1736

1

2

C1735

1

2

U1700

H18

H19

J18

J19

K19

R18

R19

T19

T20

U18

M19

N19

L19

L18

L20

K20

L3

N2

G2

T4

H3

H4

R2

R3

R4

R5

T2

T3

E2

E3

E4

E5

J2

F2

F4

F5

G5

U2

V2

V3

V4

W2

W3

J3

Y3

Y4

J4

J5

K2

K3

P3

P4

L4

N3

G4

U3

K4

N4

G3

U4

P19

M4

U19

V17

W17

V16

W16

W15

V10

W10

W9

Y9

V8

W13

W12

W14

V14

Y14

Y15

C14

B12

B18

D9

C17

D17

B10

C10

D10

E10

B9

C9

B20

C20

D20

E20

B16

B19

D19

E19

E18

B8

B7

C7

D7

B6

C6

C16

B5

C5

D16

E16

B15

C15

C11

D11

D14

C12

D18

C8

D15

D12

C18

D8

W11

D13

W8

U1700

AA19

B13

Y19

Y5

Y6

C2

C3

G19

M2

P18

V11

W20

W21

AA18

AA20

P20

V20

V21

W19

Y11

Y18

Y20

Y21

AA21

AA4

AA5

B3

B4

E13

E21

M5

H20

K18

M18

N18

T18

V12

V13

V15

V9

Y17

A10

A12

E12

E17

F1

F3

H5

J1

K1

L2

N1

N5

A15

R1

W4

A16

A19

B14

C19

C21

D4

D6

U1700

A1

A18

AA1

AA2

AA3

AA6

AA7

B1

B11

B17

B2

B21

A2

C1

C13

C4

D1

D2

D21

D3

D5

E1

E14

A20

E15

E6

E7

E9

F18

F19

F20

F21

G1

G18

A21 G20

G21

H2

J20

K5

L5

M20

M3

N20

P2

A3

R20

T5

U1

U20

V18

V19

V5

V6

V7

W1

A4

W18

W5

W6

W7

Y1

Y10

Y12

Y13

Y16

Y2

A5

Y7

Y8

A6

A8

C1779

1

2

C1739

1

2

C1759

1

2

C1719

1

2

C1709

1

2

C1774

1

2

C1734

1

2

051-0301

B.0.0

17 OF 155

15 OF 73

15

15

14 15 72

15

15

15

15

15

14 15 72

14 15 72

15

14 15 72

14 72

14 15 72

剩余72页未读,继续阅读

1719 浏览量

1951 浏览量

479 浏览量

332 浏览量

508 浏览量

1719 浏览量

194 浏览量

2022-11-23 上传

106 浏览量

asdsafasdfgh

- 粉丝: 10

- 资源: 29

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- blogNextJs:我的博客是在下一个js上创建并经过高度优化的

- chrome谷歌浏览器驱动(101.0.4951.41)

- Forecast.io Weather-crx插件

- Unity实现热力图.zip

- IBFORMATIONjuin2018

- 20210806-中信证券-金地集团-600383-投资价值分析报告:信用的长期价值,品质的运营贡献.rar

- Java-Studio-3 ---菜单类

- 懒加载导入所有流行的Python数据科学库-python

- Oneindia Tamil-crx插件

- 作品答辩时尚简约实用模板.rar

- 青春树儿童摄影.rar

- egg_impact:使用Impactjs引擎的简单养鸡场游戏

- Google-Docs-Clone:基于Vuejs,SocketIO和Vuetify的实时协作编辑器。 使用MongoDB作为数据库,使用Mongoose作为ORM

- 配方奶粉

- The New York Times Living-crx插件

- ASP+access校园新闻发布管理系统(LW+源代码+任务书+说明+答辩PPT).zip

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功