Cadence原理图组装清单实践指南:方法对比与优化

需积分: 10 56 浏览量

更新于2024-09-08

收藏 561KB PDF 举报

本文主要讨论了在Cadence软件中使用CANDENCE进行原理图组装清单的实践方法。CANDENCE是一款广泛应用于电子设计自动化(EDA)的工具,适用于ASIC、FPGA和PCB设计等多个领域。文章首先介绍了CANDENCE的基本功能和用途。

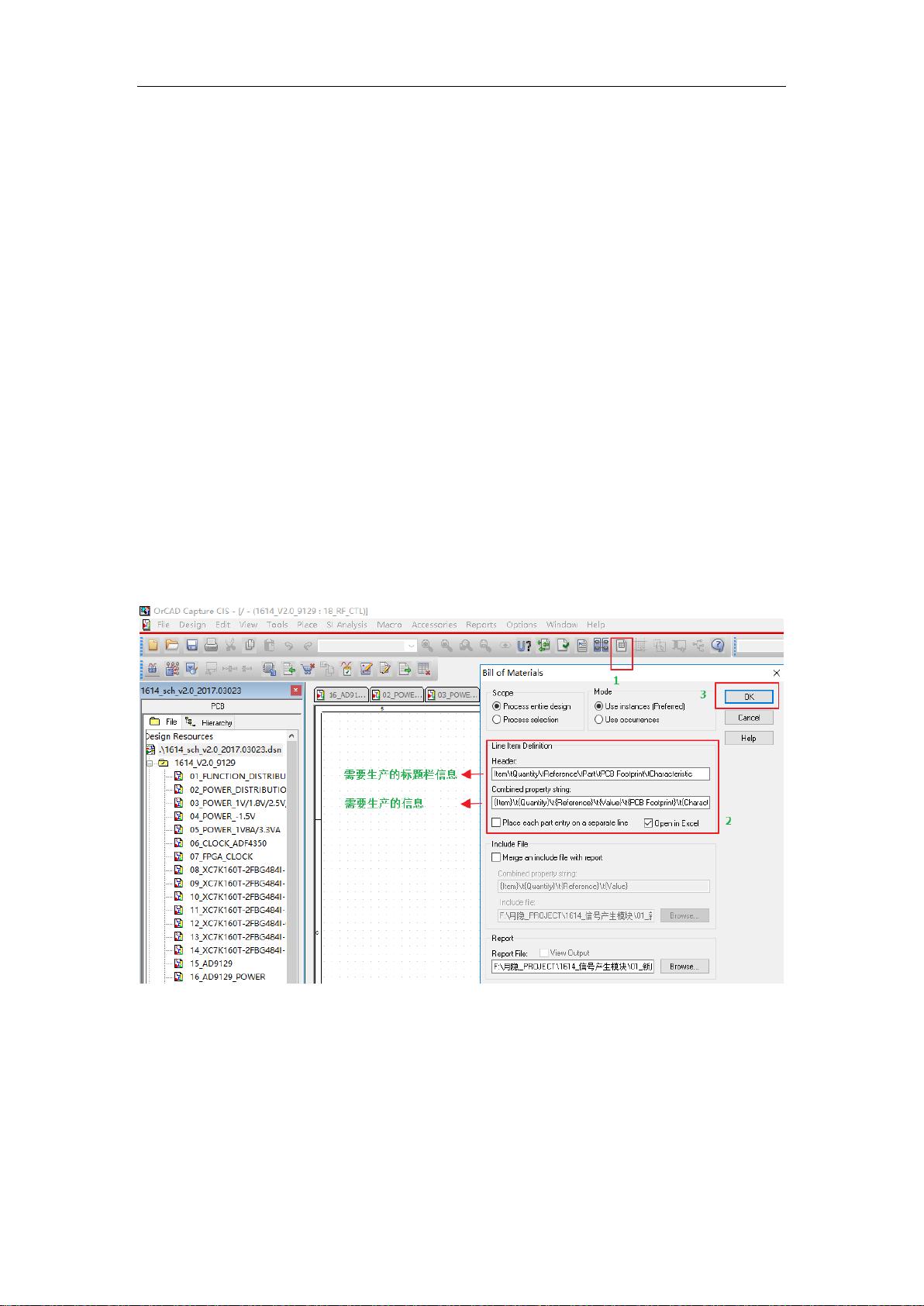

传统的组装清单制作方法通常有两种。方法一涉及导出Boom单,即原理图组件列表,然后手动将型号、数量和位号等信息复制到表格中,并补充其他必要细节。 Boom单如图1所示,虽然操作相对简单,但可能存在信息遗漏的情况,因为需要额外填写一些表格列。

方法二则是在创建元器件封装时直接嵌入组装清单所需的信息。这一步骤通过双击器件打开userproperties界面,添加自定义信息,如图4所示。这种方法的优点是Boom单制作速度快,但封装建立过程可能较为繁琐,特别是对于大量或复杂封装,查找和重复利用信息可能会变得不便。

作者针对方法一提出了个人改进方案,即创建一个《优选目录》,也就是一个器件信息表。在原理图绘制完成后,规范器件型号和封装信息是一个关键步骤,包括使用Edit/Browse/Parts功能选择元件并使用CTRL+E快捷键进入编辑界面,如图5和图7所示。在这个过程中,可以批量处理并确保信息的一致性和准确性。

本文详细讲解了在Cadence的CANDENCE环境下,如何高效地制作组装清单,以及不同方法的优缺点,并提供了一种实用的优化策略,以提高工作效率和数据管理的准确性。这对于电子设计工程师来说,是一项实用的技能指导。

2021-09-15 上传

2010-05-27 上传

2021-04-06 上传

2010-03-16 上传

2017-12-08 上传

风中月隐

- 粉丝: 2w+

- 资源: 35

最新资源

- Android圆角进度条控件的设计与应用

- mui框架实现带侧边栏的响应式布局

- Android仿知乎横线直线进度条实现教程

- SSM选课系统实现:Spring+SpringMVC+MyBatis源码剖析

- 使用JavaScript开发的流星待办事项应用

- Google Code Jam 2015竞赛回顾与Java编程实践

- Angular 2与NW.js集成:通过Webpack和Gulp构建环境详解

- OneDayTripPlanner:数字化城市旅游活动规划助手

- TinySTM 轻量级原子操作库的详细介绍与安装指南

- 模拟PHP序列化:JavaScript实现序列化与反序列化技术

- ***进销存系统全面功能介绍与开发指南

- 掌握Clojure命名空间的正确重新加载技巧

- 免费获取VMD模态分解Matlab源代码与案例数据

- BuglyEasyToUnity最新更新优化:简化Unity开发者接入流程

- Android学生俱乐部项目任务2解析与实践

- 掌握Elixir语言构建高效分布式网络爬虫