CML环振荡器驱动的96%电源抑制PLL:集成校准技术提升性能

158 浏览量

更新于2024-08-26

收藏 2.54MB PDF 举报

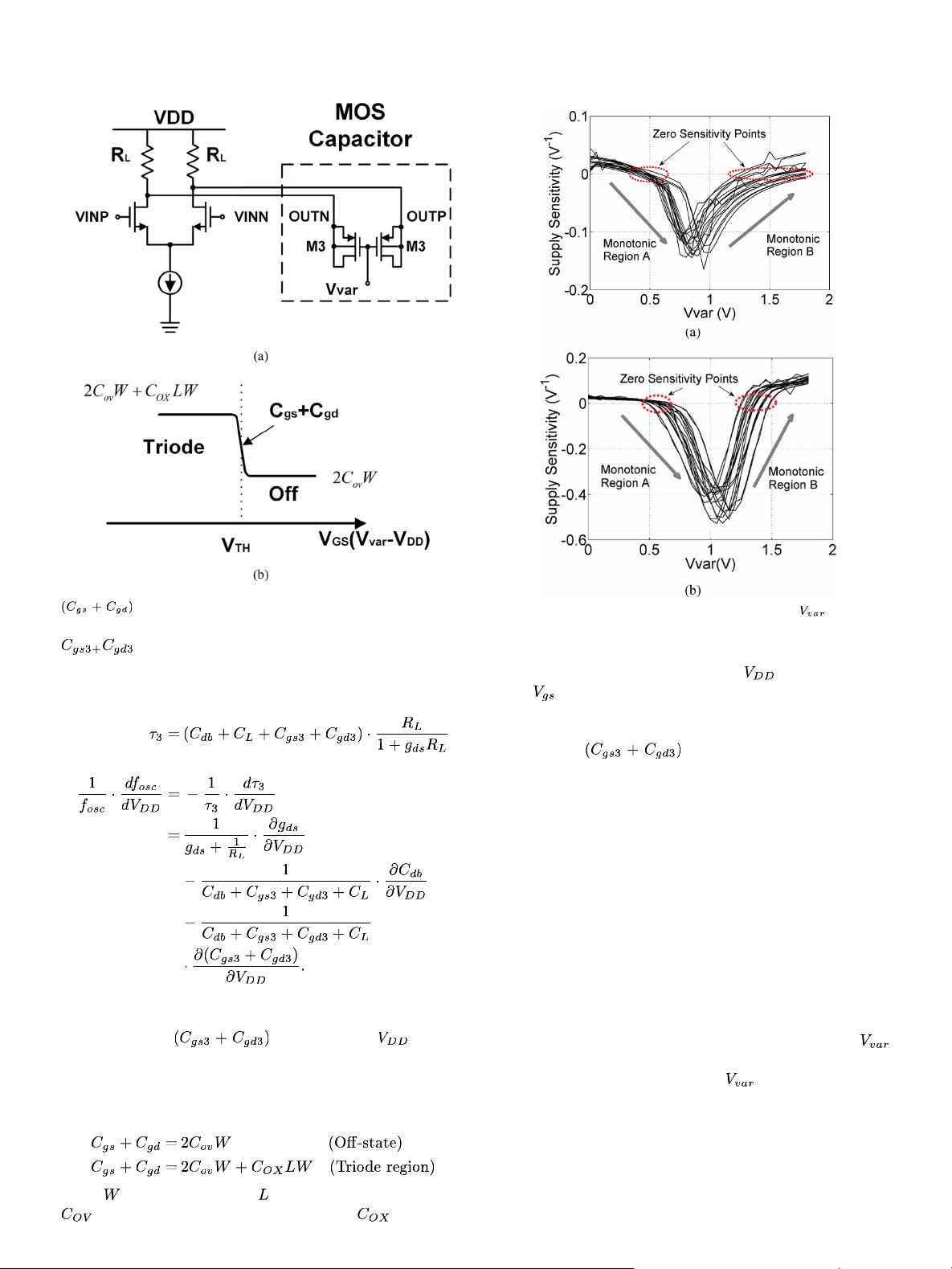

本文介绍了一篇发表在《IEEE Transactions on Microwave Theory and Techniques》上的研究论文,标题为“具有片上校准功能的1.5-2.5 GHz CML环形振荡器驱动的电源不敏感锁相环(PLL)”。该研究主要针对的是现代通信系统中广泛使用的锁相环路设计,这些系统通常依赖于高性能的时钟同步。

研究者提出了一种创新的PLL架构,采用电流模式逻辑(CML)环形振荡器作为核心元件,这种振荡器设计考虑了电源波动的补偿,旨在提高系统的电源抑制性能。文章特别提到了两种不同的CML环形振荡器拓扑的应用,它们协同工作,有效地降低了VCO(电压控制振荡器)对电源变化的敏感性。相比于传统设计,这项技术展示了高达96%以上的VCO电源灵敏度降低,这是通过精确地调整和优化电路设计实现的。

此外,文中着重强调了片上校准方案的重要性。通过集成校准机制,研究人员能够确保VCO在PLL运行时处于最佳的工作状态,从而最大限度地减少因电源波动引起的性能衰减。这种方法不仅显著改善了VCO的供电稳定性,而且还提升了闭环系统的正弦抖动性能,至少提高了70%。

该芯片是基于SMIC的0.18微米CMOS工艺实现的,这表明其在小型化和低功耗方面的优势,对于现代电子设备中的应用非常关键。整体而言,这篇研究不仅提供了先进的PLL设计策略,而且展示了如何通过技术创新来应对通信系统中电源不敏感性和抖动控制的关键挑战。

这项工作对于提升无线通信系统在不同电源条件下的稳定性和可靠性具有重要意义,为未来的无线通信技术发展提供了一个重要的技术参考点。

2013-01-08 上传

2021-09-22 上传

2021-04-04 上传

2021-09-20 上传

2021-09-14 上传

2023-06-29 上传

2023-07-18 上传

2023-07-30 上传

weixin_38514523

- 粉丝: 8

- 资源: 939

最新资源

- PureMVC AS3在Flash中的实践与演示:HelloFlash案例分析

- 掌握Makefile多目标编译与清理操作

- STM32-407芯片定时器控制与系统时钟管理

- 用Appwrite和React开发待办事项应用教程

- 利用深度强化学习开发股票交易代理策略

- 7小时快速入门HTML/CSS及JavaScript基础教程

- CentOS 7上通过Yum安装Percona Server 8.0.21教程

- C语言编程:锻炼计划设计与实现

- Python框架基准线创建与性能测试工具

- 6小时掌握JavaScript基础:深入解析与实例教程

- 专业技能工厂,培养数据科学家的摇篮

- 如何使用pg-dump创建PostgreSQL数据库备份

- 基于信任的移动人群感知招聘机制研究

- 掌握Hadoop:Linux下分布式数据平台的应用教程

- Vue购物中心开发与部署全流程指南

- 在Ubuntu环境下使用NDK-14编译libpng-1.6.40-android静态及动态库