UVM:验证方法创新,融合业界智慧

需积分: 13 196 浏览量

更新于2024-09-10

收藏 336KB PDF 举报

UVM(Universal Verification Methodology),即通用验证方法学,是验证领域的一项重大创新,由多个行业专家在Accellera这个标准化组织的框架下共同开发,旨在构建一个坚实、可重用且具有互操作性的验证基础设施。UVM的诞生并不是由单一的EDA供应商推动,而是市场上竞争公司的合作产物,这体现了业界对解决复杂系统验证挑战的共识。

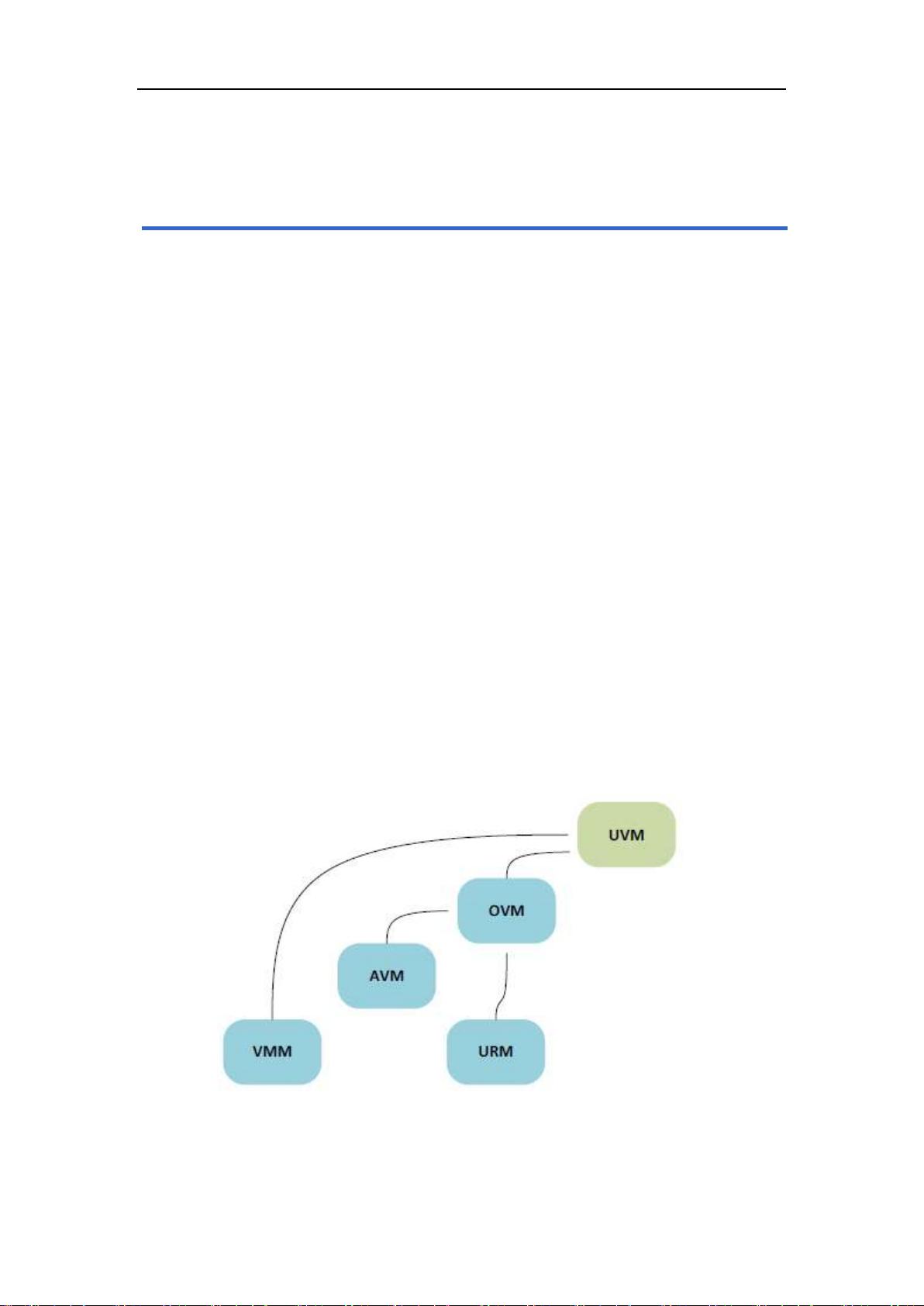

UVM的开发历程融合了前几代验证方法论的精华,如AVM(Advanced Verification Methodology)、URM(Universal Register Model)、VMM(Virtual Module Methodology)和OVM(Object-Oriented Verification Methodology)。特别地,OVM-2.1.1作为UVM的基石,对UVM的发展起到了关键作用,尽管UVM在很大程度上继承了这些方法,但它并非简单的堆砌,而是引入了全新的功能和使用模式,提升了验证流程的效率和灵活性。

UVM的核心价值在于它为现代系统-on-chip(SoC)中的寄存器建模提供了全面的支持。在SoC设计中,寄存器扮演着连接器的角色,用于设备初始化、配置和数据交换。UVM提供了丰富的功能,如“后门访问”,允许测试bench通过其模型直接访问RTL中的寄存器,这对于验证器件功能至关重要。此外,UVM的模型化能力使得测试bench能够更精确地模拟和控制寄存器的行为,从而实现更深入的验证。

UVM作为下一代验证方法学,不仅整合了先前的最佳实践,还通过创新的架构和功能设计,提高了验证的效率和一致性,成为了电子设计自动化领域的重要里程碑。它标志着验证方法的进化,使得验证工程师能够更加高效地应对复杂系统的验证挑战。

2245 浏览量

351 浏览量

291 浏览量

点击了解资源详情

1050 浏览量

176 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

gouch0819

- 粉丝: 0

最新资源

- Google Earth链接插件:Wikipedia上的实用扩展

- PHP面向对象编程:数据库操作类的封装与实现

- Vue技术面试必备题及答案解析

- USB Type-C接口Cadence PCB封装设计指南

- AMI TOOL 1.63:专业AMI BIOS修改工具

- Linux下Realtek-8188/8192无线网卡驱动安装指南

- Java实现图片缩放、圆角及透明处理教程

- 易语言开发的Access数据库SQL语句切换工具

- Python便利贴插件:提升Thonny编辑器的编程体验

- 网络抓包工具实现与数据分析教程

- Python制作的极简主义Discord机器人Astro

- 打造美观专业网页的必备工具:WEB编辑器解析

- PHP-DataBase类:高效数据库操作封装

- WinCE设备联网同步时间的实现方法

- 隐藏ЧатРазЖивем的Valeron帖子浏览器扩展

- JavaScript实现的花式滑块效果教程