低压差LDO稳压器:拓扑与应用革新

172 浏览量

更新于2024-08-30

收藏 211KB PDF 举报

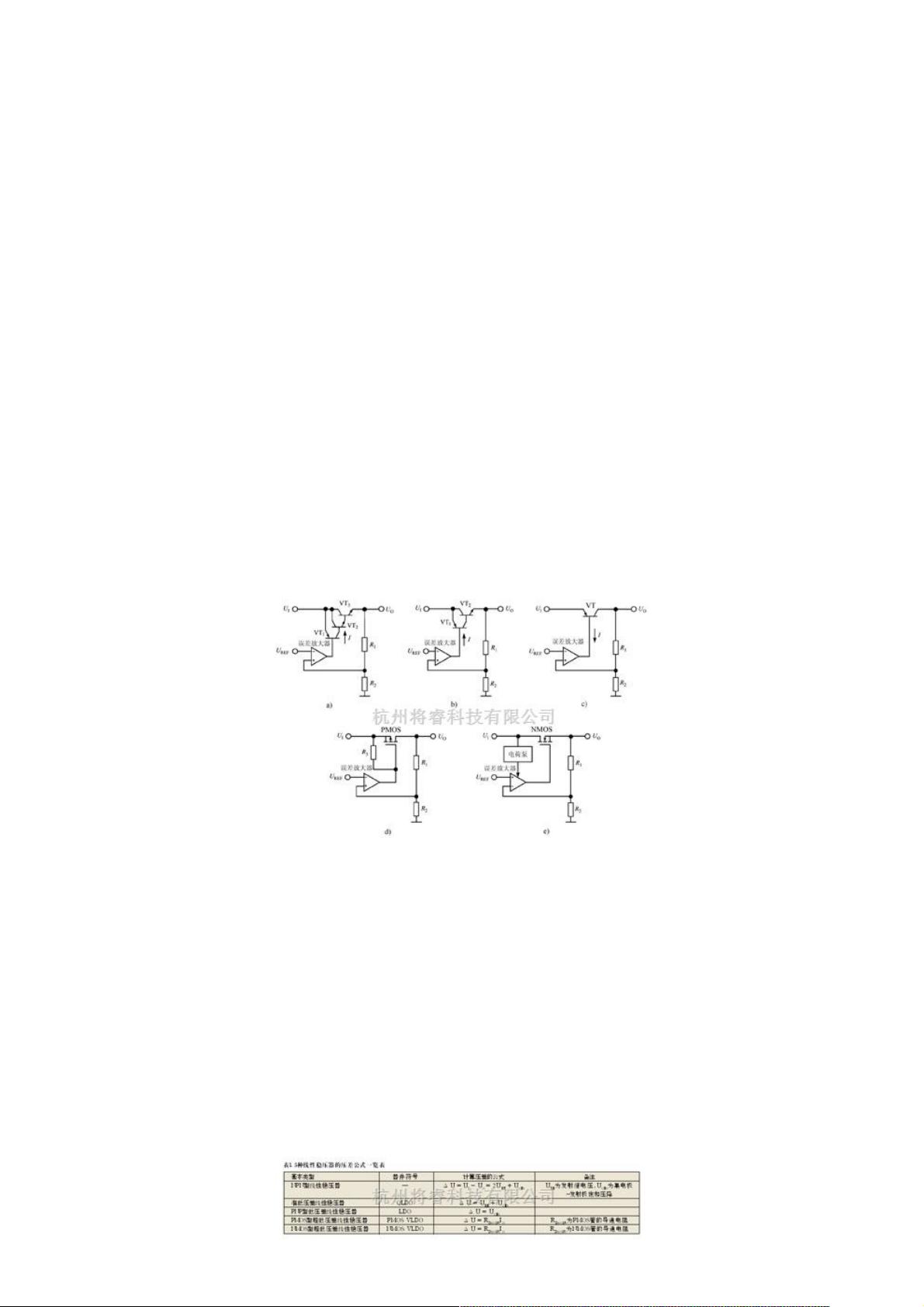

低压差线性稳压器(LDO)是现代电源技术中的一个重要组件,随着便携式电子设备对小型化、高效能和低功耗需求的提升,它们的应用领域得到了显著扩展。传统集成线性稳压器由于输入/输出压差较大,限制了它们在低电压应用场景中的使用,而LDO则通过其独特的拓扑结构解决了这一问题。

LDO的核心特点是压降电压极低,通常在200mV左右,这对于正输出电压设计尤其明显,使用的是PNP功率晶体管。这种晶体管允许在饱和状态下工作,从而实现了极低的电压损耗。相比之下,NPN复合电源晶体管的压降通常在2V左右,而负输出LDO则使用NPN作为传递设备,其工作原理类似于正输出LDO。

MOS功率晶体管是LDO发展中的一种新趋势,它可以进一步降低压降电压,特别是当负载电流较小时,压降甚至可以低至几十毫伏。这使得LDO在微电源系统和低电压应用中具有优势,比如5V转3.3V的转换,其压降仅为1V,显著减少了电源设备的功耗和尺寸。

LDO的低功耗特性使其在便携式电子设备如移动电话、笔记本电脑、可穿戴设备等中广泛应用,这些设备往往依赖于电池供电,每一点能量的损失都是宝贵的。此外,LDO还以其高效率、低噪声、高抗扰性能和小型化的体积赢得了设计师的青睐。它们对于电源管理电路的设计至关重要,特别是在那些对电源稳定性要求极高或者电源电压波动大的环境中。

低压差线性稳压器通过优化的拓扑设计和新型半导体元件的应用,极大地提高了电子设备在低电压、小功率场景下的性能表现,推动了整个电源技术的发展,使得电子产品的功能更加强大且更加绿色节能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-10-22 上传

2020-12-13 上传

2020-11-11 上传

2020-11-11 上传

2020-10-25 上传

2020-11-22 上传

weixin_38527978

- 粉丝: 5

- 资源: 900

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率