SystemVerilog验证方法学:应对芯片验证挑战

需积分: 5 66 浏览量

更新于2024-07-09

收藏 668KB PDF 举报

“SystemVerilogForVerifinChinese.pdf”是一份关于使用SystemVerilog进行硬件设计验证的中文文档,主要探讨了SystemVerilog在解决芯片验证挑战中的应用和验证方法学。

SystemVerilog是一种强大的硬件描述语言,尤其在验证领域扮演着核心角色。随着系统级芯片(SoC)和可重用IP模块设计的复杂度不断提升,传统的验证方法往往难以应对这种增长,导致验证成为设计流程中最关键且最具挑战性的部分。为了解决这一问题,SystemVerilog提供了丰富的语义支持,以及基于覆盖率驱动的可重用验证方法学。

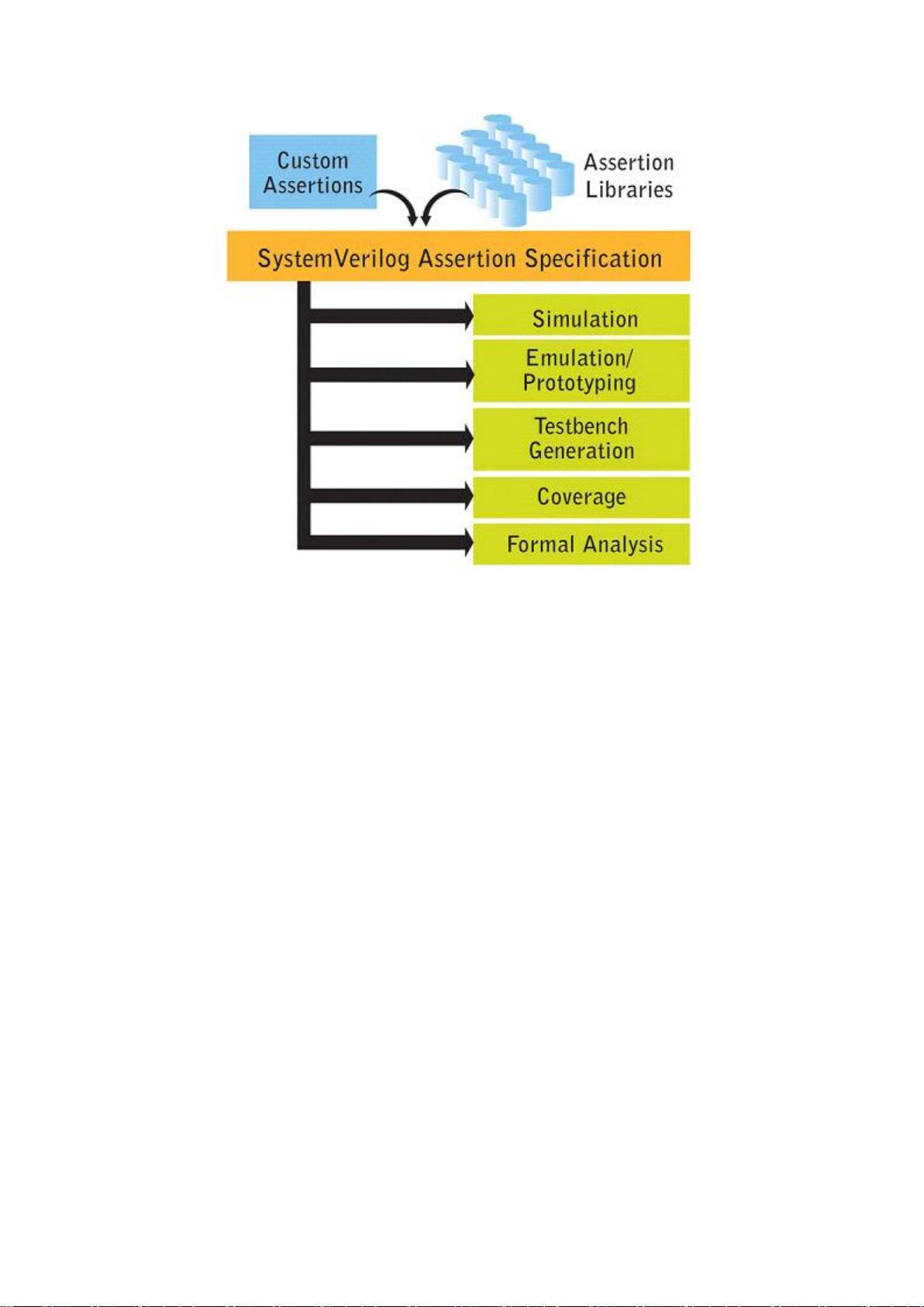

该文档的第一部分深入介绍了SystemVerilog验证方法学,这与《VMM for SystemVerilog》一书中的内容相呼应。VMM(验证管理模型)是一种建立在SystemVerilog基础上的验证框架,旨在创建可扩展、可预测和可重用的验证环境。VMM允许工程师利用断言、重用、自动生成验证平台、覆盖率分析和形式验证等高级验证技术,有效地处理寄存器传输层(RTL)和系统级别的验证问题。这样的环境有助于提升验证的信心度,确保芯片在初期就能达到较高的验证质量。

验证面临的挑战主要包括设计复杂度的增加和验证信心的不足。许多SoC项目在初次流片时就会失败,其主要原因就是功能缺陷。设计的复杂性使得在所有可能条件下模拟执行变得极其困难,尤其是在寻找设计中的边界条件和深层缺陷时。因此,需要在有限的资源和紧迫的时间表下,尽早发现设计错误。

SystemVerilog提供的验证技术包括但不限于手动编写验证代码、使用约束随机生成仿真激励以及高级验证平台。通过功能覆盖率的统计,可以进一步提高自动验证的效率。此外,断言的使用有助于确认设计的正确性,并能诊断设计中的潜在问题。

总而言之,SystemVerilogForVerifinChinese.pdf这份文档详细阐述了SystemVerilog在验证领域的应用,以及如何利用SystemVerilog和VMM来构建高效的验证环境,以应对SoC和IP验证的复杂性挑战。通过学习和应用这些方法,工程师可以更有效地验证设计,降低首次流片失败的风险。

2024-12-26 上传

2024-12-26 上传

2024-12-26 上传

2024-12-26 上传

hudsonhua

- 粉丝: 0

- 资源: 4

最新资源

- ATT7022B-programe,网络验证c语言源码,c语言

- Utils:一些实用程序

- chatomud

- configs:基于UNIX的点文件

- Feminazi a flor-crx插件

- 802.11b PHY Simulink 模型:802.11b 基带物理层的 Simulink:registered: 模型。-matlab开发

- SQLITE

- CpuTimer0,c语言read源码,c语言

- java-projects

- 오늘의 운세-crx插件

- technical-community-builders:雇用技术社区建设者的公司

- csrf_attack_example

- grpar:提取构建引擎组(.grp)文件的工具-开源

- Backjoon

- 每日日记:一种日记应用程序,融合了我在编码过程中所学到的技术

- AT89C2051UPS,c语言输出图形源码,c语言