5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

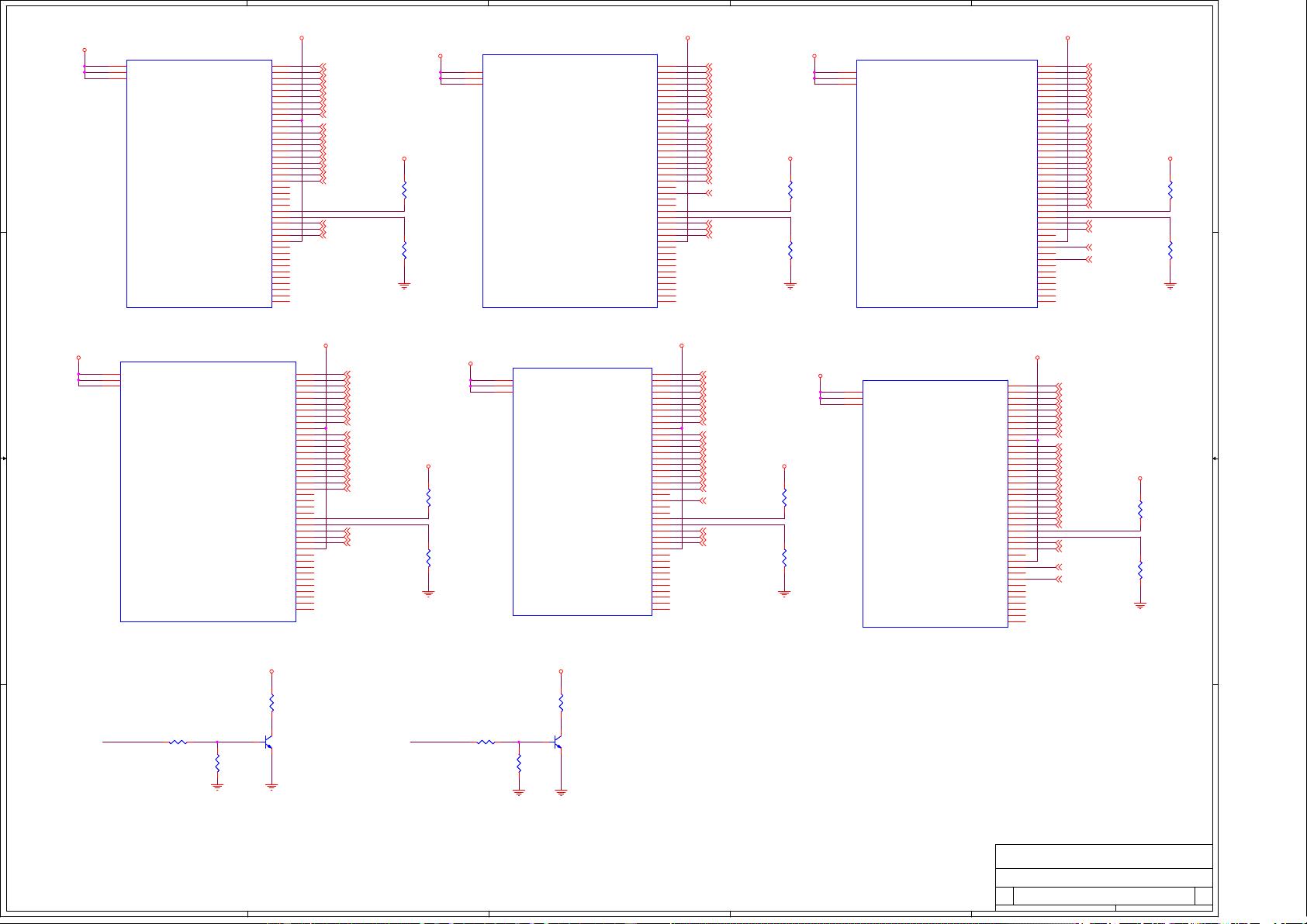

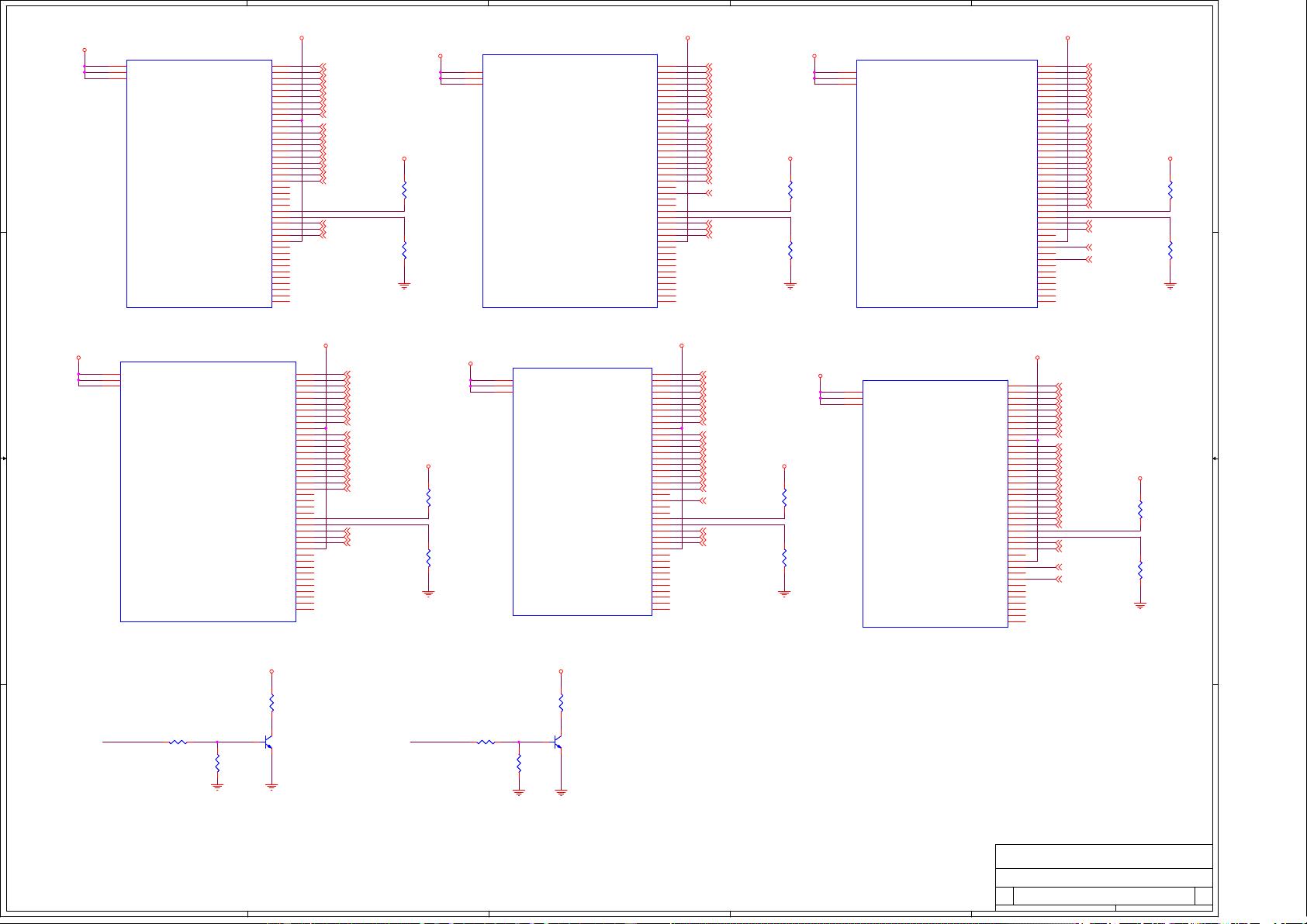

C0_PHY_INIT_DONE C1_PHY_INIT_DONE

VCC1V8

VCC1V8 VCC1V8

VCC1V8

VCC1V8

VCC1V8

VREF_DDR

VCC1V8

VREF_DDR

VCC1V8

VREF_DDR

VCC1V8

VREF_DDR

VCC1V8

VREF_DDR

VREF_DDR

VCC2V5 VCC2V5

VCC1V8

VCC1V8

C0_DDR2_DQ<0>

C0_DDR2_DQ<1>

C0_DDR2_DQ<2>

C0_DDR2_DQ<3>

C0_DDR2_DM<0>

C0_DDR2_DQ<4>

C0_DDR2_DQ<5>

C0_DDR2_DQ<6>

C0_DDR2_DQ<7>

C0_DDR2_DQ<8>

C0_DDR2_DQ<9>

C0_DDR2_DQ<10>

C0_DDR2_DQ<11>

C0_DDR2_DM<1>

C0_DDR2_DQ<12>

C0_DDR2_DQS_N<0>

C0_DDR2_DQS<0>

C0_DDR2_DQS<1>

C0_DDR2_DQS_N<1>

C0_DDR2_DQ<13>

C0_DDR2_DQ<14>

C0_DDR2_DQ<15>

C0_DDR2_DQ<16>

C0_DDR2_DQ<17>

C0_DDR2_DQ<18>

C0_DDR2_DQ<19>

C0_DDR2_DM<2>

C0_DDR2_DQ<20>

C0_DDR2_DQ<21>

C0_DDR2_DQ<22>

C0_DDR2_DQ<23>

C0_DDR2_DQ<24>

C0_DDR2_DQ<25>

C0_DDR2_DQ<26>

C0_DDR2_DQ<27>

C0_DDR2_DM<3>

C0_DDR2_DQ<28>

C0_DDR2_DQS_N<2>

C0_DDR2_DQS<2>

C0_DDR2_DQS<3>

C0_DDR2_DQS_N<3>

C0_DDR2_DQ<29>

C0_DDR2_DQ<30>

C0_DDR2_DQ<31>

C0_PHY_INIT_DONE

C1_DDR2_DQ<0>

C1_DDR2_DQ<1>

C1_DDR2_DQ<2>

C1_DDR2_DQ<3>

C1_DDR2_DM<0>

C1_DDR2_DQ<4>

C1_DDR2_DQ<5>

C1_DDR2_DQ<6>

C1_DDR2_DQ<7>

C1_DDR2_DQ<8>

C1_DDR2_DQ<9>

C1_DDR2_DQ<10>

C1_DDR2_DQ<11>

C1_DDR2_DM<1>

C1_DDR2_DQ<12>

C1_DDR2_DQS_N<0>

C1_DDR2_DQS<0>

C1_DDR2_DQS<1>

C1_DDR2_DQS_N<1>

C1_DDR2_DQ<13>

C1_DDR2_DQ<14>

C1_DDR2_DQ<15>

C1_DDR2_DQ<16>

C1_DDR2_DQ<17>

C1_DDR2_DQ<18>

C1_DDR2_DQ<19>

C1_DDR2_DM<2>

C1_DDR2_DQ<20>

C1_DDR2_DQ<21>

C1_DDR2_DQ<22>

C1_DDR2_DQ<23>

C1_DDR2_DQ<24>

C1_DDR2_DQ<25>

C1_DDR2_DQ<26>

C1_DDR2_DQ<27>

C1_DDR2_DM<3>

C1_DDR2_DQ<28>

C1_DDR2_DQS_N<2>

C1_DDR2_DQS<2>

C1_DDR2_DQS<3>

C1_DDR2_DQS_N<3>

C1_DDR2_DQ<29>

C1_DDR2_DQ<30>

C1_DDR2_DQ<31>

C1_PHY_INIT_DONE

C0_DDR2_CK<0>

C0_DDR2_CK_N<0>

C0_DDR2_CK<1>

C0_DDR2_CK_N<1>

C0_DDR2_A<13>

C0_DDR2_A<12>

C0_DDR2_A<11>

C0_DDR2_A<10>

C0_DDR2_A<9>

C0_DDR2_A<8>

C0_DDR2_A<7>

C0_DDR2_A<6>

C0_DDR2_A<5>

C0_DDR2_A<4>

C0_DDR2_A<3>

C0_DDR2_A<1>

C0_DDR2_A<2>

C0_DDR2_A<0>

C0_DDR2_BA<2>

C0_DDR2_WE_N

C0_DDR2_CS_N

C0_DDR2_BA<0>

C0_DDR2_ODT

C0_DDR2_CKE

C0_DDR2_BA<1>

C0_DDR2_CAS_N

C0_DDR2_RAS_N

C1_DDR2_CKE

C1_DDR2_CK<0>

C1_DDR2_CK_N<0>

C1_DDR2_CK<1>

C1_DDR2_CK_N<1>

C1_DDR2_A<13>

C1_DDR2_A<12>

C1_DDR2_A<11>

C1_DDR2_A<10>

C1_DDR2_A<9>

C1_DDR2_A<8>

C1_DDR2_A<7>

C1_DDR2_A<6>

C1_DDR2_A<5>

C1_DDR2_A<4>

C1_DDR2_A<3>

C1_DDR2_A<1>

C1_DDR2_A<2>

C1_DDR2_A<0>

C1_DDR2_BA<2>

C1_DDR2_WE_N

C1_DDR2_CS_N

C1_DDR2_BA<0>

C1_DDR2_BA<1>

C1_DDR2_CAS_N

C1_DDR2_RAS_N

C1_DDR2_ODT

Title

Size Document Number Rev

Date: Sheet

of

FPGA 0.01

PCI-E VIRTEX5

C

315Tuesday, March 01, 2011

Title

Size Document Number Rev

Date: Sheet

of

FPGA 0.01

PCI-E VIRTEX5

C

315Tuesday, March 01, 2011

Title

Size Document Number Rev

Date: Sheet

of

FPGA 0.01

PCI-E VIRTEX5

C

315Tuesday, March 01, 2011

R18

49.9

R18

49.9

R19

49.9

R19

49.9

R28

49.9

R28

49.9

R17

49.9

R17

49.9

R20

49.9

R20

49.9

R24

49.9

R24

49.9

R14

10K

R14

10K

R29

49.9

R29

49.9

R15

10K

R15

10K

FF1136

BNAK 21

U2-11

XC5VLX50T-FF1136

FF1136

BNAK 21

U2-11

XC5VLX50T-FF1136

IO_L0P_21

AA25

IO_L0N_21

AA26

IO_L1P_21

AB27

IO_L1N_21

AC27

IO_L2P_21

Y24

IO_L2N_21

AA24

IO_L3P_21

AB25

IO_L3N_21

AB26

IO_L4P_21

AC28

IO_L4N_VREF_21

AD27

IO_L5P_21

AB28

IO_L5N_21

AA28

IO_L6P_21

AG28

IO_L6N_21

AH28

IO_L7P_21

AE28

IO_L7N_21

AF28

IO_L8P_CC_21

AK26

IO_L8N_CC_21

AJ27

IO_L9P_CC_21

AK29

IO_L9N_CC_21

AJ29

IO_L10P_CC_21

AK28

IO_L10N_CC_21

AK27

IO_L11P_CC_21

AH27

IO_L11N_CC_21

AJ26

IO_L12P_VRN_21

AJ25

IO_L12N_VRP_21

AH25

IO_L13P_21

AF24

IO_L13N_21

AG25

IO_L14P_21

AG27

IO_L14N_VREF_21

AG26

IO_L15P_21

AF25

IO_L15N_21

AF26

IO_L16P_21

AE27

IO_L16N_21

AE26

IO_L17P_21

AC25

IO_L17N_21

AC24

IO_L18P_21

AD26

IO_L18N_21

AD25

IO_L19P_21

AD24

IO_L19N_21

AE24

VCCO1_21

AJ28

VCCO2_21

AM29

VCCO3_21

AL32

R25

49.9

R25

49.9

FF1136

BNAK 13

U2-9

XC5VLX50T-FF1136

FF1136

BNAK 13

U2-9

XC5VLX50T-FF1136

IO_L0P_SM8P_13

V32

IO_L0N_SM8N_13

V33

IO_L1P_SM7P_13

W34

IO_L1N_SM7N_13

V34

IO_L2P_SM6P_13

Y33

IO_L2N_SM6N_13

AA33

IO_L3P_SM5P_13

AA34

IO_L3N_SM5N_13

Y34

IO_L4P_13

Y32

IO_L4N_VREF_13

W32

IO_L5P_SM4P_13

AC34

IO_L5N_SM4N_13

AD34

IO_L6P_SM3P_13

AC32

IO_L6N_SM3N_13

AB32

IO_L7P_SM2P_13

AC33

IO_L7N_SM2N_13

AB33

IO_L8P_CC_SM1P_15

AF33

IO_L8N_CC_SM1N_15

AE33

IO_L9P_CC_SM0P_13

AF34

IO_L9N_CC_SM0N_13

AE34

IO_L10P_CC_13

AH34

IO_L10N_CC_13

AJ34

IO_L11P_CC_13

AD32

IO_L11N_CC_13

AE32

IO_L12P_VRN_13

AG33

IO_L12N_VRP_13

AH33

IO_L13P_13

AK34

IO_L13N_13

AK33

IO_L14P_13

AG32

IO_L14N_VREF_13

AH32

IO_L15P_13

AJ32

IO_L15N_13

AK32

IO_L16P_13

AL34

IO_L16N_13

AL33

IO_L17P_13

AM33

IO_L17N_13

AM32

IO_L18P_13

AN34

IO_L18N_13

AN33

IO_L19P_13

AN32

IO_L19N_13

AP32

VCCO1_13

W28

VCCO2_13

AB29

VCCO3_13

AA32

T1

9013

SOT23

T1

9013

SOT23

1

32

FF1136

BNAK 15

U2-7

XC5VLX50T-FF1136

FF1136

BNAK 15

U2-7

XC5VLX50T-FF1136

IO_L0P_15

E29

IO_L0N_15

F29

IO_L1P_15

G30

IO_L1N_15

F30

IO_L2P_15

H29

IO_L2N_15

J29

IO_L3P_15

F31

IO_L3N_15

E31

IO_L4P_15

L29

IO_L4N_VREF_15

K29

IO_L5P_15

H30

IO_L5N_15

G31

IO_L6P_15

J30

IO_L6N_15

J31

IO_L7P_15

L30

IO_L7N_15

M30

IO_L8P_CC_15

N29

IO_L8N_CC_15

P29

IO_L9P_CC_15

K31

IO_L9N_CC_15

L31

IO_L10P_CC_15

P31

IO_L10N_CC_15

P30

IO_L11P_CC_15

M31

IO_L11N_CC_15

N30

IO_L12P_VRN_15

R28

IO_L12N_VRP_15

R29

IO_L13P_15

T31

IO_L13N_15

R31

IO_L14P_15

U30

IO_L14N_VREF_15

T30

IO_L15P_15

T28

IO_L15N_15

T29

IO_L16P_15

U27

IO_L16N_15

U28

IO_L17P_15

R26

IO_L17N_15

R27

IO_L18P_15

U26

IO_L18N_15

T26

IO_L19P_15

U25

IO_L19N_15

T25

VCCO1_15

M29

VCCO2_15

L32

VCCO3_15

P33

R26

49.9

R26

49.9

R16

330

R16

330

R23

330

R23

330

R27

49.9

R27

49.9

R21 10KR21 10K

R22

10K

R22

10K

T2

9013

SOT23

T2

9013

SOT23

1

32

R30

49.9

R30

49.9

FF1136

BNAK 17

U2-10

XC5VLX50T-FF1136

FF1136

BNAK 17

U2-10

XC5VLX50T-FF1136

IO_L0P_17

W24

IO_L0N_17

V24

IO_L1P_17

Y26

IO_L1N_17

W26

IO_L2P_17

V25

IO_L2N_17

W25

IO_L3P_17

Y27

IO_L3N_17

W27

IO_L4P_17

V30

IO_L4N_VREF_17

W30

IO_L5P_17

V28

IO_L5N_17

V27

IO_L6P_17

W31

IO_L6N_17

Y31

IO_L7P_17

W29

IO_L7N_17

V29

IO_L8P_CC_17

Y28

IO_L8N_CC_17

Y29

IO_L9P_CC_17

AB31

IO_L9N_CC_17

AA31

IO_L10P_CC_17

AB30

IO_L10N_CC_17

AC30

IO_L11P_CC_17

AA29

IO_L11N_CC_17

AA30

IO_L12P_VRN_17

AD31

IO_L12N_VRP_17

AE31

IO_L13P_17

AD30

IO_L13N_17

AC29

IO_L14P_17

AF31

IO_L14N_VREF_17

AG31

IO_L15P_17

AE29

IO_L15N_17

AD29

IO_L16P_17

AJ31

IO_L16N_17

AK31

IO_L17P_17

AF29

IO_L17N_17

AF30

IO_L18P_17

AJ30

IO_L18N_17

AH30

IO_L19P_17

AH29

IO_L19N_17

AG30

VCCO1_17

AE30

VCCO2_17

AH31

VCCO3_17

AD33

FF1136

BNAK 19

U2-8

XC5VLX50T-FF1136

FF1136

BNAK 19

U2-8

XC5VLX50T-FF1136

IO_L0P_19

K24

IO_L0N_19

L24

IO_L1P_19

L25

IO_L1N_19

L26

IO_L2P_19

J24

IO_L2N_19

J25

IO_L3P_19

M25

IO_L3N_19

M26

IO_L4P_19

J27

IO_L4N_VREF_19

J26

IO_L5P_19

G25

IO_L5N_19

G26

IO_L6P_19

H25

IO_L6N_19

H24

IO_L7P_19

F25

IO_L7N_19

F26

IO_L8P_CC_19

G27

IO_L8N_CC_19

H27

IO_L9P_CC_19

H28

IO_L9N_CC_19

G28

IO_L10P_CC_19

E28

IO_L10N_CC_19

F28

IO_L11P_CC_19

E26

IO_L11N_CC_19

E27

IO_L12P_VRN_19

N27

IO_L12N_VRP_19

M27

IO_L13P_19

K28

IO_L13N_19

L28

IO_L14P_19

K27

IO_L14N_VREF_19

K26

IO_L15P_19

M28

IO_L15N_19

N28

IO_L16P_19

P26

IO_L16N_19

P27

IO_L17P_19

N24

IO_L17N_19

P24

IO_L18P_19

P25

IO_L18N_19

N25

IO_L19P_19

R24

IO_L19N_19

T24

VCCO1_19

J28

VCCO2_19

E30

VCCO3_19

H31

FF1136

BNAK 11

U2-6

XC5VLX50T-FF1136

FF1136

BNAK 11

U2-6

XC5VLX50T-FF1136

VCCO1_11

T27

VCCO2_11

R30

VCCO3_11

V31

IO_L0P_11

B32

IO_L0N_11

A33

IO_L1P_11

B33

IO_L1N_11

C33

IO_L2P_11

C32

IO_L2N_11

D32

IO_L3P_11

C34

IO_L3N_11

D34

IO_L4P_11

G32

IO_L4N_VREF_11

H32

IO_L5P_11

F33

IO_L5N_11

E34

IO_L6P_11

E32

IO_L6N_11

E33

IO_L7P_11

G33

IO_L7N_11

F34

IO_L8P_CC_11

J32

IO_L8N_CC_11

H33

IO_L9P_CC_11

H34

IO_L9N_CC_11

J34

IO_L10P_CC_SM15P_11

L34

IO_L10N_CC_SM15N_11

K34

IO_L11P_CC_SM14P_11

K33

IO_L11N_CC_SM14N_11

K32

IO_L12P_VRN_11

N33

IO_L12N_VRP_11

M33

IO_L13P_11

L33

IO_L13N_11

M32

IO_L14P_11

P34

IO_L14N_VREF_11

N34

IO_L15P_SM13P_11

P32

IO_L15N_SM13N_11

N32

IO_L16P_SM12P_11

T33

IO_L16N_SM12N_11

R34

IO_L17P_SM11P_11

R33

IO_L17N_SM11N_11

R32

IO_L18P_SM10P_11

U33

IO_L18N_SM10N_11

T34

IO_L19P_SM9P_11

U32

IO_L19N_SM9N_11

U31

R31

49.9

R31

49.9