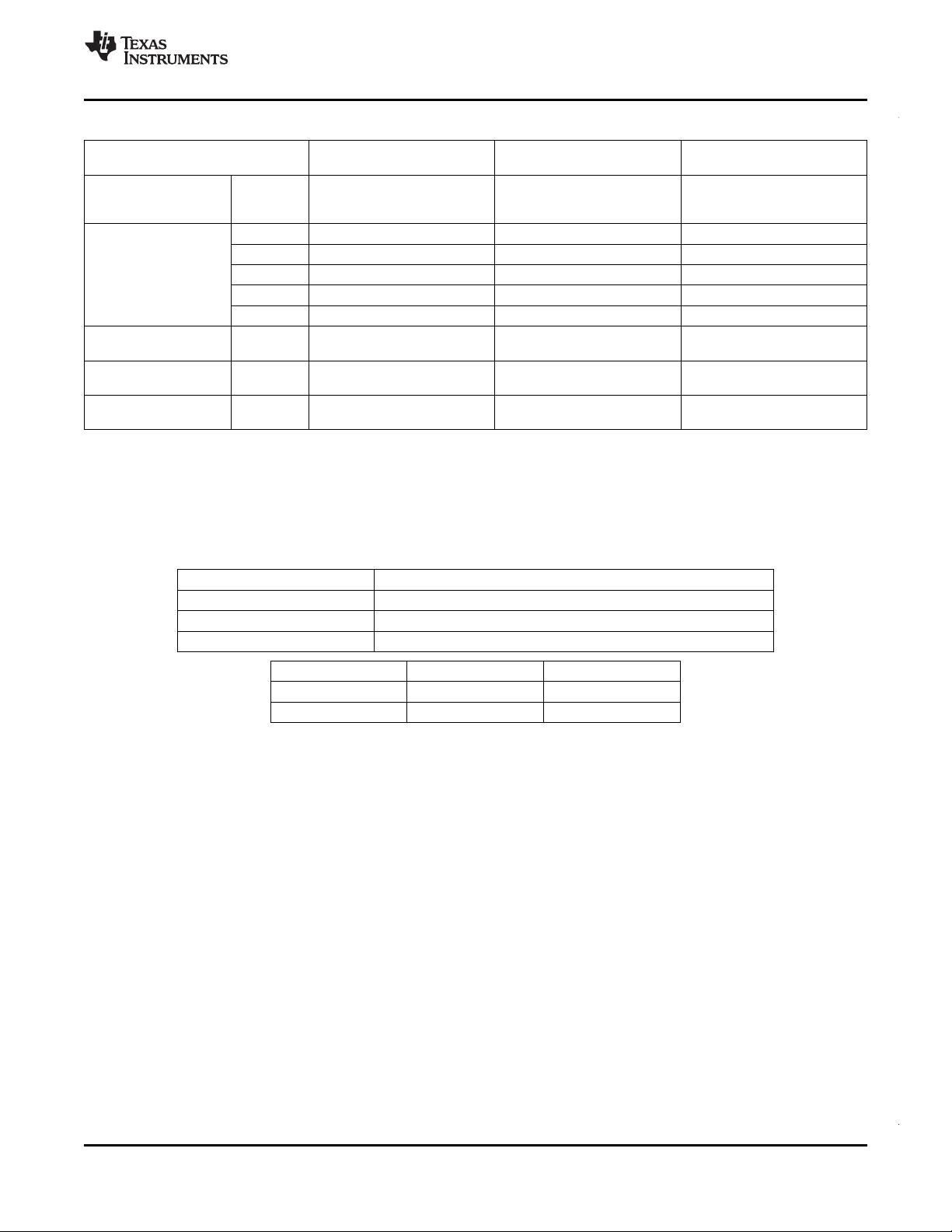

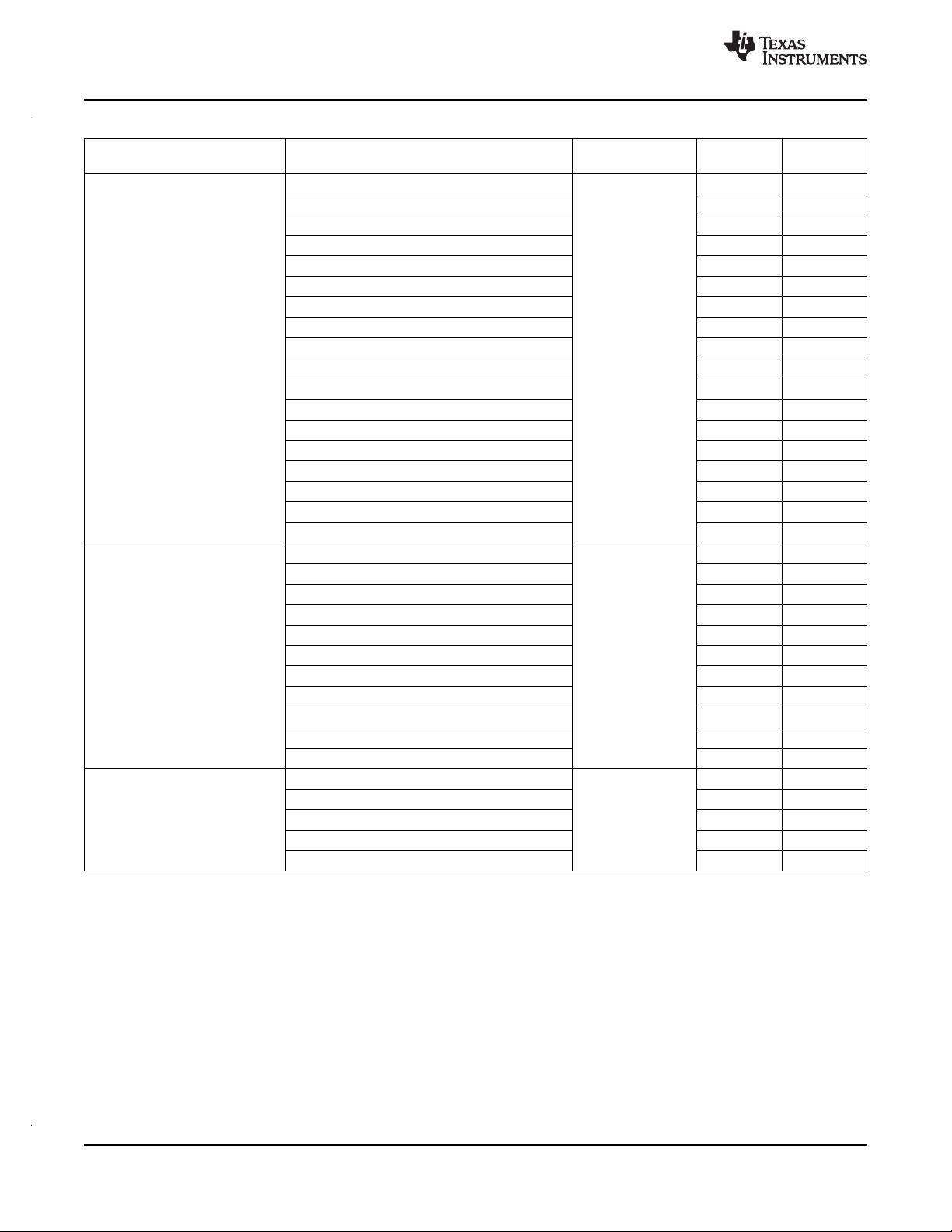

Peripherals

Digital I/O

Oscillator and System Clock

Power Management Module (PMM)

Hardware Multiplier

MSP430F543x, MSP430F541x

MSP430F543xA, MSP430F541xA

SLAS609 – JUNE 2008 ......................................................................................................................................................................................................

www.ti.com

Peripherals are connected to the CPU through data, address, and control busses and can be handled using all

instructions. For complete module descriptions, refer to the MSP430x5xx Family User ' s Guide, literature number

SLAU208 .

There are up to ten 8-bit I/O ports implemented: For 100 pin options, P1 through P10 are complete. P11 contains

three individual I/O ports.For 80 pin options, P1 through P7 are complete. P8 contains seven individual I/O ports.

P9 through P11 do not exist. Port PJ contains four individual I/O ports, common to all devices.

• All individual I/O bits are independently programmable.

• Any combination of input, output, and interrupt conditions is possible.

• Programmable pullup or pulldown on all ports.

• Programmable drive strength on all ports.

• Edge-selectable interrupt input capability for all the eight bits of ports P1 and P2.

• Read/write access to port-control registers is supported by all instructions.

• Ports can be accessed byte-wise (P1 through P11) or word-wise in pairs (PA through PF).

The clock system in the MSP430x5xx family of devices is supported by the Unified Clock System (UCS) module

that includes support for a 32 kHz watch crystal oscillator (XT1 LF mode), an internal very-low-power

low-frequency oscillator (VLO), an internal trimmed low-frequency oscillator (REFO), an integrated internal

digitally-controlled oscillator (DCO), and a high-frequency crystal oscillator (XT1 HF mode or XT2). The UCS

module is designed to meet the requirements of both low system cost and low-power consumption. The UCS

module features digital frequency locked loop (FLL) hardware that, in conjunction with a digital modulator,

stabilizes the DCO frequency to a programmable multiple of the watch crystal frequency. The internal DCO

provides a fast turn-on clock source and stabilizes in less than 5 µ s. The UCS module provides the following

clock signals:

• Auxiliary clock (ACLK), sourced from a 32 kHz watch crystal, a high-frequency crystal, the internal

low-frequency oscillator (VLO), the trimmed low-frequency oscillator (REFO), or the internal digitally-controlled

oscillator DCO.

• Main clock (MCLK), the system clock used by the CPU. MCLK can be sourced by same sources made

available to ACLK.

• Sub-Main clock (SMCLK), the subsystem clock used by the peripheral modules. SMCLK can be sourced by

same sources made available to ACLK.

• ACLK/n, the buffered output of ACLK, ACLK/2, ACLK/4, ACLK/8, ACLK/16, ACLK/32.

The PMM includes an integrated voltage regulator that supplies the core voltage to the device and contains

programmable output levels to provide for power optimization. The PMM also includes supply voltage supervisor

(SVS) and supply voltage monitoring (SVM) circuitry, as well as brownout protection. The brownout circuit is

implemented to provide the proper internal reset signal to the device during power-on and power-off. The

SVS/SVM circuitry detects if the supply voltage drops below a user-selectable level and supports both supply

voltage supervision (the device is automatically reset) and supply voltage monitoring (SVM, the device is not

automatically reset). SVS and SVM circuitry is available on the primary supply and core supply.

The multiplication operation is supported by a dedicated peripheral module. The module performs operations with

32-bit, 24-bit, 16-bit, and 8-bit operands. The module is capable of supporting signed and unsigned multiplication

as well as signed and unsigned multiply and accumulate operations.

16 Submit Documentation Feedback Copyright © 2008, Texas Instruments Incorporated