VerilogHDL建模基础与技巧探索

需积分: 9 41 浏览量

更新于2024-07-24

收藏 8.61MB PDF 举报

"VerilogHDL那些事儿_建模篇(for DB4CE15).pdf,一本由黑金动力社区荣誉出品的教程,旨在帮助初学者理解和掌握VerilogHDL建模技术在FPGA设计中的应用。"

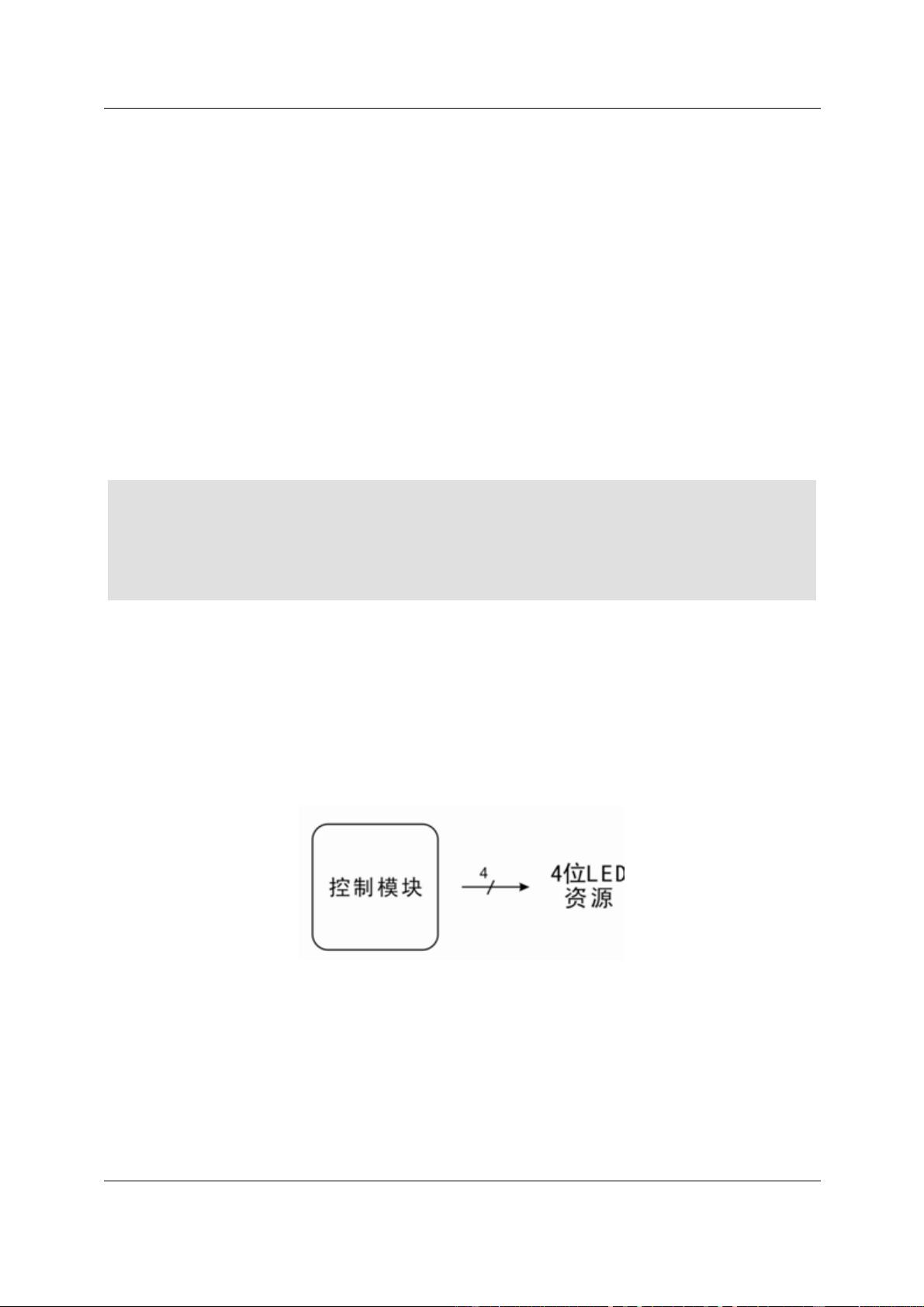

VerilogHDL是一种硬件描述语言,广泛用于数字系统的建模和设计,特别是在FPGA(Field-Programmable Gate Array)领域。建模是VerilogHDL的核心概念,意味着使用该语言创建逻辑模块,就像用乐高积木构建结构一样,VerilogHDL是实现FPGA逻辑设计的工具。

在学习VerilogHDL的过程中,建模技巧的重要性不言而喻。然而,许多初学者往往在面对复杂的源代码和抽象的设计概念时感到困惑,难以将理论与实践相结合。"建模篇"强调了理解并掌握建模方法对于有效使用VerilogHDL至关重要。书中提到,建模不仅需要理解RTL(Register Transfer Level)代码,还需要能读懂并理解他人的代码设计,而这通常是一个挑战,因为缺乏建模技巧可能导致理解上的困难。

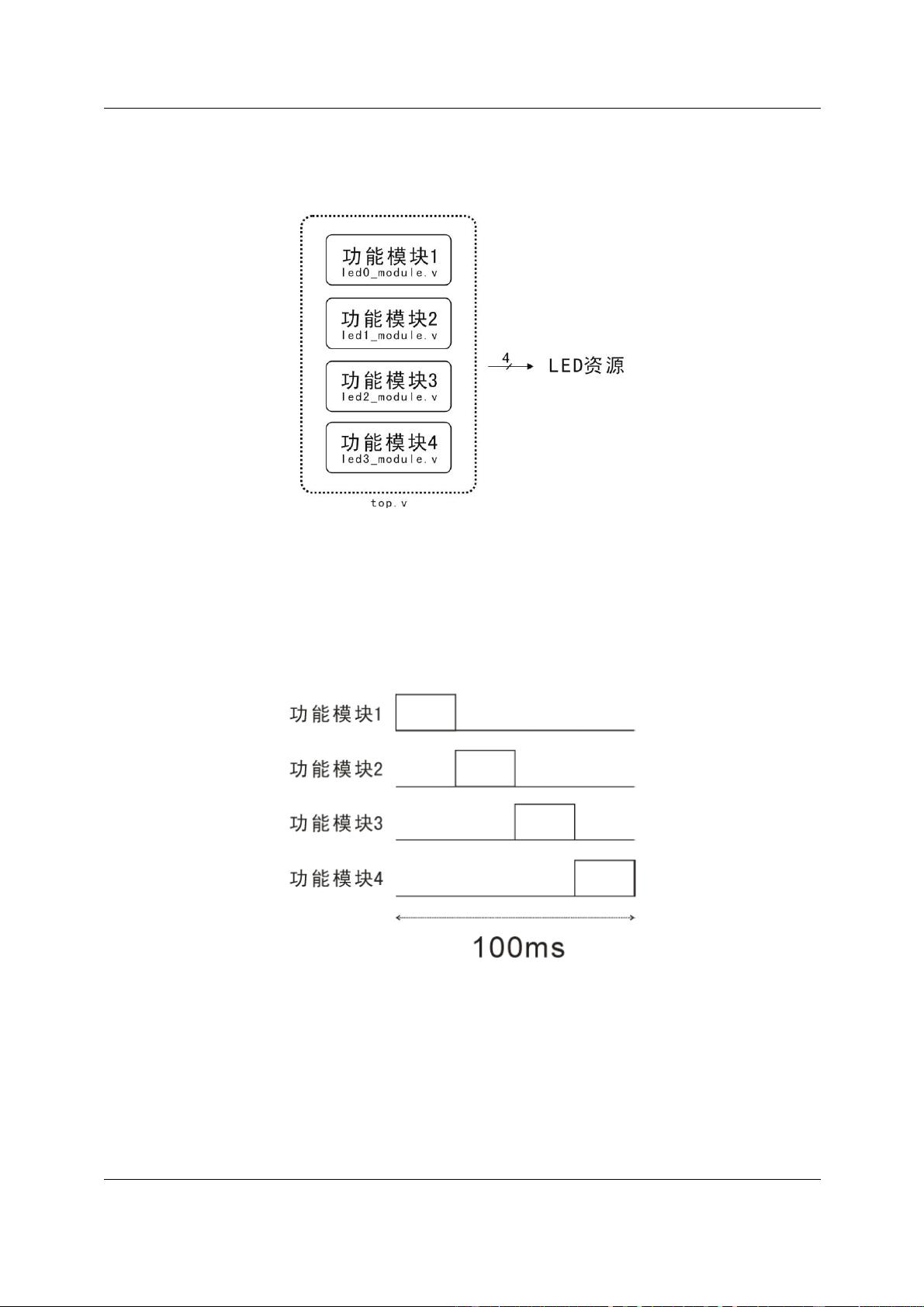

作者指出,良好的建模技巧包括清晰的模块划分、逻辑结构的组织以及代码的可读性。设计应该易于理解,即使对他人来说也是如此,这要求代码整齐、表达直接。建模的结构化有助于提高设计效率和可维护性,这是比时序分析和功能仿真更基础但同样关键的技能。作者坚信,通过掌握建模技巧,VerilogHDL能够展现出与其他高级编程语言相媲美,甚至超越它们的潜力。

对于那些在VerilogHDL和FPGA学习过程中挣扎的人来说,问题通常在于没有掌握好建模这个基础。本书《VerilogHDL那些事儿-建模篇》试图填补这一空白,提供实用的指导,帮助初学者克服难关,从理论过渡到实际操作,从而更好地运用VerilogHDL进行FPGA设计。通过深入探讨建模的各个方面,读者可以期待提升自己的建模能力,进而更加自如地在FPGA设计领域游刃有余。

114 浏览量

2018-05-03 上传

2019-07-11 上传

275 浏览量

483 浏览量

357 浏览量

108 浏览量

414 浏览量

2024-09-15 上传

skyer2012

- 粉丝: 5

最新资源

- WebLogic Server 安装与配置教程

- Groovy编程入门:从基础到高级

- MyEclipse 6 Java开发入门教程:Struts2+Spring+Hibernate实战

- C/C++算法入门:基础与图论详解

- Eclipse IDE基础教程:平台、视图与工作区解析

- Eclipse IDE基础教程:从入门到精通

- SoftICE调试工具使用指南

- 常用 Shell 命令大全:文件操作、目录切换、文件查看

- ARM架构详解:300问解析

- 电子商务系统图解:实现交易与管理的全流程

- 延迟抢占策略的实时调度算法在多媒体通信中的应用

- NMAKE解析与MAKEFILE入门教程

- Apache2.2与Tomcat5.5整合配置JSP环境

- 程序设计实践:打造易读易维护的高效代码

- Eclipse IDE基础教程:工作台、编辑器与视图解析

- Excel VBA实用代码集锦