FPGA实现的数字幅频均衡功率放大器设计

197 浏览量

更新于2024-08-30

2

收藏 371KB PDF 举报

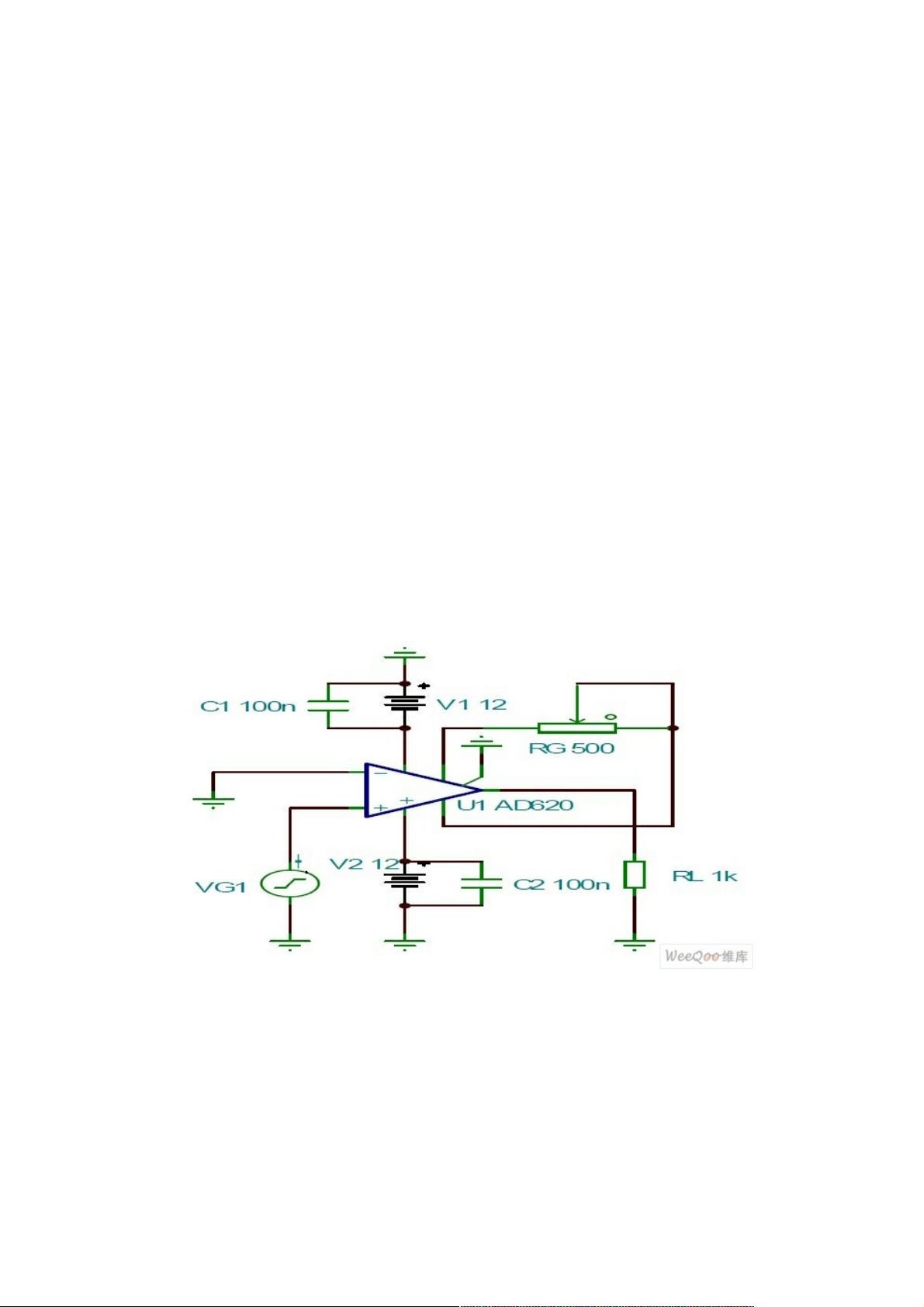

"该文提出了一种基于FPGA的数字幅频均衡功率放大器设计方案,旨在解决现代通信系统中的码间干扰问题,提高通信质量。系统由小信号放大、带阻网络衰减、数字信号均衡处理和功率放大四部分组成。小信号放大采用AD620,后级功率放大采用分立MOS管。通过FIR滤波算法设计滤波器以实现幅频均衡。硬件设计包括AD620的前置放大电路设计和阻带网络的计算。"

在通信系统中,尤其是在高速数据传输中,码间干扰(ISI,Inter-Symbol Interference)是一个普遍存在的问题,它使得信号在经过信道传输后,相邻符号之间产生相互影响,导致解码错误,降低了通信的可靠性。为了解决这个问题,均衡器被引入到接收端,通过对信号进行适当的补偿来消除或减小码间干扰。

本解决方案的核心在于基于FPGA的数字幅频均衡功率放大器。FPGA(Field-Programmable Gate Array)因其可编程性、灵活性和高性能而被广泛应用于数字信号处理领域。在这个设计中,FPGA承担了数字信号的均衡处理任务,通过FIR(Finite Impulse Response)滤波算法来校正信号的幅频特性,实现对信号的频率域均衡,从而改善系统的误码率性能。

硬件电路设计包括两个关键部分:前置放大电路和带阻网络。前置放大电路采用AD620,这是一种低功耗、高精度的仪表运算放大器,通过调节可变电阻RG来调整增益,以满足信号放大需求。带阻网络的设计则依据幅频特性和基尔霍夫定律来确定元件值,以实现特定频率范围内的信号衰减,有助于进一步优化信号质量。

在功率放大阶段,采用分立MOS管构建功率放大电路,这种设计方法可以提供较高的输出功率,同时具有良好的线性度和效率,适应不同负载条件下的工作需求。

该设计方案综合考虑了信号放大、频率响应均衡和功率输出等多个方面,通过FPGA的数字处理能力和精心设计的硬件电路,有效地解决了码间干扰问题,提高了通信系统的整体性能。这一技术在无线通信、有线通信以及其他需要高数据速率传输的应用中具有重要的实践价值。

188 浏览量

点击了解资源详情

点击了解资源详情

171 浏览量

103 浏览量

103 浏览量

102 浏览量

点击了解资源详情

点击了解资源详情

weixin_38713717

- 粉丝: 6

最新资源

- DeepFreeze密码移除工具6.x版本使用教程

- MQ2烟雾传感器无线报警器项目解析

- Android实现消息推送技术:WebSocket的运用解析

- 利用jQuery插件自定义制作酷似Flash的广告横幅通栏

- 自定义滚动时间选择器,轻松转换为Jar包

- Python环境下pyuvs-rt模块的使用与应用

- DLL文件导出函数查看器 - 查看DLL函数名称

- Laravel框架深度解析:开发者的创造力与学习资源

- 实现滚动屏幕背景固定,提升网页高端视觉效果

- 遗传算法解决0-1背包问题

- 必备nagios插件压缩包:实现监控的关键

- Asp.Net2.0 Data Tutorial全集深度解析

- Flutter文本分割插件flutter_break_iterator入门与实践

- GD Spi Flash存储器的详细技术手册

- 深入解析MyBatis PageHelper分页插件的使用与原理

- DELPHI实现斗地主游戏设计及半成品源码分析