Allegro PCB设计教程:从网表导入到约束管理

需积分: 14 93 浏览量

更新于2024-09-07

收藏 301KB DOC 举报

"allegro_PCB设计笔记详细记录了如何导入ORCAD网络表,使用quickplace放置器件,以及约束管理器中bus、flat nets、schematic nets的设置和原理图与PCB设计间的关联处理。"

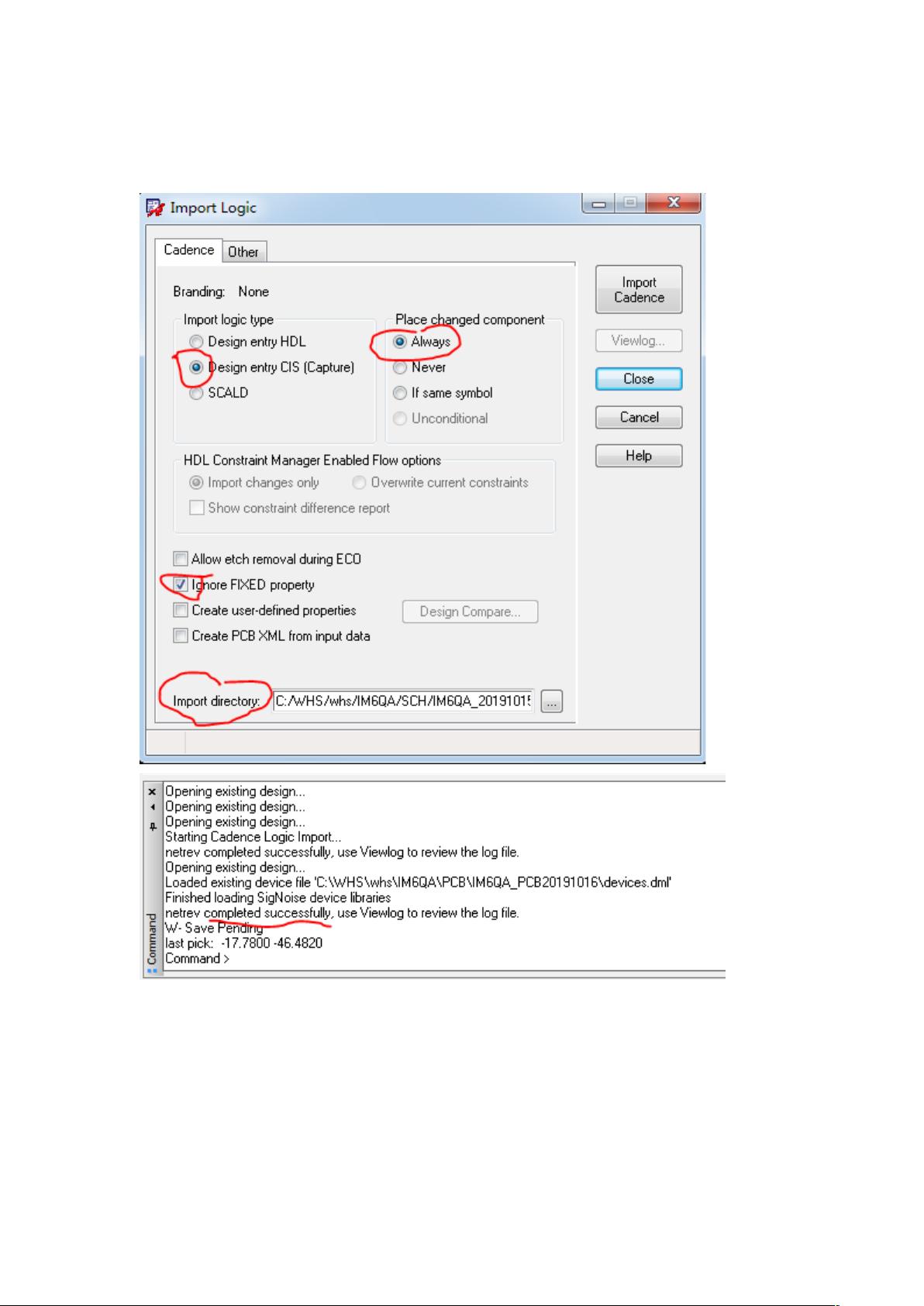

在Allegro PCB设计过程中,导入ORCAD网络表是一个重要的步骤,它允许设计师将原理图的信息同步到PCB布局中。通过File菜单选择Import,然后选择Logic,可以导入网络表。在完成设置并点击"Import"后,系统会在命令框中显示导入成功的提示信息。

快速放置器件是提高设计效率的关键。在Place菜单中选择Quickplace,点击'Place'按钮,然后完成器件放置。放置完成后,别忘了点击“OK”来确认位置。这样可以确保器件正确无误地被放置在PCB设计上。

当原理图中的器件属性包含SIGNAL_MODEL时,导入PCB后约束管理器会自动生成xnet,这是因为在原理图中定义了串阻、串容、串感型网络。如果不想让这些xnet出现,可以删除SIGNAL_MODEL属性,重新导入网表。同样,如果在schematic nets或flat nets中添加了BUS_NAME和DIFFERENTIAL_PAIR,约束管理器会识别出bus和差分对。删除这些属性后,需手动添加。

原理图的更改会影响到PCB设计的约束管理器。如果在PCB中已经设置好的netgroup、xnet等不会因导入新网表而被更改或删除,但原理图中的bus或差分对如果在约束管理器中被删除,再次导入网表时,这些设置会重新出现在约束管理器中。此外,即使在原理图中删除了差分对,约束管理器中仍然保留,这表明约束管理器会增加原理图中新增的约束,但不会删除已存在的约束。

创建差分对可以在原理图中进行,如通过所示的界面创建,差分对的名称将直接应用于约束管理器。而在Allegro 16.6版本中,无法直接创建bus,但可以通过原理图生成。这使得设计者能够在原理图层面设定好bus结构,然后在导入到PCB时自动生成对应的约束。

总结来说,Allegro PCB设计笔记详尽地阐述了如何有效地管理网络表导入、器件放置以及约束设置,强调了原理图与PCB设计之间的交互,并提供了处理bus、差分对等复杂网络关系的方法,对于进行Allegro PCB设计的工程师来说,是一份非常实用的参考资料。

2020-04-16 上传

2020-04-16 上传

2019-11-07 上传

2021-11-12 上传

2021-09-29 上传

2021-09-02 上传

2019-12-23 上传

2022-07-15 上传

2021-11-04 上传

liehuoyaoche

- 粉丝: 6

- 资源: 42

最新资源

- Android圆角进度条控件的设计与应用

- mui框架实现带侧边栏的响应式布局

- Android仿知乎横线直线进度条实现教程

- SSM选课系统实现:Spring+SpringMVC+MyBatis源码剖析

- 使用JavaScript开发的流星待办事项应用

- Google Code Jam 2015竞赛回顾与Java编程实践

- Angular 2与NW.js集成:通过Webpack和Gulp构建环境详解

- OneDayTripPlanner:数字化城市旅游活动规划助手

- TinySTM 轻量级原子操作库的详细介绍与安装指南

- 模拟PHP序列化:JavaScript实现序列化与反序列化技术

- ***进销存系统全面功能介绍与开发指南

- 掌握Clojure命名空间的正确重新加载技巧

- 免费获取VMD模态分解Matlab源代码与案例数据

- BuglyEasyToUnity最新更新优化:简化Unity开发者接入流程

- Android学生俱乐部项目任务2解析与实践

- 掌握Elixir语言构建高效分布式网络爬虫