没有合适的资源?快使用搜索试试~ 我知道了~

首页Apple Macbook Pro A1226 技术规格与内容目录

Apple Macbook Pro A1226 技术规格与内容目录

需积分: 5 0 下载量 112 浏览量

更新于2024-06-18

收藏 1.76MB PDF 举报

"Apple Macbook Pro A1226 (Oroya M75 DVT).pdf 是一份关于苹果Macbook Pro型号为A1226的详细设计图纸,涵盖了多个表格目录项,可能包括了硬件组件、结构设计、电路布局等多个方面的内容。"

这份PDF文档很可能是针对苹果公司早期型号的Macbook Pro A1226进行的开发验证测试(DVT,Development Verification Test)阶段的图纸资料。Oroya M75可能是这款设备的一个特定配置或者内部代号,通常这样的命名方式在产品开发过程中用于区分不同的版本或迭代。

苹果Macbook Pro系列以其高性能和出色的工业设计著称,A1226型号的设备可能会包含以下关键知识点:

1. **硬件规格**:图纸中可能详细列出了该型号的硬件配置,如处理器类型(可能是Intel Core 2 Duo或更早的型号),内存大小,硬盘容量,显卡信息等。

2. **设计细节**:Macbook Pro的外壳材质、尺寸、重量、接口布局,以及屏幕分辨率等都可能在图纸中有详尽的标注。

3. **电路布局**:电路设计对于任何电子设备都是至关重要的,图纸可能展示了主板布局,电源管理,信号路径,散热设计等,这些都是确保设备稳定运行的关键部分。

4. **连接器和接口**:包括USB,FireWire,HDMI,DisplayPort,MagSafe充电端口,耳机插孔等的规格和位置。

5. **散热系统**:Macbook Pro的散热设计是其性能表现的关键,图纸会详细描绘风扇、散热片和热管的布局。

6. **电池设计**:对于笔记本电脑来说,电池的容量和续航时间是用户关心的重点,图纸将揭示电池的形状、容量和安装位置。

7. **内部结构**:硬盘、内存、无线模块等的安装位置和更换方法,对于维修和升级来说非常重要。

8. **兼容性和认证**:可能包含各种安全和电磁兼容性(EMC)的合规信息,确保产品满足全球不同市场的标准。

由于没有提供具体的图纸内容,以上分析基于一般的产品设计流程和苹果产品的常规特性进行推测。实际的图纸内容可能会更加详细,包括每个部件的精确尺寸、材料规格、生产流程图、测试要求等,这些信息对于工程师、技术人员和DIY爱好者来说都是非常有价值的参考资料。

IN

IN

OUT

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

BI

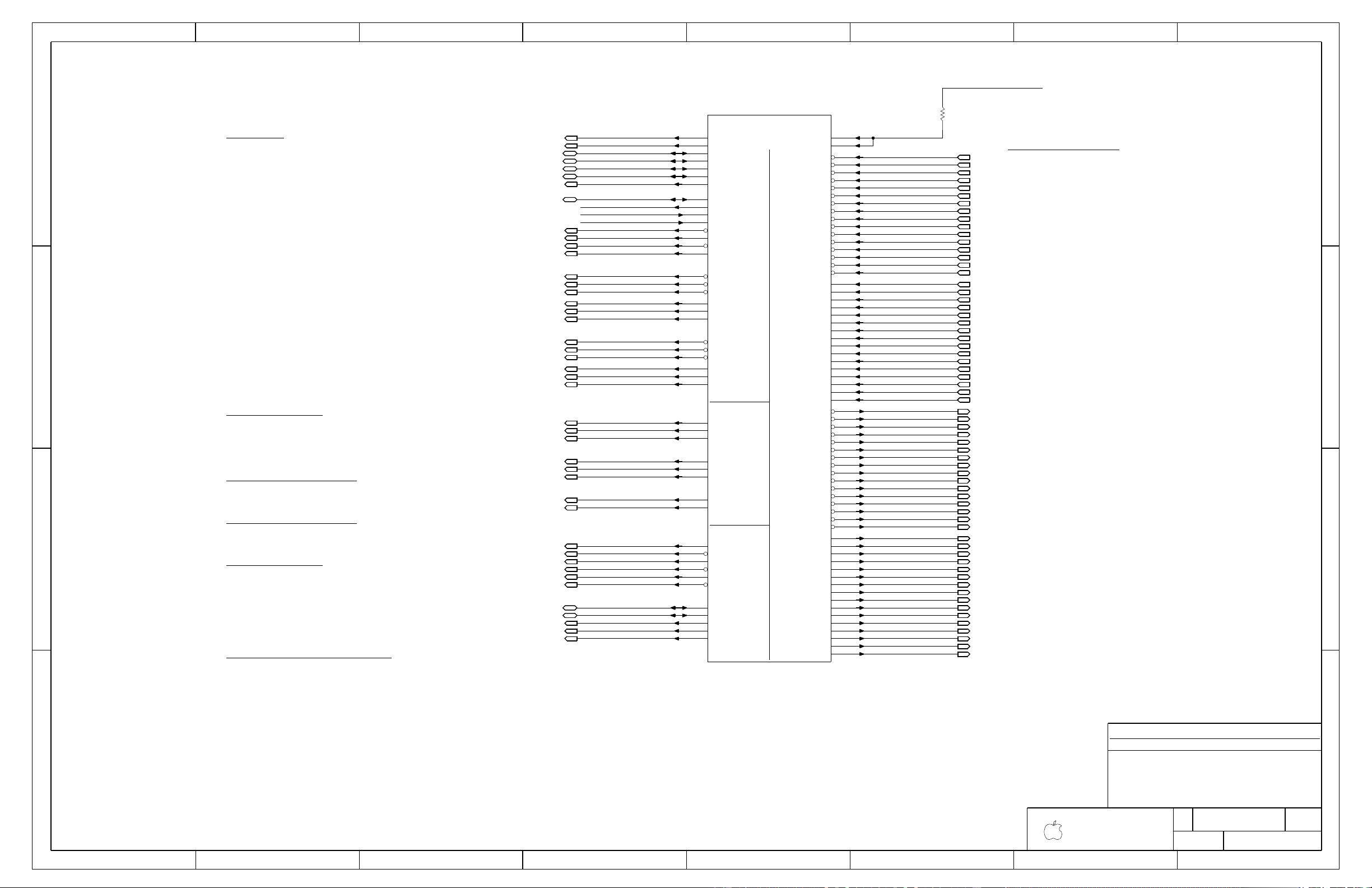

L_BKLT_CTRL

L_VDD_EN

PEG_TX15*

PEG_TX14*

PEG_TX13*

PEG_TX12*

PEG_TX11*

PEG_TX10*

PEG_TX9*

PEG_TX8*

PEG_TX7*

PEG_TX6*

PEG_TX5*

PEG_TX4*

PEG_TX3*

PEG_TX2*

PEG_TX1*

PEG_TX0*

PEG_TX15

PEG_TX14

PEG_TX13

PEG_TX12

PEG_TX11

PEG_TX10

PEG_TX9

PEG_TX8

PEG_TX7

PEG_TX6

PEG_TX5

PEG_TX4

PEG_TX3

PEG_TX2

PEG_TX1

PEG_TX0

PEG_RX14

PEG_RX15*

PEG_RX14*

PEG_RX13*

PEG_RX12*

PEG_RX11*

PEG_RX15

PEG_RX13

PEG_RX12

PEG_RX11

PEG_RX10

PEG_RX9

PEG_RX8

PEG_RX7

PEG_RX6

PEG_RX5

PEG_RX4

PEG_RX3

PEG_RX2

PEG_RX1

PEG_RX0

PEG_RX10*

PEG_RX9*

PEG_RX8*

PEG_RX7*

PEG_RX6*

PEG_RX5*

PEG_RX4*

PEG_RX3*

PEG_RX2*

PEG_RX1*

PEG_RX0*

PEG_COMPI

PEG_COMPO

CRT_DDC_DATA

L_CTRL_DATA

LVDSB_DATA1

LVDSB_DATA2

LVDSB_DATA0

LVDSB_DATA2*

LVDSB_DATA1*

LVDSB_DATA0*

LVDSA_DATA2

LVDSA_DATA0

LVDSA_DATA1

LVDSB_CLK*

LVDS_VREFL

LVDS_IBG

TVC_RTN

TVA_RTN

TVB_RTN

TVC_DAC

TVB_DAC

TVA_DAC

CRT_RED*

CRT_RED

CRT_GREEN*

CRT_GREEN

CRT_BLUE*

CRT_BLUE

CRT_VSYNC

CRT_TVO_IREF

CRT_HSYNC

CRT_DDC_CLK

L_BKLT_EN

L_DDC_CLK

TV_DCONSEL0

TV_DCONSEL1

LVDSA_DATA2*

L_DDC_DATA

LVDSA_DATA1*

LVDSA_DATA0*

LVDSB_CLK

LVDSA_CLK

LVDSA_CLK*

LVDS_VREFH

L_CTRL_CLK

LVDS_VBG

VGA

TV

LVDS

(3 OF 10)

PCI-EXPRESS GRAPHICS

BI

BI

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

rails must be filtered except for VCCA_CRT.

Tie DPLL_REF_CLK* and DPLL_REF_SSCLK* to VCC (VCore).

S-Video: DACB & DACC only

share filtering with VCCA_CRT_DAC.

Tie R/R#/G/G#/B/B#, HSYNC and VSYNC to GND.

Tie TVx_DAC, TVx_RTN, R/R#/G/G#/B/B#, HSYNC,

CRT & TV-Out Disable

All CRT/TVDAC rails must be powered. All

VCCA_CRT_DAC, VCCA_DAC_BG, VCCA_TVx_DAC,

VCCD_CRT, VCCD_QDAC and VCC_SYNC.

NOTE: Must keep VDDC_TVDAC powered

and filtered at all times!

Internal Graphics Disable

Follow instructions for LVDS and CRT & TV-Out Disable above.

TV_DCONSELx to GND.

Can also tie CRT_DDC_*, L_CTRL_*, L_DDC_*, SDVO_CTRL_* and

Tie DPLL_REF_CLK and DPLL_REF_SSCLK to GND.

Tie VCCA_DPLLA and VCCA_DPLLB to VCC (VCore).

Tie VCC_AXG and VCC_AXG_NCTF to GND.

Leave GFX_VID<3..0> and GFX_VR_EN as NC.

Tie TVx_DAC and TVx_RTN to GND. Must power all

TV-Out Disable / CRT Enable

CRT Disable / TV-Out Enable

VSYNC and CRT_TVO_IREF to GND.

Can tie the following rails to GND:

TV-Out Signal Usage:

Composite: DACA only

Component: DACA, DACB & DACC

TVDAC rails. VCCA_TVx_DAC and VCCA_DAC_BG can

LVDS Disable

SDVOC_RED

SDVOC_GREEN

SDVOC_BLUE

SDVOC_CLKP

SDVOB_BLUE

SDVOB_CLKP

SDVOB_RED#

SDVOB_GREEN#

SDVOB_BLUE#

SDVOB_CLKN

SDVOC_RED#

SDVOC_GREEN#

SDVOC_BLUE#

SDVOC_CLKN

SDVOB_RED

SDVOB_GREEN

SDVO_FLDSTALL

SDVO_INT

SDVO_TVCLKIN

SDVO_INT#

SDVO_TVCLKIN#

SDVO Alternate Function

SDVO_FLDSTALL#

Tie VCC_TX_LVDS and VCCA_LVDS to GND.

decoupling. Otherwise, tie VCCD_LVDS to GND also.

Can leave all signals NC if LVDS is not implemented.

Unused DAC outputs must remain powered, but can

omit filtering components. Unused DAC outputs

should connect to GND through 75-ohm resistors.

If SDVO is used, VCCD_LVDS must remain powered with proper

Note: SR DG says to tie LVDS_VREFH/L to GND. This causes

a glitch during wake-up on LVDS DATA/CLK pairs. New

recommendation is to float both signals, see Radar #5067636.

66 80

66 80

R1510

1

2

24.9

1%

1/16W

MF-LF

402

77

66 80

66 80

22 80

U1400

H32

G32

K33

G35

K29

J29

F33

F29

E29

C32

E33

J40

H39

E39

E40

C37

D35

K40

L41

L43

N41

N40

C45

D46

G50

G51

E50

E51

F48

F49

E42

D44

E44

G44

A47

B47

A45

B45

N43

M43

J50

J51

L50

L51

AC45

AD44

AC41

AD40

AH47

AG46

AG49

AH49

AH45

AG45

AG42

AG41

M47

N47

U44

T45

T49

T50

T41

U40

W45

Y44

W41

Y40

AB50

AB51

Y48

W49

M45

N45

T38

U39

AD47

AC46

AC50

AC49

AD43

AC42

AG39

AH39

AE50

AE49

AH43

AH44

T46

U47

N50

N51

R51

R50

U43

T42

W42

Y43

Y47

W46

Y39

W38

AC38

AD39

M35

P33

E27

F27

G27

J27

K27

L27

FCBGA

CRESTLINE

OMIT

13

13

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

66 80

77

77

66 80

75 77

75 77

77 80

77 80

77 80

77 80

77 80

77 80

66 80

77 80

77 80

77 80

77 80

77 80

77 80

77 80

77 80

77 80

77 80

66 80

SYNC_MASTER=T9_NOME

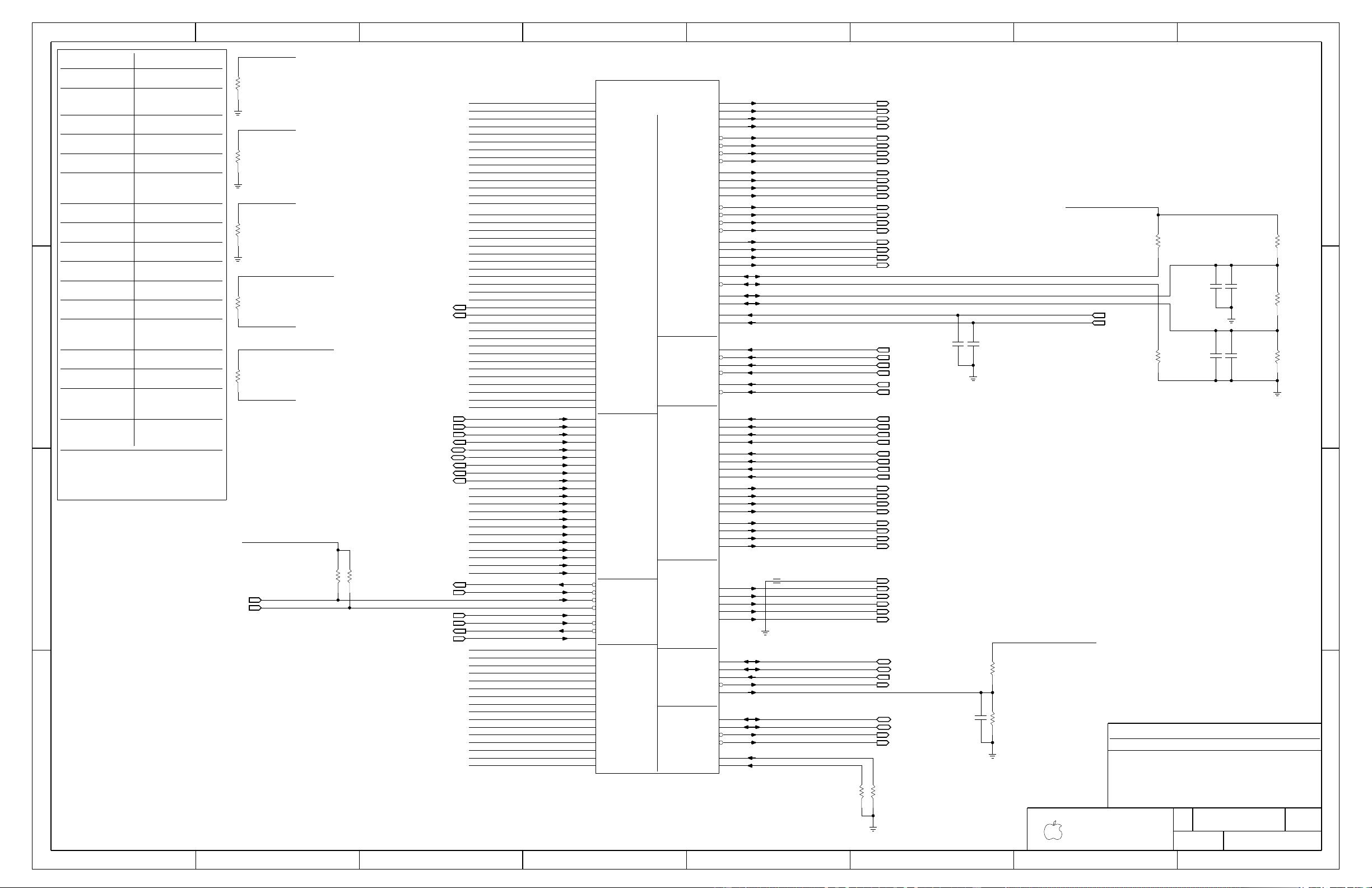

NB PEG / Video Interfaces

051-7225

14.0.0

8815

SYNC_DATE=03/16/2007

LVDS_BKLT_CTL

LVDS_VDD_EN

PEG_R2D_C_N<15>

PEG_R2D_C_N<14>

PEG_R2D_C_N<13>

PEG_R2D_C_N<12>

PEG_R2D_C_N<11>

PEG_R2D_C_N<10>

PEG_R2D_C_N<9>

PEG_R2D_C_N<8>

PEG_R2D_C_N<7>

PEG_R2D_C_N<6>

PEG_R2D_C_N<5>

PEG_R2D_C_N<4>

PEG_R2D_C_N<3>

PEG_R2D_C_N<2>

PEG_R2D_C_N<1>

PEG_R2D_C_N<0>

PEG_R2D_C_P<15>

PEG_R2D_C_P<14>

PEG_R2D_C_P<13>

PEG_R2D_C_P<12>

PEG_R2D_C_P<11>

PEG_R2D_C_P<10>

PEG_R2D_C_P<9>

PEG_R2D_C_P<8>

PEG_R2D_C_P<7>

PEG_R2D_C_P<6>

PEG_R2D_C_P<5>

PEG_R2D_C_P<4>

PEG_R2D_C_P<3>

PEG_R2D_C_P<2>

PEG_R2D_C_P<1>

PEG_R2D_C_P<0>

PEG_D2R_P<14>

PEG_D2R_N<15>

PEG_D2R_N<14>

PEG_D2R_N<13>

PEG_D2R_N<12>

PEG_D2R_N<11>

PEG_D2R_P<15>

PEG_D2R_P<13>

PEG_D2R_P<12>

PEG_D2R_P<8>

PEG_D2R_P<7>

PEG_D2R_P<6>

PEG_D2R_P<5>

PEG_D2R_P<4>

PEG_D2R_P<3>

PEG_D2R_P<2>

PEG_D2R_P<1>

PEG_D2R_P<0>

PEG_D2R_N<10>

PEG_D2R_N<9>

PEG_D2R_N<8>

PEG_D2R_N<7>

PEG_D2R_N<5>

PEG_D2R_N<4>

PEG_D2R_N<3>

PEG_D2R_N<2>

PEG_D2R_N<0>

PEG_COMP

GND

LVDS_B_DATA_P<1>

LVDS_B_DATA_P<2>

LVDS_B_DATA_P<0>

LVDS_B_DATA_N<0>

LVDS_A_DATA_P<2>

LVDS_A_DATA_P<0>

LVDS_A_DATA_P<1>

LVDS_B_CLK_N

NC_LVDS_VREFL

LVDS_IBG

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

LVDS_BKLT_EN

LVDS_CONN_DDC_CLK

GND

GND

LVDS_A_DATA_N<2>

LVDS_CONN_DDC_DATA

LVDS_A_DATA_N<1>

LVDS_A_DATA_N<0>

LVDS_B_CLK_P

LVDS_A_CLK_P

LVDS_A_CLK_N

NC_LVDS_VREFH

PEG_D2R_N<6>

PEG_D2R_N<1>

PP1V05_S0_NB_VCCPEG

PEG_D2R_P<10>

PEG_D2R_P<11>

PEG_D2R_P<9>

TP_LVDS_VBG

LVDS_CTRL_CLK

LVDS_CTRL_DATA

LVDS_B_DATA_N<1>

LVDS_B_DATA_N<2>

GND

GND

21

22

22

19

IN

IN

CLKREQ*

NC1

NC8

CL_CLK

CL_PWROK

CL_RST*

RSVD6

THERMTRIP*

PM_BM_BUSY*

RSVD4

RSVD3

RSVD7

SM_CKE1

SM_CK0*

SM_CKE0

SM_ODT0

SM_ODT2

SM_RCOMP

SM_RCOMP*

SM_VREF0

SM_VREF1

SM_RCOMP_VOL

SM_CS1*

SM_CS0*

RSVD14

RSVD11

RSVD10

RSVD9

RSVD5

RSVD8

RSVD2

DPLL_REF_CLK*

DPLL_REF_SSCLK

PEG_CLK

DMI_RXN1

DMI_RXN0

DMI_RXN3

DMI_RXN2

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_TXN0

DMI_RXP3

DMI_TXN2

DMI_TXN1

DMI_TXP0

DMI_TXN3

DMI_TXP1

DMI_TXP2

DMI_TXP3

PEG_CLK*

RSVD12

CL_DATA

CL_VREF

SDVO_CTRL_CLK

SDVO_CTRL_DATA

ICH_SYNC*

TEST1

TEST2

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VR_EN

GFX_VID3

RSVD20

RSVD21

RSVD24

RSVD25

RSVD27

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD41

RSVD42

RSVD40

RSVD43

RSVD44

RSVD45

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG16

CFG15

CFG14

CFG17

CFG18

CFG19

CFG20

PM_DPRSTP*

PM_EXT_TS0*

PWROK

PM_EXT_TS1*

RSTIN*

DPRSLPVR

NC2

NC4

NC3

NC5

NC7

NC6

NC10

NC9

NC12

NC11

NC13

NC14

NC15

NC16

DPLL_REF_CLK

SM_RCOMP_VOH

SM_ODT3

SM_ODT1

RSVD13

SM_CS2*

SM_CS3*

SM_CK3

SM_CK4

SM_CK4*

SM_CKE3

RSVD1

SM_CKE4

DPLL_REF_SSCLK*

SM_CK3*

SM_CK1*

SM_CK1

SM_CK0

SA_MA14

RSVD22

RSVD23

RSVD26

SB_MA14

SM_CK2

SM_CK2*

SM_CK5

SM_CK5*

(2 OF 10)

RSVD

DDR MUXING

CLK

CFG

DMI

PM

GRAPHICS VID

ME

MISC

NC

OUT

OUT

OUT

OUT

OUT

BI

BI

IN

OUT

BI

BI

OUT

OUT

IN

IN

OUT

OUT

OUT

IN

IN

IN

OUT

OUT

OUT

OUT

BI

OUT

BI

OUT

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

NB CFG<8:0> used for debug access

IPU

IPU

NB_CFG<4>

NB_CFG<5>

DMI x2 Select

NOTE: GMCH CL_PWROK input must be PWRGD signal for

PP3V3_S0M, PP3V3_S0MWOL, PP1V8_S3M, PP1V25_S0M,

If ME/AMT is not used, short CL_PWROK to PWROK.

PP1V05_S0M, PP0V9_S3M and PP0V9_S0M.

NB_CFG<18>

NB_CFG<15>

FSB Dynamic

ODT

NB_CFG<17>

NB_CFG<14>

NB_CFG<16>

NB_CFG<11>

NB_CFG<12>

NB_CFG<13>

DMI Lane

Reversal

SDVO/PCIe x1

Concurrent

NB_CFG<20>

NB_CFG<19>

00 = RESERVED

or PCIe x16

11 = Normal Operation

High = Reversed

Low = Only SDVO

NB_CFG<13:12>

High = Both active

Low = Normal

01 = XOR Mode Enabled

10 = All-Z Mode Enabled

High = Enabled

Low = Disabled

See Below

See Below

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

Lane Reversal

PCIe Graphics

NB_CFG<9>

NB_CFG<10>

Low = Reversed

High = Normal

RESERVED

RESERVED

RESERVED

NB_CFG<7>

High = DMIx4

NB_CFG<6>

RESERVED

IPU

Clk used for PEG and DMI

IPD

IPD

IPD

IPU

IPU

IPU

IPU

IPU

IPU

IPU

IPU

IPU

IPU

NB_CFG<8>

NB_CFG<3>

Low = DMIx2

RESERVED

RESERVED

IPU

IPU

NB CFG<13:12> require ICT access

7

28

8

16 31 32 62

C1616

1

2

10V

0.1uF

20%

CERM

402

C1615

1

2

10V

0.1uF

20%

CERM

402

U1400

P27

N27

R24

L23

J23

E23

E20

K23

M20

M24

L32

N33

N24

L35

C21

C23

F23

N23

G23

J20

C20

AM49

AK50

AT43

AN49

AM50

G39

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

B42

C42

H48

H47

G36

E35

A39

C38

B39

E36

G40

BJ51

E1

A5

C51

B50

A50

A49

BK2

BK51

BK50

BL50

BL49

BL3

BL2

BK1

BJ1

K44

K45

G41

L39

L36

J36

AW49

AV20

P36

AR37

AM36

AL36

AM37

D20

P37

H10

B51

BJ20

BK22

BF19

BH20

BK18

BJ18

R35

BH39

AW20

BK20

C48

D47

B44

N35

C44

A35

B37

B36

B34

C34

AR12

AR13

AM12

AN13

J12

BJ29

BE24

H35

K36

AV29

AW30

BB23

BA23

BF23

BG23

BA25

AW25

AV23

AW23

BC23

BD24

BE29

AY32

BD39

BG37

BG20

BK16

BG16

BE13

BH18

BJ15

BJ14

BE16

BL15

BK14

BK31

BL31

AR49

AW4

A37

R32

N20

OMIT

FCBGA

CRESTLINE

9

9

9

9

9

59

25 83

25 83

7 9

16 28 58

25 83

7

29

7

25

R1691

1

2

5%

1/16W

MF-LF

20K

402

R1690

1

2

5%

1/16W

MF-LF

0

402

7

25 58 79

32 45

R1631

1

2

1/16W

5%

MF-LF

10K

402

C1625

1

2

402

CERM

16V

10%

0.01UF

C1624

1

2

20%

CERM1

6.3V

2.2UF

603

R1624

1

2

402

1/16W

1%

MF-LF

1K

R1622

1

2

3.01K

MF-LF

1/16W

1%

402

C1622

1

2

20%

2.2UF

CERM1

6.3V

603

C1623

1

2

402

CERM

16V

10%

0.01UF

R1620

1

2

MF-LF

1%

1/16W

402

1K

R1641

1

2

1%

1/16W

MF-LF

392

402

R1640

1

2

1%

1K

1/16W

MF-LF

402

C1640

1

2

0.1uF

CERM

10V

20%

402

R1655

1

2

NBCFG_DMI_X2

1/16W

MF-LF

3.9K

5%

402

R1659

1

2

NBCFG_PEG_REVERSE

3.9K

MF-LF

1/16W

5%

402

R1666

1

2

MF-LF

5%

1/16W

3.9K

NBCFG_DYN_ODT_DISABLE

402

R1669

1

2

NBCFG_DMI_REVERSE

5%

1/16W

MF-LF

3.9K

402

R1670

1

2

NBCFG_SDVO_AND_PCIE

3.9K

MF-LF

1/16W

5%

402

31 33 81

32 33 81

13 30 79

13 30 79

13 30 79

13

13

13

13

13 16

25

13

10 23 46 79

31 45

7

10 23 58 79

7 9

16 28 58

31 81

32 81

32 81

31 81

31 81

32 81

32 81

31 81

31 33 81

31 33 81

32 33 81

31 33 81

32 33 81

31 33 81

32 33 81

32 33 81

31 33 81

31 33 81

32 33 81

32 33 81

R1610

1

2

402

20

1%

1/16W

MF-LF

R1611

1

2

402

20

MF-LF

1%

1/16W

8

16 31 32 62

7

29 30 84

7

29 30 84

8

18 21 22 50

7

22 29 30 84

7

22 29 30 84

24 80

24 80

24 80

24 80

24 80

24 80

24 80

24 80

24 80

24 80

24 80

24 80

24 80

24 80

24 80

24 80

R1630

1

2

10K

5%

1/16W

MF-LF

402

NB Misc Interfaces

SYNC_DATE=03/16/2007

SYNC_MASTER=T9_NOME

16 88

14.0.0

051-7225

TP_LVDS_A_DATAP3

TP_NB_RSVD<34>

MEM_B_A<14>

TP_NB_RSVD<27>

TP_NB_RSVD<26>

TP_NB_RSVD<25>

NB_CLK100M_DPLLSS_P

NB_CLK100M_DPLLSS_N

NB_BSEL<0>

NB_CFG<5>

MEM_CKE<4>

TP_NB_RSVD<1>

MEM_CLK_P<0>

MEM_CLK_N<4>

MEM_CLK_N<3>

MEM_CLK_P<4>

MEM_CLK_P<3>

TP_NB_RSVD<13>

TP_NB_NC<16>

TP_NB_NC<15>

TP_NB_NC<14>

TP_NB_NC<13>

TP_NB_NC<11>

TP_NB_NC<12>

TP_NB_NC<9>

TP_NB_NC<10>

TP_NB_NC<6>

TP_NB_NC<7>

TP_NB_NC<5>

TP_NB_NC<3>

TP_NB_NC<2>

PM_EXTTS_L<0>

NB_CFG<20>

NB_CFG<19>

TP_NB_CFG<18>

TP_NB_CFG<14>

TP_NB_CFG<15>

NB_CFG<16>

TP_NB_CFG<12>

TP_NB_CFG<10>

TP_NB_RSVD<41>

TP_NB_RSVD<23>

TP_NB_RSVD<22>

TP_NB_RSVD<21>

TP_NB_RSVD<20>

NB_TEST2

NB_TEST1

TP_NB_RSVD<2>

TP_NB_RSVD<8>

TP_NB_RSVD<9>

TP_NB_RSVD<10>

TP_NB_RSVD<11>

MEM_CS_L<0>

MEM_CS_L<1>

MEM_CKE<0>

MEM_CLK_N<1>

MEM_CLK_P<1>

MEM_CLK_N<0>

TP_NB_RSVD<7>

TP_NB_RSVD<3>

TP_NB_RSVD<4>

TP_NB_NC<8>

TP_NB_NC<1>

GND

NB_CLK100M_PCIE_P

NB_CLK100M_PCIE_N

DMI_S2N_P<0>

DMI_S2N_P<1>

DMI_S2N_P<2>

DMI_N2S_N<0>

DMI_N2S_N<1>

DMI_N2S_N<3>

DMI_N2S_N<2>

DMI_N2S_P<0>

DMI_N2S_P<1>

DMI_N2S_P<2>

DMI_N2S_P<3>

GFX_VID<2>

CLINK_NB_DATA

VR_PWRGOOD_DELAY

CLINK_NB_RESET_L

GND

GND

NB_CLKREQ_L

NB_SB_SYNC_L

TP_MEM_CLKN2

TP_MEM_CLKP5

TP_MEM_CLKN5

PM_BMBUSY_L

CPU_DPRSTP_L

VR_PWRGOOD_DELAY

PM_THRMTRIP_L

MEM_CS_L<2>

MEM_ODT<2>

MEM_ODT<3>

PPVCORE_S0_NB_R

MEM_CS_L<3>

MEM_ODT<0>

MEM_ODT<1>

TP_NB_RSVD<6>

TP_NB_RSVD<12>

TP_NB_NC<4>

GFX_VID<4>

DMI_S2N_P<3>

DMI_S2N_N<2>

PP0V9_S3_MEM_VREF

TP_NB_RSVD<5>

TP_NB_RSVD<24>

TP_MEM_CLKP2

TP_LVDS_A_DATAN3

TP_LVDS_B_DATAP3

MEM_A_A<14>

DMI_S2N_N<0>

TP_NB_RSVD<35>

TP_NB_RSVD<36>

TP_LVDS_B_DATAN3

TP_NB_RSVD<45>

TP_NB_RSVD<42>

DMI_S2N_N<3>

DMI_S2N_N<1>

TP_NB_RSVD<14>

PM_DPRSLPVR

NB_RESET_L

PM_EXTTS_L<1>

NB_CFG<9>

NB_CFG<16>

PP3V3_S0

NB_CFG<19>

NB_CFG<20>

PP3V3_S0

TP_NB_CFG<11>

TP_NB_CFG<13>

GFX_VID<3>

GFX_VR_EN

PP3V3_S0

TP_NB_CFG<17>

GFX_VID<1>

CLINK_NB_CLK

PP1V25_S0M_NB_VCCAXD

GND

NB_CLINK_VREF

NB_BSEL<2>

NB_BSEL<1>

NB_CFG<3>

NB_CFG<6>

NB_CFG<7>

NB_CFG<8>

NB_CFG<9>

NB_CFG<5>

MEM_RCOMP_L

TP_NB_RSVD<43>

TP_NB_RSVD<44>

NB_CFG<4>

MEM_CKE<1>

MEM_CKE<3>

PP0V9_S3_MEM_VREF

MEM_RCOMP_VOL

MEM_RCOMP

PP1V8_S3_ISNS

MEM_RCOMP_VOH

87

87

87

77

77

77

75

75

75

74

74

74

65

65

65

59

59

59

58

58

58

57

57

57

52

52

52

51

51

51

50

50

50

48

48

48

47

47

47

46

46

46

42

42

42

32

32

32

31

31

31

30

30

30

29

29

29

28

28

28

27

27

27

26

26

26

25

25

25

24

24

24

23

23

23

21

21

21

57

19

19

19

50

16

16

16

21

16

13

13

13

21

18

13

7

7

7

7

7

7

7

7

7

7

7

7

7

16

16

16

7

7

7

16

16

8

16

16

8

8

19

83

16

8

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

OUT

OUT

BI

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

OUT

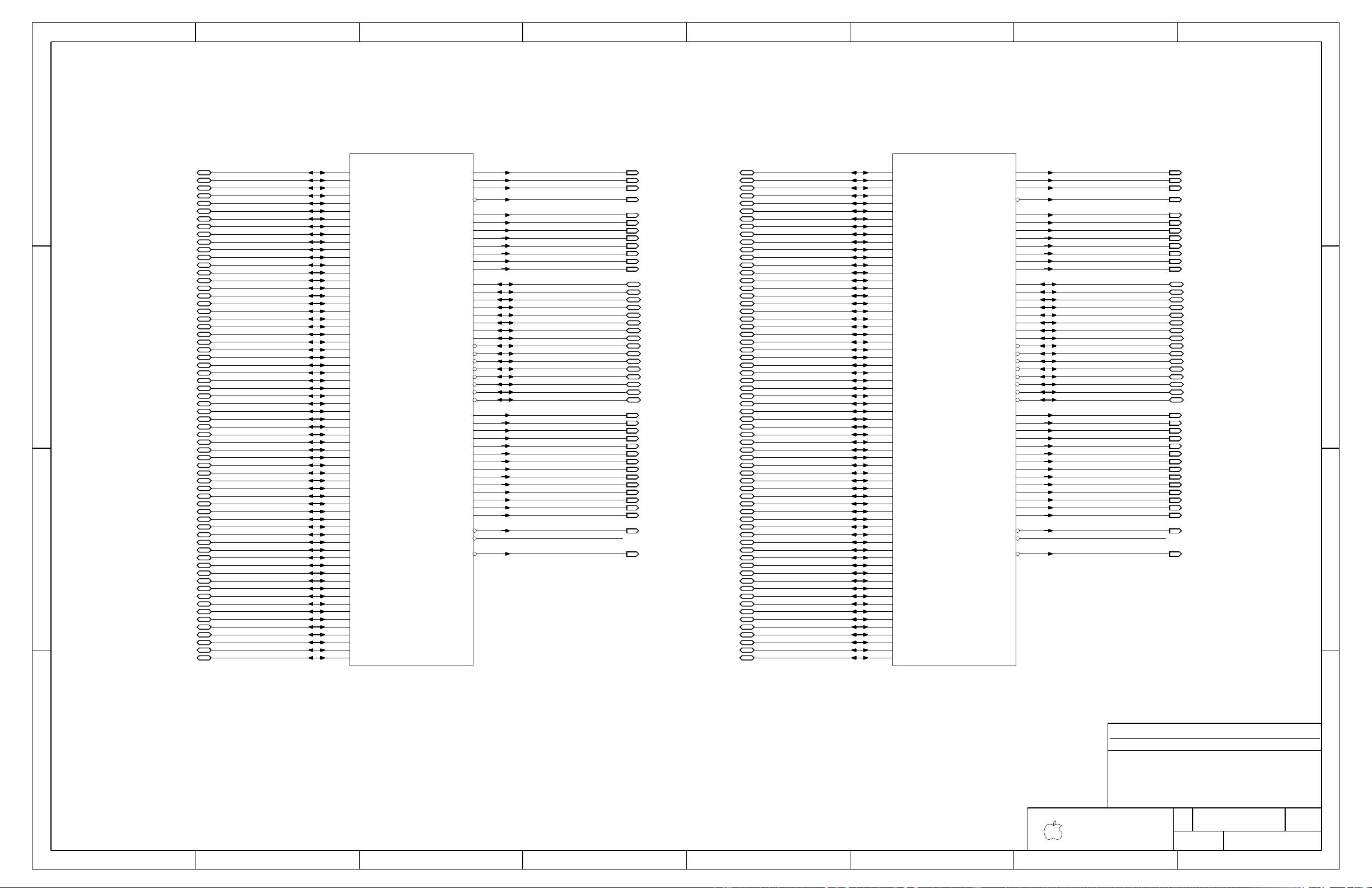

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ4

SA_DQ6

SA_DQ14

SA_CAS*

SA_BS2

SA_DQ63

SA_DQ62

SA_DQ61

SA_DQ60

SA_DQ59

SA_DQ58

SA_DQ57

SA_DQ56

SA_DQ55

SA_DQ54

SA_DQ53

SA_DQ52

SA_DQ51

SA_DQ50

SA_DQ49

SA_DQ48

SA_DQ47

SA_DQ46

SA_DQ44

SA_DQ43

SA_DQ42

SA_DQ41

SA_DQ40

SA_DQ39

SA_DQ38

SA_DQ37

SA_DQ36

SA_DQ34

SA_DQ35

SA_DQ33

SA_DQ32

SA_DQ31

SA_DQ30

SA_DQ28

SA_DQ29

SA_DQ27

SA_DQ26

SA_DQ25

SA_DQ24

SA_DQ23

SA_DQ22

SA_DQ21

SA_DQ20

SA_DQ19

SA_DQ18

SA_DQ17

SA_DQ16

SA_DQ15

SA_DQ13

SA_DQ11

SA_DQ12

SA_DQ10

SA_DQ9

SA_DQ8

SA_DQ7

SA_DQ5

SA_DQ3

SA_BS1

SA_BS0

SA_DQ45

SA_DM0

SA_DM1

SA_DM3

SA_DM2

SA_DM5

SA_DM4

SA_DM7

SA_DM6

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS1*

SA_DQS0*

SA_DQS2*

SA_DQS4*

SA_DQS3*

SA_DQS5*

SA_DQS6*

SA_DQS7*

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA9

SA_MA8

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_RAS*

SA_RCVEN*

SA_WE*

DDR SYSTEM MEMORY A

(4 OF 10)

SB_DQ2

SB_DQ1

SB_DQ5

SB_DM0

SB_DQ0

SB_DQ4

SB_DQ6

SB_DQ7

SB_CAS*

SB_BS2

SB_BS0

SB_BS1

SB_DQ63

SB_DQ62

SB_DQ59

SB_DQ58

SB_DQ56

SB_DQ55

SB_DQ54

SB_DQ53

SB_DQ52

SB_DQ51

SB_DQ50

SB_DQ49

SB_DQ48

SB_DQ47

SB_DQ45

SB_DQ46

SB_DQ44

SB_DQ43

SB_DQ42

SB_DQ41

SB_DQ40

SB_DQ39

SB_DQ38

SB_DQ37

SB_DQ36

SB_DQ34

SB_DQ35

SB_DQ33

SB_DQ32

SB_DQ31

SB_DQ30

SB_DQ28

SB_DQ29

SB_DQ27

SB_DQ26

SB_DQ25

SB_DQ24

SB_DQ23

SB_DQ22

SB_DQ21

SB_DQ20

SB_DQ19

SB_DQ18

SB_DQ17

SB_DQ16

SB_DQ15

SB_DQ14

SB_DQ13

SB_DQ11

SB_DQ12

SB_DQ10

SB_DQ9

SB_DQ8

SB_DQ3

SB_DQ57

SB_DQ61

SB_DQ60

SB_WE*

SB_RCVEN*

SB_RAS*

SB_MA13

SB_MA12

SB_MA11

SB_MA10

SB_MA8

SB_MA9

SB_MA7

SB_MA6

SB_MA5

SB_MA4

SB_MA3

SB_MA2

SB_MA1

SB_MA0

SB_DQS7*

SB_DQS6*

SB_DQS5*

SB_DQS3*

SB_DQS4*

SB_DQS2*

SB_DQS0*

SB_DQS1*

SB_DQS7

SB_DQS6

SB_DQS5

SB_DQS4

SB_DQS3

SB_DQS2

SB_DQS1

SB_DQS0

SB_DM6

SB_DM7

SB_DM4

SB_DM5

SB_DM2

SB_DM3

SB_DM1

(5 OF 10)

DDR SYSTEM MEMORY B

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

31 81 32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

31 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

31 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

31 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

31 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

31 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 33 81

32 33 81

32 33 81

31 81

32 33 81

32 33 81

32 33 81

32 33 81

32 33 81

32 33 81

32 33 81

32 33 81

32 33 81

32 33 81

31 81

32 33 81

32 33 81

32 33 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

31 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

31 81

32 81

32 81

32 81

32 81

32 81

32 81

32 81

32 33 81

32 33 81

32 33 81

31 81

32 33 81

U1400

BB19

BK19

BF29

BL17

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AR43

AW44

BG47

BJ45

BB47

BG50

BH49

BE45

AW43

BE44

BG42

BE40

BA45

BF44

BH45

BG40

BF40

AR40

AW40

AT39

AW36

AW41

AY41

AY46

AV38

AT38

AV13

AT13

AW11

AV11

AU15

AT11

BA13

BA11

AR41

BE10

BD10

BD8

AY9

BG10

AW9

BD7

BB9

BB5

AY7

AR45

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AM8

AN10

AT42

AT9

AN9

AM9

AN11

AW47

BB45

BF48

AT46

AT47

BE48

BD47

BB43

BC41

BC37

BA37

BB16

BA16

BH6

BH7

BB2

BC1

AP3

AP2

BJ19

BD20

BC19

BE28

BG30

BJ16

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BE18

AY20

BA19

OMIT

CRESTLINE

FCBGA

U1400

AY17

BG18

BG36

BE17

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AP49

AR51

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

AW50

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

AW51

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

AN51

BJ10

BL9

BK5

BL5

BK9

BK10

BJ8

BJ6

BF4

BH5

AN50

BG1

BC2

BK3

BE4

BD3

BJ2

BA3

BB3

AR1

AT3

AV50

AY2

AY3

AU2

AT2

AV49

BA50

BB50

AT50

AU50

BD50

BC50

BK46

BL45

BK39

BK38

BJ12

BK12

BL7

BK7

BE2

BF2

AV2

AV3

BC18

BG28

BG17

BE37

BA39

BG13

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

AV16

AY18

BC17

OMIT

CRESTLINE

FCBGA

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 33 81

31 33 81

31 33 81

31 81

31 33 81

31 81

31 33 81

31 33 81

31 33 81

31 33 81

31 33 81

31 33 81

31 33 81

31 81

31 33 81

31 33 81

31 33 81

31 33 81

31 33 81

31 33 81

31 33 81

31 33 81

31 33 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

31 81

17 88

14.0.0

051-7225

NB DDR2 Interfaces

SYNC_MASTER=T9_NOME

SYNC_DATE=03/16/2007

MEM_A_DQ<35>

TP_MEM_A_RCVEN_L TP_MEM_B_RCVEN_L

MEM_B_DQ<39>

MEM_B_BS<0>

MEM_B_BS<1>

MEM_B_BS<2>

MEM_B_DM<0>

MEM_B_CAS_L

MEM_B_DM<1>

MEM_B_DM<2>

MEM_B_DQ<0>

MEM_B_DQ<1>

MEM_B_DQ<2>

MEM_B_DQ<3>

MEM_B_DQ<4>

MEM_B_DQ<5>

MEM_B_DQ<6>

MEM_B_DQ<7>

MEM_B_DQ<8>

MEM_B_DM<3>

MEM_B_DM<4>

MEM_B_DM<5>

MEM_B_DM<6>

MEM_B_DM<7>

MEM_B_DQS_P<1>

MEM_B_DQS_P<0>

MEM_B_DQS_P<4>

MEM_B_DQS_P<3>

MEM_B_DQS_P<2>

MEM_B_DQS_P<6>

MEM_B_DQS_P<5>

MEM_B_DQS_N<1>

MEM_B_DQS_P<7>

MEM_B_DQS_N<0>

MEM_B_DQS_N<3>

MEM_B_DQS_N<2>

MEM_B_DQS_N<4>

MEM_B_DQS_N<6>

MEM_B_DQS_N<5>

MEM_B_DQS_N<7>

MEM_B_A<0>

MEM_B_A<1>

MEM_B_A<2>

MEM_B_A<3>

MEM_B_A<4>

MEM_B_A<5>

MEM_B_A<6>

MEM_B_A<7>

MEM_B_A<8>

MEM_B_A<9>

MEM_B_A<10>

MEM_B_A<11>

MEM_B_A<12>

MEM_B_RAS_L

MEM_B_A<13>

MEM_B_WE_L

MEM_B_DQ<9>

MEM_B_DQ<10>

MEM_B_DQ<11>

MEM_B_DQ<12>

MEM_B_DQ<13>

MEM_B_DQ<14>

MEM_B_DQ<15>

MEM_B_DQ<16>

MEM_B_DQ<17>

MEM_B_DQ<18>

MEM_B_DQ<19>

MEM_B_DQ<20>

MEM_B_DQ<21>

MEM_B_DQ<22>

MEM_B_DQ<23>

MEM_B_DQ<24>

MEM_B_DQ<25>

MEM_B_DQ<26>

MEM_B_DQ<27>

MEM_B_DQ<28>

MEM_B_DQ<29>

MEM_B_DQ<30>

MEM_B_DQ<31>

MEM_B_DQ<32>

MEM_B_DQ<33>

MEM_B_DQ<34>

MEM_B_DQ<35>

MEM_B_DQ<36>

MEM_B_DQ<37>

MEM_B_DQ<38>

MEM_B_DQ<40>

MEM_B_DQ<41>

MEM_B_DQ<42>

MEM_B_DQ<43>

MEM_B_DQ<44>

MEM_B_DQ<45>

MEM_B_DQ<46>

MEM_B_DQ<47>

MEM_B_DQ<48>

MEM_B_DQ<49>

MEM_B_DQ<50>

MEM_B_DQ<51>

MEM_B_DQ<52>

MEM_B_DQ<53>

MEM_B_DQ<54>

MEM_B_DQ<55>

MEM_B_DQ<56>

MEM_B_DQ<57>

MEM_B_DQ<58>

MEM_B_DQ<59>

MEM_B_DQ<60>

MEM_B_DQ<61>

MEM_B_DQ<62>

MEM_B_DQ<63>

MEM_A_DQ<0>

MEM_A_DQ<1>

MEM_A_DQ<2>

MEM_A_DQ<4>

MEM_A_DQ<6>

MEM_A_CAS_L

MEM_A_BS<2>

MEM_A_DQ<8>

MEM_A_DQ<7>

MEM_A_DQ<5>

MEM_A_DQ<3>

MEM_A_BS<1>

MEM_A_BS<0>

MEM_A_DM<0>

MEM_A_DM<1>

MEM_A_DM<3>

MEM_A_DM<2>

MEM_A_DM<5>

MEM_A_DM<4>

MEM_A_DM<7>

MEM_A_DM<6>

MEM_A_DQS_P<0>

MEM_A_DQS_P<1>

MEM_A_DQS_P<2>

MEM_A_DQS_P<3>

MEM_A_DQS_P<4>

MEM_A_DQS_P<5>

MEM_A_DQS_P<6>

MEM_A_DQS_P<7>

MEM_A_DQS_N<1>

MEM_A_DQS_N<0>

MEM_A_DQS_N<2>

MEM_A_DQS_N<4>

MEM_A_DQS_N<3>

MEM_A_DQS_N<5>

MEM_A_DQS_N<6>

MEM_A_DQS_N<7>

MEM_A_A<0>

MEM_A_A<1>

MEM_A_A<2>

MEM_A_A<3>

MEM_A_A<4>

MEM_A_A<5>

MEM_A_A<6>

MEM_A_A<7>

MEM_A_A<9>

MEM_A_A<8>

MEM_A_A<10>

MEM_A_A<11>

MEM_A_A<12>

MEM_A_A<13>

MEM_A_RAS_L

MEM_A_WE_L

MEM_A_DQ<9>

MEM_A_DQ<10>

MEM_A_DQ<11>

MEM_A_DQ<12>

MEM_A_DQ<13>

MEM_A_DQ<14>

MEM_A_DQ<15>

MEM_A_DQ<16>

MEM_A_DQ<17>

MEM_A_DQ<18>

MEM_A_DQ<19>

MEM_A_DQ<20>

MEM_A_DQ<21>

MEM_A_DQ<22>

MEM_A_DQ<23>

MEM_A_DQ<24>

MEM_A_DQ<25>

MEM_A_DQ<26>

MEM_A_DQ<27>

MEM_A_DQ<28>

MEM_A_DQ<29>

MEM_A_DQ<30>

MEM_A_DQ<31>

MEM_A_DQ<32>

MEM_A_DQ<33>

MEM_A_DQ<34>

MEM_A_DQ<36>

MEM_A_DQ<37>

MEM_A_DQ<38>

MEM_A_DQ<39>

MEM_A_DQ<40>

MEM_A_DQ<41>

MEM_A_DQ<42>

MEM_A_DQ<43>

MEM_A_DQ<44>

MEM_A_DQ<45>

MEM_A_DQ<46>

MEM_A_DQ<47>

MEM_A_DQ<48>

MEM_A_DQ<49>

MEM_A_DQ<50>

MEM_A_DQ<51>

MEM_A_DQ<52>

MEM_A_DQ<53>

MEM_A_DQ<54>

MEM_A_DQ<55>

MEM_A_DQ<56>

MEM_A_DQ<57>

MEM_A_DQ<58>

MEM_A_DQ<59>

MEM_A_DQ<60>

MEM_A_DQ<61>

MEM_A_DQ<62>

MEM_A_DQ<63>

VCC_SM20

VCC_AXG_NCTF42

VCC_SM9

VCC_SM10

VCC_SM17

VCC_SM16

VCC3

VCC_SM5

VCC_SM8

VCC_AXG_NCTF1

VCC_AXG_NCTF2

VCC_AXG_NCTF3

VCC_AXG_NCTF4

VCC_AXG_NCTF5

VCC_AXG_NCTF6

VCC_AXG_NCTF8

VCC_AXG_NCTF7

VCC_AXG_NCTF10

VCC_AXG_NCTF9

VCC_AXG_NCTF11

VCC_AXG_NCTF12

VCC_AXG_NCTF13

VCC_AXG_NCTF14

VCC_AXG_NCTF15

VCC_AXG_NCTF16

VCC_AXG_NCTF18

VCC_AXG_NCTF17

VCC_AXG_NCTF20

VCC_AXG_NCTF19

VCC_AXG_NCTF21

VCC_AXG_NCTF22

VCC_AXG_NCTF25

VCC_AXG_NCTF26

VCC_AXG_NCTF28

VCC_AXG_NCTF27

VCC_AXG_NCTF29

VCC_AXG_NCTF20

VCC_AXG_NCTF31

VCC_AXG_NCTF32

VCC_AXG_NCTF33

VCC_AXG_NCTF34

VCC_AXG_NCTF35

VCC_AXG_NCTF36

VCC_AXG_NCTF38

VCC_AXG_NCTF37

VCC_AXG_NCTF40

VCC_AXG_NCTF39

VCC_AXG_NCTF41

VCC_AXG_NCTF43

VCC_AXG_NCTF44

VCC_AXG_NCTF45

VCC_AXG_NCTF46

VCC_AXG_NCTF48

VCC_AXG_NCTF47

VCC_AXG_NCTF49

VCC_AXG_NCTF50

VCC_AXG_NCTF51

VCC_AXG_NCTF55

VCC_AXG_NCTF58

VCC_AXG_NCTF57

VCC_AXG_NCTF59

VCC_AXG_NCTF61

VCC_AXG_NCTF60

VCC_AXG_NCTF62

VCC_AXG_NCTF63

VCC_AXG_NCTF64

VCC_AXG_NCTF66

VCC_AXG_NCTF65

VCC_AXG_NCTF67

VCC_AXG_NCTF68

VCC_AXG_NCTF69

VCC_AXG_NCTF71

VCC_AXG_NCTF70

VCC_AXG_NCTF72

VCC_AXG_NCTF73

VCC_AXG_NCTF74

VCC_AXG_NCTF76

VCC_AXG_NCTF75

VCC_AXG_NCTF77

VCC_AXG_NCTF78

VCC_AXG_NCTF79

VCC_AXG_NCTF81

VCC_AXG_NCTF80

VCC_AXG_NCTF82

VCC_AXG_NCTF83

VCC_SM_LF1

VCC_SM_LF2

VCC_SM_LF3

VCC_SM_LF4

VCC_SM_LF5

VCC_SM_LF6

VCC_SM_LF7

VCC_AXG_NCTF56

VCC_AXG_NCTF54

VCC_AXG_NCTF53

VCC_AXG_NCTF52

VCC_AXG1

VCC_AXG2

VCC_AXG3

VCC_AXG4

VCC_AXG5

VCC_AXG6

VCC_AXG7

VCC_AXG8

VCC_AXG9

VCC_AXG10

VCC_AXG11

VCC_AXG12

VCC_AXG13

VCC_AXG14

VCC_AXG15

VCC_AXG16

VCC_AXG17

VCC_AXG18

VCC_AXG19

VCC_AXG20

VCC_AXG21

VCC_AXG22

VCC_AXG23

VCC_AXG24

VCC_AXG25

VCC_AXG26

VCC_AXG27

VCC_AXG28

VCC_AXG29

VCC_AXG30

VCC_AXG31

VCC_AXG32

VCC_AXG33

VCC_AXG34

VCC_SM1

VCC_SM2

VCC_SM3

VCC_SM4

VCC_SM6

VCC_SM7

VCC_SM11

VCC_SM12

VCC_SM13

VCC_SM14

VCC_SM15

VCC_SM18

VCC_SM19

VCC_SM21

VCC_SM22

VCC_SM23

VCC_SM26

VCC_SM27

VCC_SM28

VCC_SM29

VCC_SM30

VCC_SM31

VCC_SM32

VCC_SM33

VCC_SM34

VCC_SM35

VCC_SM36

VCC_SM25

VCC_SM24

VCC1

VCC2

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC_AXG_NCTF24

VCC_AXG_NCTF23

VCC6

VCC5

VCC4

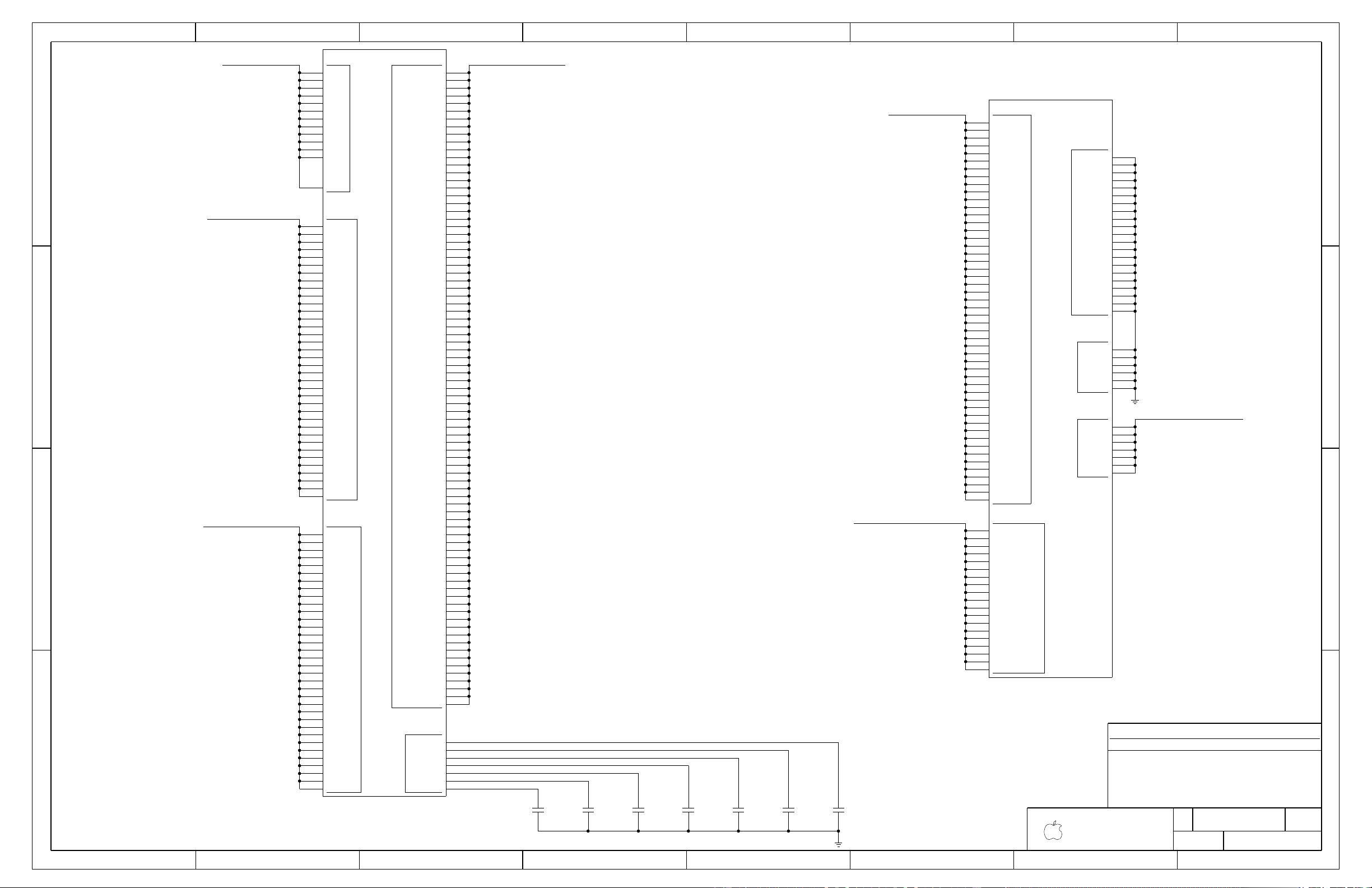

VCC GFX

VCC SM

VCC SM LF

(6 OF 10)

VCC CORE

POWER

VCC GFX NCTF

VCC_NCTF49

VCC_NCTF15

VCC_NCTF2

VCC_NCTF10

VCC_AXM7

VCC_AXM5

VCC_AXM4

VCC_AXM3

VCC_AXM2

VCC_AXM1

VSS_SCB6

VSS_SCB5

VSS_SCB4

VSS_SCB3

VSS_SCB2

VSS_SCB1

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VSS_NCTF21

VSS_NCTF20

VSS_NCTF19

VSS_NCTF18

VSS_NCTF17

VSS_NCTF16

VSS_NCTF15

VSS_NCTF14

VSS_NCTF12

VSS_NCTF11

VSS_NCTF13

VSS_NCTF10

VSS_NCTF9

VSS_NCTF8

VSS_NCTF7

VSS_NCTF6

VSS_NCTF5

VSS_NCTF4

VSS_NCTF3

VSS_NCTF2

VSS_NCTF1

VCC_NCTF22

VCC_NCTF27

VCC_NCTF50

VCC_NCTF47

VCC_NCTF48

VCC_NCTF44

VCC_NCTF43

VCC_NCTF39

VCC_NCTF40

VCC_NCTF38

VCC_NCTF37

VCC_NCTF34

VCC_NCTF35

VCC_NCTF33

VCC_NCTF32

VCC_NCTF31

VCC_NCTF29

VCC_NCTF28

VCC_NCTF26

VCC_NCTF24

VCC_NCTF25

VCC_NCTF23

VCC_NCTF21

VCC_NCTF18

VCC_NCTF19

VCC_NCTF16

VCC_NCTF17

VCC_NCTF3

VCC_NCTF4

VCC_NCTF41

VCC_NCTF42

VCC_NCTF45

VCC_NCTF46

VCC_AXM6

VCC_AXM_NCTF1

VCC_AXM_NCTF2

VCC_AXM_NCTF3

VCC_AXM_NCTF4

VCC_AXM_NCTF5

VCC_AXM_NCTF6

VCC_AXM_NCTF7

VCC_AXM_NCTF8

VCC_AXM_NCTF9

VCC_AXM_NCTF10

VCC_AXM_NCTF11

VCC_AXM_NCTF12

VCC_AXM_NCTF13

VCC_AXM_NCTF14

VCC_AXM_NCTF15

VCC_AXM_NCTF16

VCC_AXM_NCTF17

VCC_AXM_NCTF18

VCC_AXM_NCTF19

VCC_NCTF8

VCC_NCTF20

VCC_NCTF1

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF36

VCC_NCTF30

VCC_NCTF9

VCC AXM NCTF

VCC NCTF

VSS SCBVCC AXM

VSS NCTF

(7 OF 10)

POWER

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

1395 mA (1 ch, 533MHz)

1700 mA (1 ch, 667MHz)

2700 mA (2 ch, 533MHz)

3300 mA (2 ch, 667MHz)

540 mA

1573 mA (Int Graphics)

1310 mA (Ext Graphics)

7700 mA (Int Graphics)

5 mA (standby)

impacting part performance.

These connections can break without

NCTF balls are Not Critical To Function

Current numbers from Crestline EDS, doc #21749.

U1400

AT35

AH31

AH29

AF32

R30

AT34

AH28

AC31

AC32

AK32

AJ31

AJ28

AH32

R20

AB21

AB24

AB29

AC20

AC21

AC23

AC24

AC26

AC28

AC29

T14

AD20

AD23

AD24

AD28

AF21

AF26

AA31

AH20

AH21

AH23

W13

AH24

AH26

AD31

AJ20

AN14

W14

Y12

AA20

AA23

AA26

AA28

T17

U17

U19

U20

U21

U23

U26

V16

V17

V19

V20

T18

V21

V23

V24

Y15

Y16

Y17

Y19

Y20

Y21

Y23

T19

Y24

Y26

Y28

Y29

AA16

AA17

AB16

AB19

AC16

AC17

T21

AC19

AD15

AD16

AD17

AF16

AF19

AH15

AH16

AH17

AH19

T22

AJ16

AJ17

AJ19

AK16

AK19

AL16

AL17

AL19

AL20

AL21

T23

AL23

AM15

AM16

AM19

AM20

AM21

AM23

AP15

AP16

AP17

T25

AP19

AP20

AP21

AP23

AP24

AR20

AR21

AR23

AR24

AR26

U15

V26

V28

V29

Y31

U16

AU32

BA35

BB33

BC32

BC33

BC35

BD32

BD35

BE32

BE33

BE35

AU33

BF33

BF34

BG32

BG33

BG35

BH32

BH34

BH35

BJ32

BJ33

AU35

BJ34

BK32

BK33

BK34

BK35

BL33

AU30

AV33

AW33

AW35

AY35

BA32

BA33

AW45

BC39

BE39

BD17

BD4

AW8

AT6

OMIT

CRESTLINE

FCBGA

U1400

AT33

AT31

AK29

AK24

AK23

AJ26

AJ23

AL24

AP29

AP31

AP32

AP33

AL29

AL31

AL32

AR31

AR32

AR33

AL26

AL28

AM26

AM28

AM29

AM31

AM32

AM33

AB33

AF36

AH33

AH35

AH36

AH37

AJ33

AJ35

AK33

AK35

AK36

AB36

AK37

AD33

AJ36

AM35

AL33

AL35

AA33

AA35

AA36

AP35

AB37

AP36

AR35

AR36

Y32

Y33

Y35

Y36

Y37

T30

T34

AC33

T35

U29

U31

U32

U33

U35

U36

V32

V33

V36

AC35

V37

AC36

AD35

AD36

AF33

T27

AD19

AD37

AF17

AF35

AK17

AM17

AM24

AP26

AP28

AR15

T37

AR19

AR28

U24

U28

V31

V35

AA19

AB17

AB35

A3

B2

C1

BL1

BL51

A51

OMIT

CRESTLINE

FCBGA

C1806

1

2

402

0.1uF

10V

CERM

20%

C1807

1

2

402

0.1uF

10V

CERM

20%

C1804

1

2

402

X5R

0.22UF

6.3V

20%

C1805

1

2

402

X5R

0.22UF

6.3V

20%

C1802

1

2

402

10%

CERM

1uF

6.3V

C1803

1

2

402

10%

0.47UF

6.3V

CERM-X5R

C1801

1

2

402

10%

CERM

1uF

6.3V

18 88

14.0.0

051-7225

NB Power 1

SYNC_DATE=03/16/2007

SYNC_MASTER=T9_NOME

PP1V05_S0

NB_VCCSM_LF5

NB_VCCSM_LF7

PPVCORE_S0_NB_R

PP1V05_S0

NB_VCCSM_LF1

NB_VCCSM_LF2

NB_VCCSM_LF3

NB_VCCSM_LF4

NB_VCCSM_LF6

PPVCORE_S0_NB_GFX

PPVCORE_S0_NB_R

PPVCORE_S0_NB_GFX

PP1V8_S3_ISNS

61

61

50

50

46

46

30

30

27

27

26

26

23

23

21

21

19

19

18

18

14

50

14

50

13

22

13

59

22 59

57

12

21

12

22

21 22

50

11

18

11

18

18 18

21

10

16

10

8

16

8

16

8

8

8

7

8 7

8

剩余87页未读,继续阅读

点击了解资源详情

2024-10-27 上传

2024-10-27 上传

2024-10-27 上传

JOZECN

- 粉丝: 757

- 资源: 3144

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C++ Qt影院票务系统源码发布,代码稳定,高分毕业设计首选

- 纯CSS3实现逼真火焰手提灯动画效果

- Java编程基础课后练习答案解析

- typescript-atomizer: Atom 插件实现 TypeScript 语言与工具支持

- 51单片机项目源码分享:课程设计与毕设实践

- Qt画图程序实战:多文档与单文档示例解析

- 全屏H5圆圈缩放矩阵动画背景特效实现

- C#实现的手机触摸板服务端应用

- 数据结构与算法学习资源压缩包介绍

- stream-notifier: 简化Node.js流错误与成功通知方案

- 网页表格选择导出Excel的jQuery实例教程

- Prj19购物车系统项目压缩包解析

- 数据结构与算法学习实践指南

- Qt5实现A*寻路算法:结合C++和GUI

- terser-brunch:现代JavaScript文件压缩工具

- 掌握Power BI导出明细数据的操作指南

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功