0.18微米浮栅EEPROM工艺流程详解:SMIC嵌入式逻辑与高耐久存储技术

需积分: 31 36 浏览量

更新于2024-07-17

3

收藏 962KB PPT 举报

0.18微米浮栅EEPROM工艺流程介绍

本PPT详细阐述了0.18微米(0.18um)浮栅EEPROM(Electrically Erasable Programmable Read-Only Memory)的简单工艺流程,该流程由SMIC(Semiconductor Manufacturing International Corporation)的0.18微米逻辑工艺完全集成。这种EEPROM技术支持多种电压选项,包括1.8伏逻辑核心、3.3伏或5伏的主电源(MV)以及16伏的高压(HV)工作环境,旨在实现高度兼容性和灵活性。

设计上,这款EEPROM芯片集成了ROM(Read-Only Memory)、OTP(One-Time Programmable)和EEPROM功能于一身,采用复古双阱(Retrograde Twin Well)、高压窄沟道(HVNW)和P型衬底等多种结构,以实现高密度的2P3M至5M存储单元。整个工艺流程涉及31个掩模步骤,其中额外的10次光刻是为了优化EEPROM部分的设计。

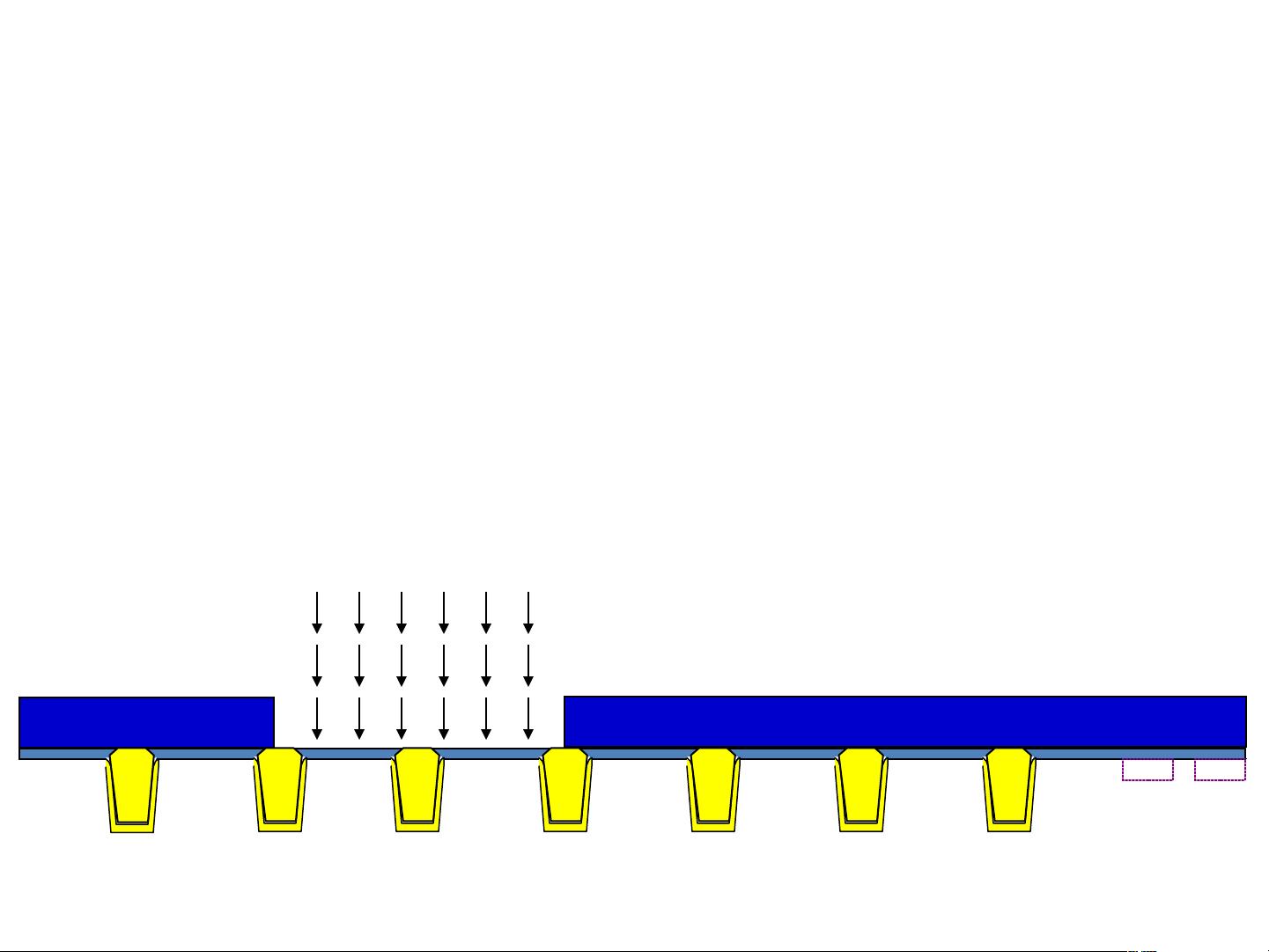

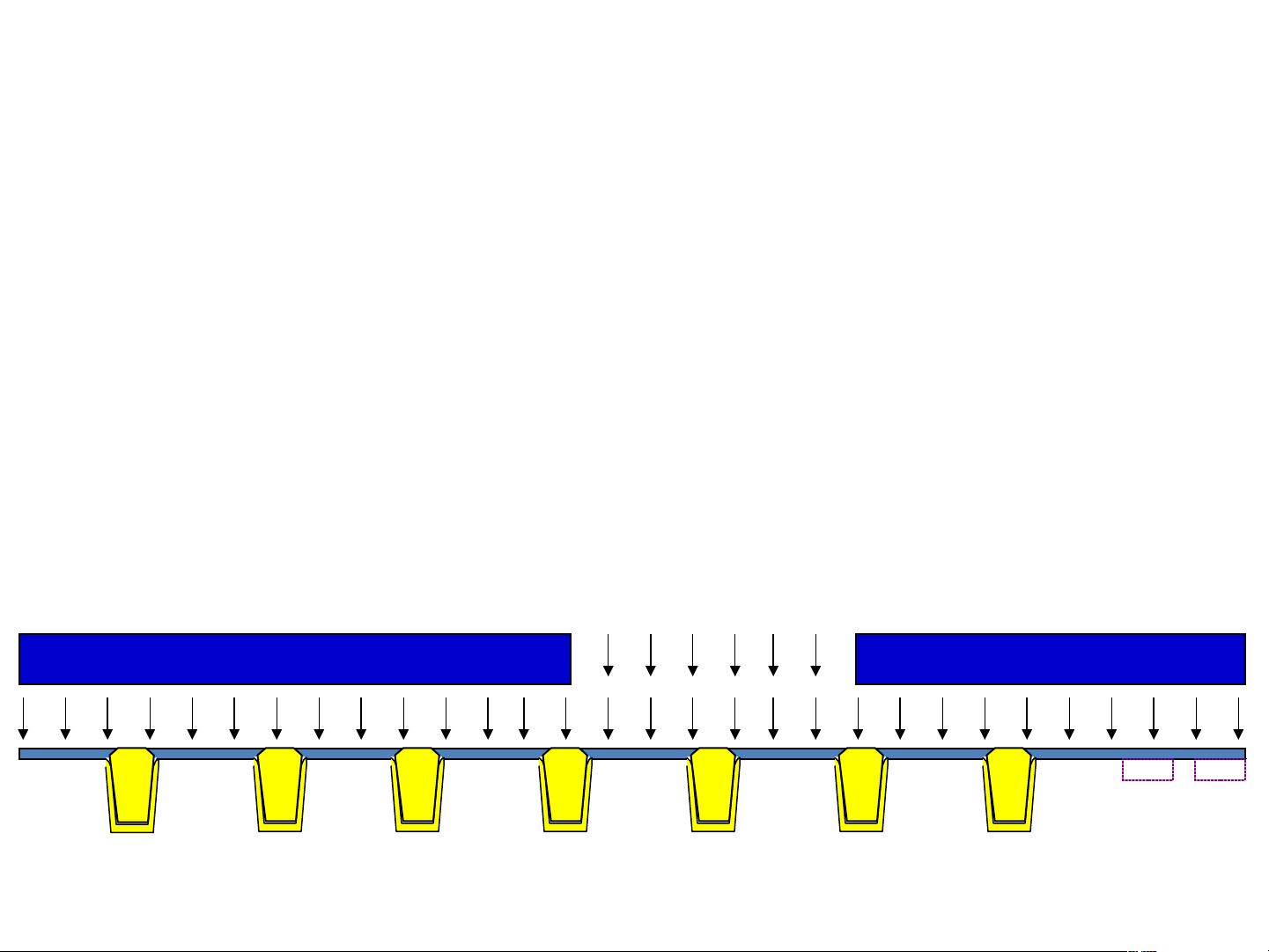

在制造过程中,从wafer开始,通过一系列关键步骤进行操作,如P型衬底的预处理(8-12欧姆每厘米的电阻率)、氧化物生长、离子注入、光刻和蚀刻等,然后是P-Well、P型和N型子层的堆叠,包括LVN(Lightly Doped N-type)、HVN(High Voltage N-type)、MVN(Medium Voltage N-type)、HVZ(High Voltage Zero Bias)等不同类型的衬底。此外,还采用了浅沟槽隔离(STI)技术,包括STI高介电氧化物沉积、光刻和CMP(Chemical Mechanical Polishing)等步骤,以提供良好的隔离性能。

工艺流程中的关键阶段还包括TIM(Tunneling Induced Metalization)的光刻和植入技术,用于制造隧道接触,确保高性能的读写功能。这些步骤确保了EEPROM具有超过10万次的写入/擦除周期,以及长达40年的数据保留能力,表现出与晶圆厂竞争的位细胞尺寸优势。

总结来说,这份PPT深入讲解了0.18微米浮栅EEPROM的工艺流程,涵盖了从材料准备到封装的各种复杂步骤,强调了其在非易失性内存(NVM)领域的技术特性,为芯片设计者提供了对这种高级存储解决方案的全面理解。

qq_20491393

- 粉丝: 4

- 资源: 5

最新资源

- Elasticsearch核心改进:实现Translog与索引线程分离

- 分享个人Vim与Git配置文件管理经验

- 文本动画新体验:textillate插件功能介绍

- Python图像处理库Pillow 2.5.2版本发布

- DeepClassifier:简化文本分类任务的深度学习库

- Java领域恩舒技术深度解析

- 渲染jquery-mentions的markdown-it-jquery-mention插件

- CompbuildREDUX:探索Minecraft的现实主义纹理包

- Nest框架的入门教程与部署指南

- Slack黑暗主题脚本教程:简易安装指南

- JavaScript开发进阶:探索develop-it-master项目

- SafeStbImageSharp:提升安全性与代码重构的图像处理库

- Python图像处理库Pillow 2.5.0版本发布

- mytest仓库功能测试与HTML实践

- MATLAB与Python对比分析——cw-09-jareod源代码探究

- KeyGenerator工具:自动化部署节点密钥生成