SM2C256VQ100开发板电路原理与解析

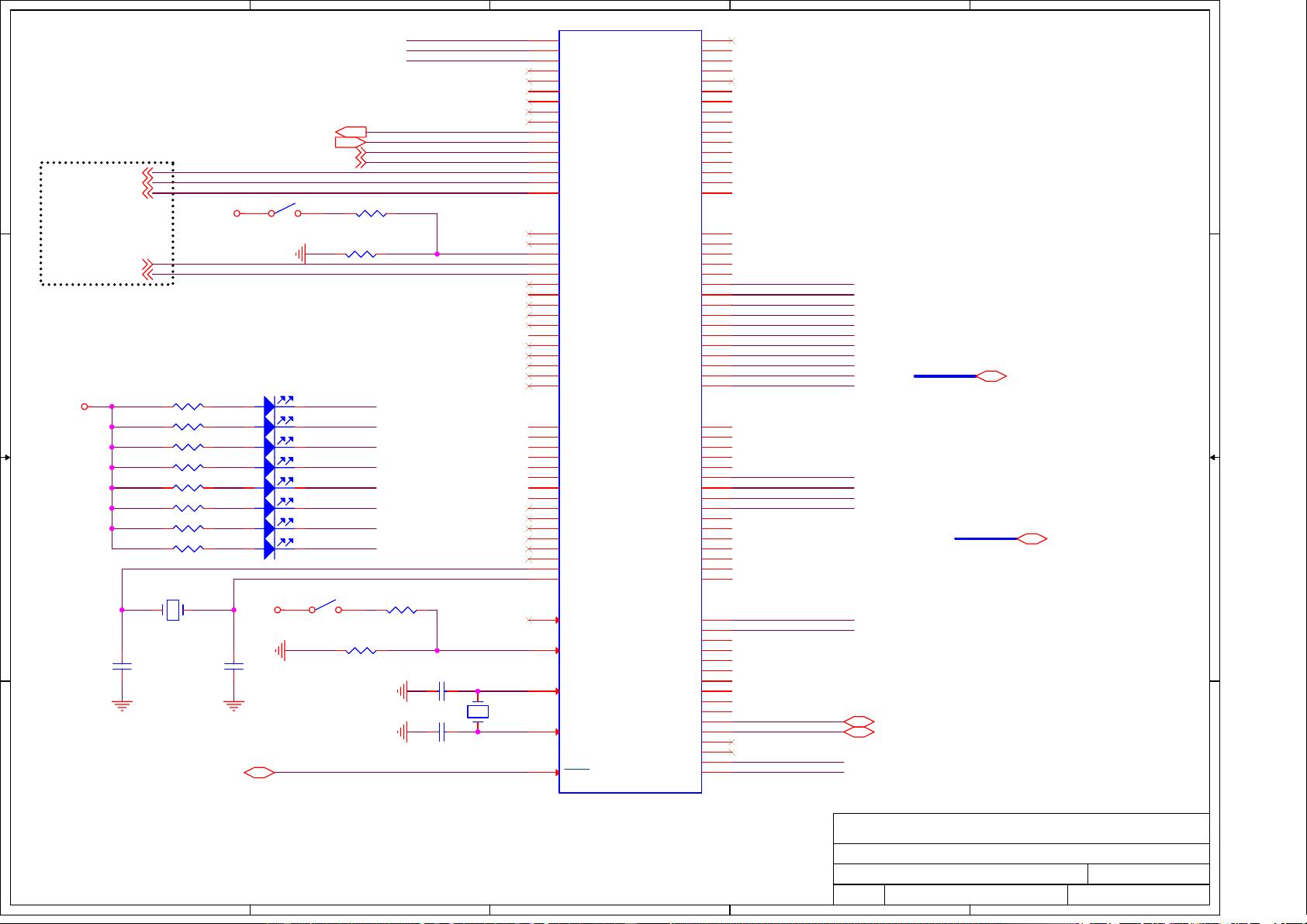

"SM2C256VQ100开发板原理图" 这份资源是关于SM2C256VQ100开发板的原理图,它主要用于硬件设计和综合资源的理解与开发。SM2C256VQ100可能是一款基于SRAM或者DRAM的内存芯片,用于存储数据。开发板是工程师进行产品原型设计、测试和验证的平台,通常包含了核心处理器、内存、电源管理、输入输出接口等多种组件。 在提供的原理图中,我们可以看到以下几个关键部分: 1. **电源管理**:开发板上有电源关闭(PowerOff)的阈值设定,当电压降至3.09V时,系统可能会自动关闭。这确保了在低电压情况下保护电路不受到损害。 2. **复位电路**:系统复位(SYS_/RESET)和系统复位输出(SYS_/PFO)被用于初始化系统。它们通常由一个上拉电阻(如R83, R81, R82, R80)和电容(C400)组成,形成一个简单的RC网络,提供复位信号的延时。 3. **监控复位器(MAX708SESA)**:U7器件是Maxim的MAX708SESA,这是一种低电压复位IC,可以监测电源电压并在电压低于预设阈值时触发复位,确保系统在稳定电压下运行。 4. **多路复用器/解复用器(CPLD)**:CPLD(复杂可编程逻辑器件)在原理图中占据了重要位置,用于灵活地管理和分配各种输入输出信号。例如,CPLD_IO[1..42]、CPLD_IO[60..77]等,这些引脚可以配置为不同的功能,如GPIO、时钟、串行通信等。 5. **时钟信号**:GCLK1和GCLK2代表全局时钟输入,这些是系统中的主要时钟源,可能连接到外部晶振或系统主时钟。 6. **通信接口**:开发板上可能包含串行通信接口,如TXD2和RXD2,这些通常是UART接口的一部分,用于设备间的异步数据传输。 7. **其他I/O**:CPLD_IO[1..77]涵盖了广泛的数字输入输出,可以连接到各种外围设备,如传感器、显示屏、按键等。 8. **版本和日期信息**:在原理图的顶部,我们看到Rev1.0表示这是设计的第一个版本,日期为2015年1月26日,表明这是设计完成的日期。 这个原理图提供了理解开发板硬件结构的基础,包括电源管理、复位机制、CPLD的配置以及通信接口。开发者可以根据这个原理图进行硬件调试、功能扩展和软件驱动的编写。同时,为了更深入地理解和操作开发板,还需要参考相关的数据手册和用户指南。

剩余12页未读,继续阅读

- 粉丝: 2

- 资源: 6

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 最优条件下三次B样条小波边缘检测算子研究

- 深入解析:wav文件格式结构

- JIRA系统配置指南:代理与SSL设置

- 入门必备:电阻电容识别全解析

- U盘制作启动盘:详细教程解决无光驱装系统难题

- Eclipse快捷键大全:提升开发效率的必备秘籍

- C++ Primer Plus中文版:深入学习C++编程必备

- Eclipse常用快捷键汇总与操作指南

- JavaScript作用域解析与面向对象基础

- 软通动力Java笔试题解析

- 自定义标签配置与使用指南

- Android Intent深度解析:组件通信与广播机制

- 增强MyEclipse代码提示功能设置教程

- x86下VMware环境中Openwrt编译与LuCI集成指南

- S3C2440A嵌入式终端电源管理系统设计探讨

- Intel DTCP-IP技术在数字家庭中的内容保护

信息提交成功

信息提交成功