Quartus II入门教程:创建与实现三人表决器逻辑

需积分: 10 48 浏览量

更新于2024-07-31

收藏 634KB DOC 举报

Quartus II 是一款由 Altera 公司开发的高级逻辑综合器,用于FPGA 和 CPLD 设备的设计与实现。本文详细介绍了如何使用 Quartus II 7.0 进行PLD(可编程逻辑器件)上的逻辑设计,以一个三人表决器为例进行教学。以下是整个使用入门过程的详细步骤:

1. **项目启动**:

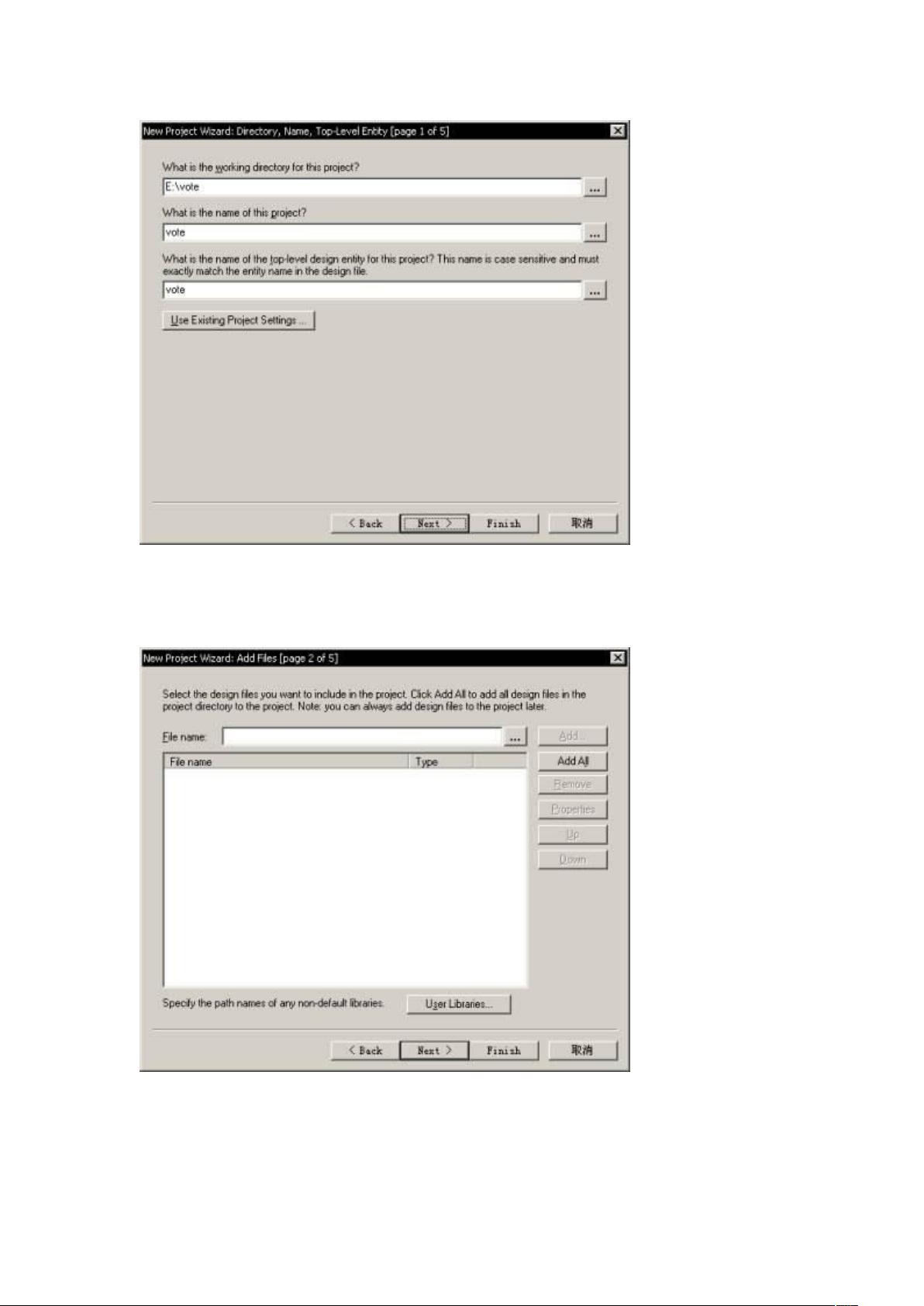

- 通过 "File" 菜单的 "New Project Wizard…" 命令开始一个新的设计项目,按照向导逐步创建。

2. **项目设置**:

- 在项目向导中,选择项目的工作目录和名称(如 "vote"),然后跳过加入现有设计文件的步骤,因为当前没有设计文件。

3. **器件选择**:

- 在器件选择阶段,确定为 Cyclone 系列,比如 EP1C6Q240C8,这是具体型号的选择。

4. **工具配置**:

- 接下来,可以选择综合工具、仿真工具和时间分析工具。本例中,使用 Quartus II 6.0 的默认设置。

5. **项目创建**:

- 完成所有设置后,点击 "Finish" 创建项目。

6. **原理图设计**:

- 在 "File" 菜单中新建一个原理图文件(BlockDiagram/Schematic File),这是硬件设计的第一步,用于绘制电路图。

7. **元件添加**:

- 在原理图中,会用到如按键(代表参与者)、指示灯(显示表决结果)等基本逻辑元素,根据设计需求将其添加到图纸上。

8. **电路连接**:

- 连接各个元件,实现表决器的逻辑功能。例如,将按键信号与表决逻辑门(如与非门、或非门)相连,以模拟三人表决的条件。

9. **真值表编写**:

- 提供的真值表展示了不同输入组合对应的输出状态,用于指导设计过程中逻辑函数的定义。

10. **逻辑编译**:

- 完成设计后,使用 Quartus II 的综合工具将原理图转化为硬件描述语言 (HDL),如 VHDL 或 Verilog,进行逻辑优化和错误检查。

11. **逻辑仿真**:

- 使用 Quartus II 的仿真工具进行功能验证,确保设计符合预期。

12. **下载和部署**:

- 最后,将优化后的逻辑下载到选定的 PLD 器件中,进行硬件测试。

这个指南提供了从项目创建、器件选择到实际设计的完整流程,对于初学者来说,是一个循序渐进的学习和实践过程。理解并掌握这些步骤,有助于在实际项目中高效地运用 Quartus II 进行 FPGA 和 CPLD 的设计。

1381 浏览量

380 浏览量

122 浏览量

2012-08-06 上传

104 浏览量

2008-12-26 上传