FPGA设计技巧:时序分析与电路设计详解

需积分: 9 24 浏览量

更新于2024-07-17

收藏 2.79MB PDF 举报

"FPGA设计技巧"

在FPGA设计中,理解和掌握各种技巧至关重要,这将直接影响到设计的性能、可靠性和可维护性。本资源详细介绍了FPGA设计的基础知识,包括时序分析、常见电路设计以及多时钟域设计等方面。

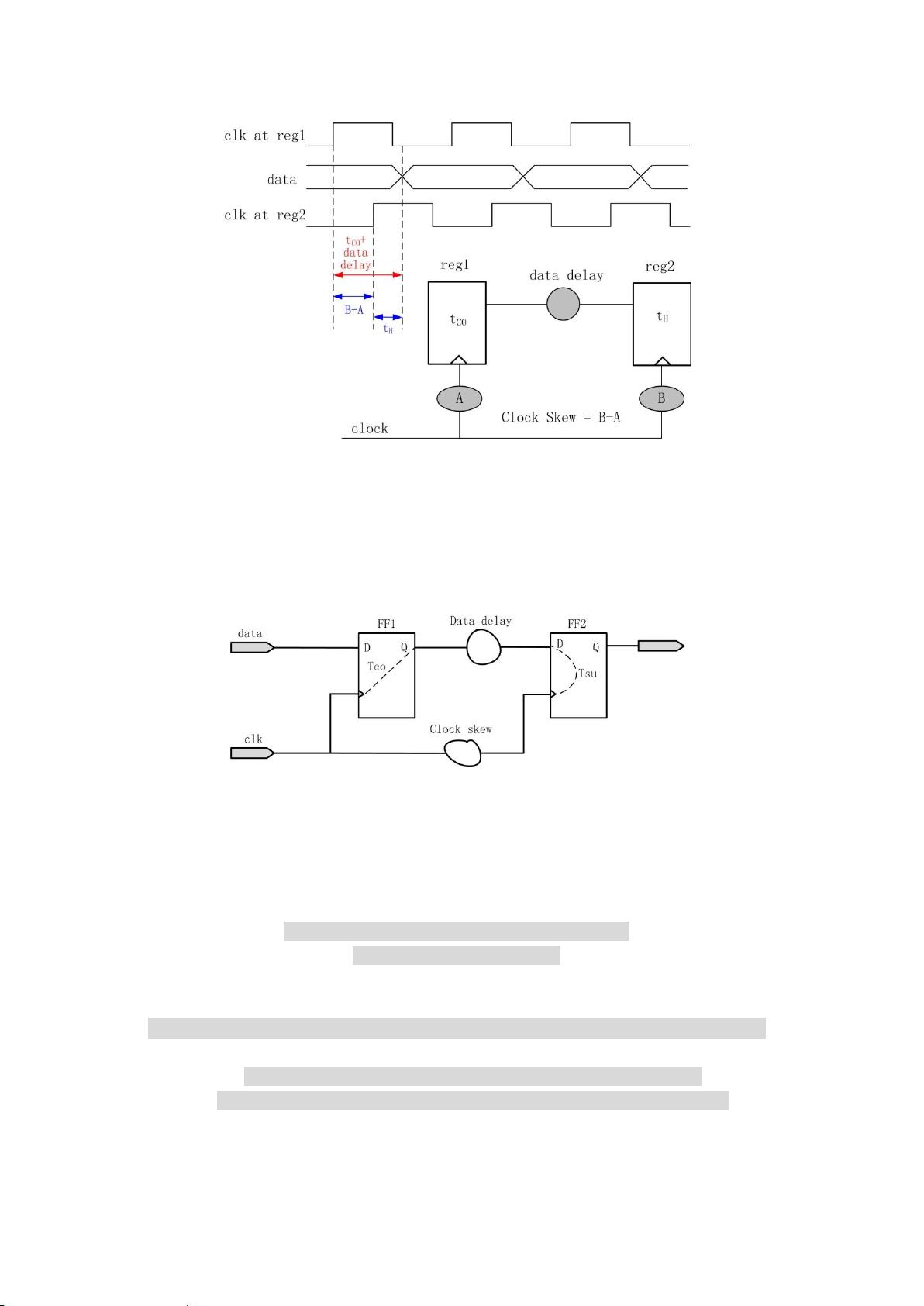

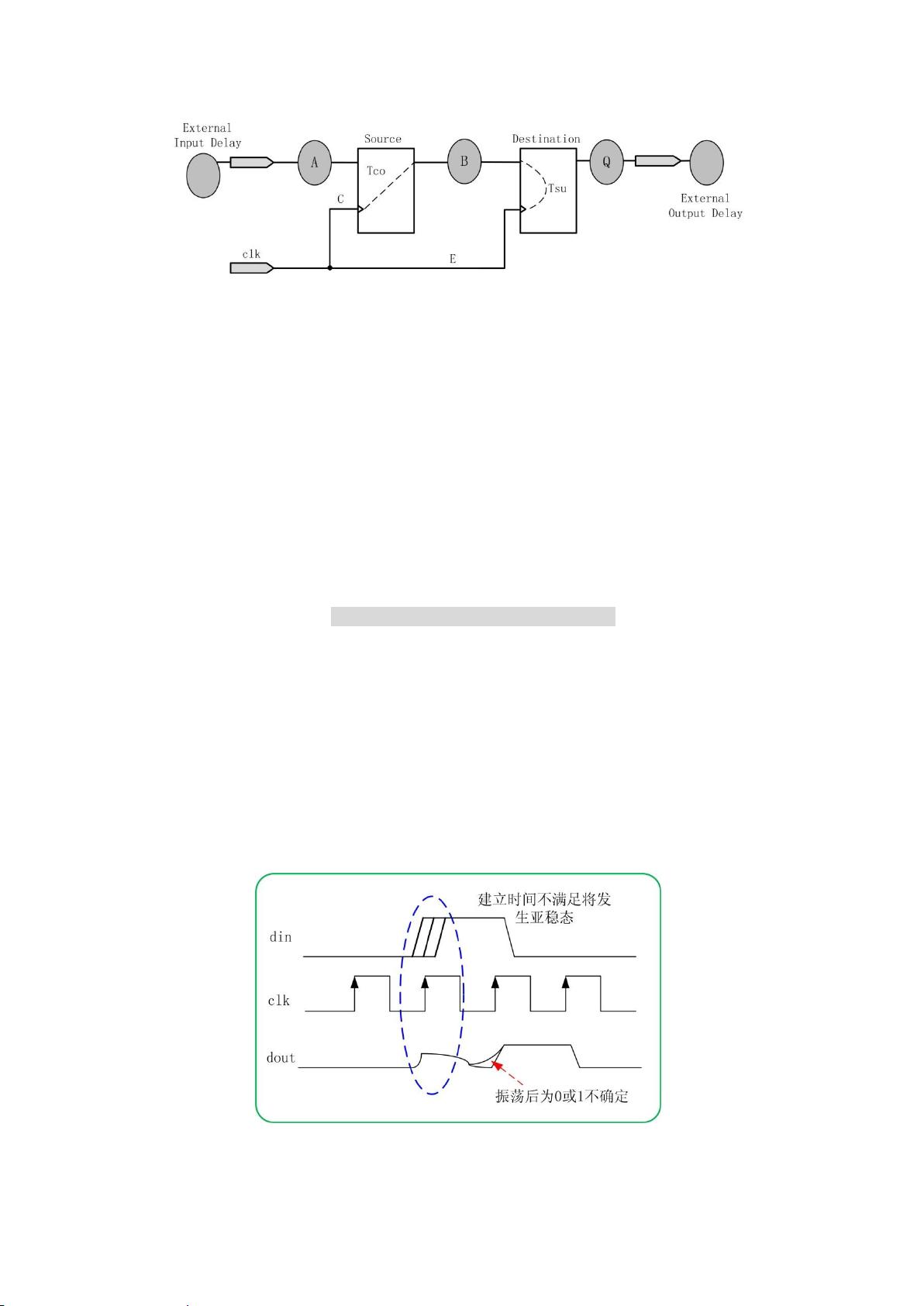

1. 时序分析是FPGA设计的核心部分,它涉及到了建立时间(tSU)和保持时间(tH)的概念。建立时间是指数据必须在时钟边沿之前稳定的时间,以确保正确捕获;而保持时间则规定了数据在时钟边沿之后应继续保持稳定的时间。理解这两个参数对于确保电路的正确工作至关重要。此外,时序分析还包括时钟输出延时(tCO),引脚到引脚的延时(tPD),时钟 skew 和 Slack,以及计算最大频率(FMAX)的方法。

2. 常用电路设计方面,包括了寄存器、组合逻辑、双向端口和三态信号的建模。寄存器电路建模用于数据的存储和传输,组合逻辑建模则处理无记忆性的逻辑运算。多路开关(多路复用器和多路解复用器)用于选择和分配输入/输出。计数器和分频器是数字系统中的基本组件,其中二进制计数器、分频器、双沿计数器和Gray码计数器等提供了不同的计数功能。移位寄存器和桶形移位寄存器用于数据的移动和处理。时钟使能电路控制数据处理的时序,而边沿检测电路用于检测信号的变化。

3. 同步复位和异步复位是FPGA设计中的重要概念。同步复位通常在时钟边沿进行,优点是简化了时序分析,但可能引入额外延迟;而异步复位在任何时候都能复位电路,响应速度更快,但可能导致毛刺和时序问题。为了克服这些问题,需要采用复位同步电路和复位分配技术,以及过滤复位毛刺,确保系统的稳定性。

4. 在多时钟域设计中,需要特别关注亚稳态问题,因为不同时钟域之间的数据传输可能导致不稳定状态。解决这一问题通常需要采用同步技术,如边沿检测和时序协调的复位撤除,以确保数据在不同时钟域间的正确传递。

5. 设计异步多时钟系统时,除了上述技巧外,还需要考虑电源管理、功耗优化以及布局布线策略。综合和描述技巧可以帮助优化设计,减少时序约束冲突,并提高设计效率。

FPGA设计涉及多个层面,从基本的时序分析到复杂的多时钟域设计,都需要设计师深入理解和熟练掌握。通过学习这些技巧,可以提高FPGA设计的成功率,同时实现高效、可靠的系统。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2013-01-06 上传

2010-02-06 上传

2009-11-18 上传

2019-04-19 上传

2022-01-09 上传

2024-04-24 上传

樱木花道長

- 粉丝: 41

- 资源: 4

最新资源

- Effective C++ 第2版(中文版).pdf

- verilog+HDL.pdf

- 汇编DEBUG命令使用解析及范例大全

- Instructor’s Solution Manual

- 2010年英语考研大纲词汇

- 华为笔试题含答案 [C]

- 游戏编程之单例类与对象工厂的简单介绍与实现

- ARM嵌入式WINCE实践教程 pdf

- linux系统移植(很详细的移植文档哦) pdf

- 系统托盘Shell_NotifyIcon

- mfc实现系统托盘c++

- VERILOG快速入门

- 《计算机应用基础》习题参考答案.doc

- CC1110中文资料(无线部分)

- ExecutableLinkableFormat.pdf

- 笔记本电脑维修指导手册