Verilog优化设计:整数与小数分频器的探索

需积分: 9 139 浏览量

更新于2024-07-23

收藏 191KB DOC 举报

"本文主要探讨了滤波器设计中的一个重要组成部分——分频器的设计方法,尤其是整数和小数分频器。通过Verilog硬件描述语言进行优化设计,实现了偶数、非50%占空比及50%占空比的奇数、半整数分频器,并对任意小数分频器进行了详细的设计和优化。通过QustusⅡ软件进行仿真验证了设计的可行性。"

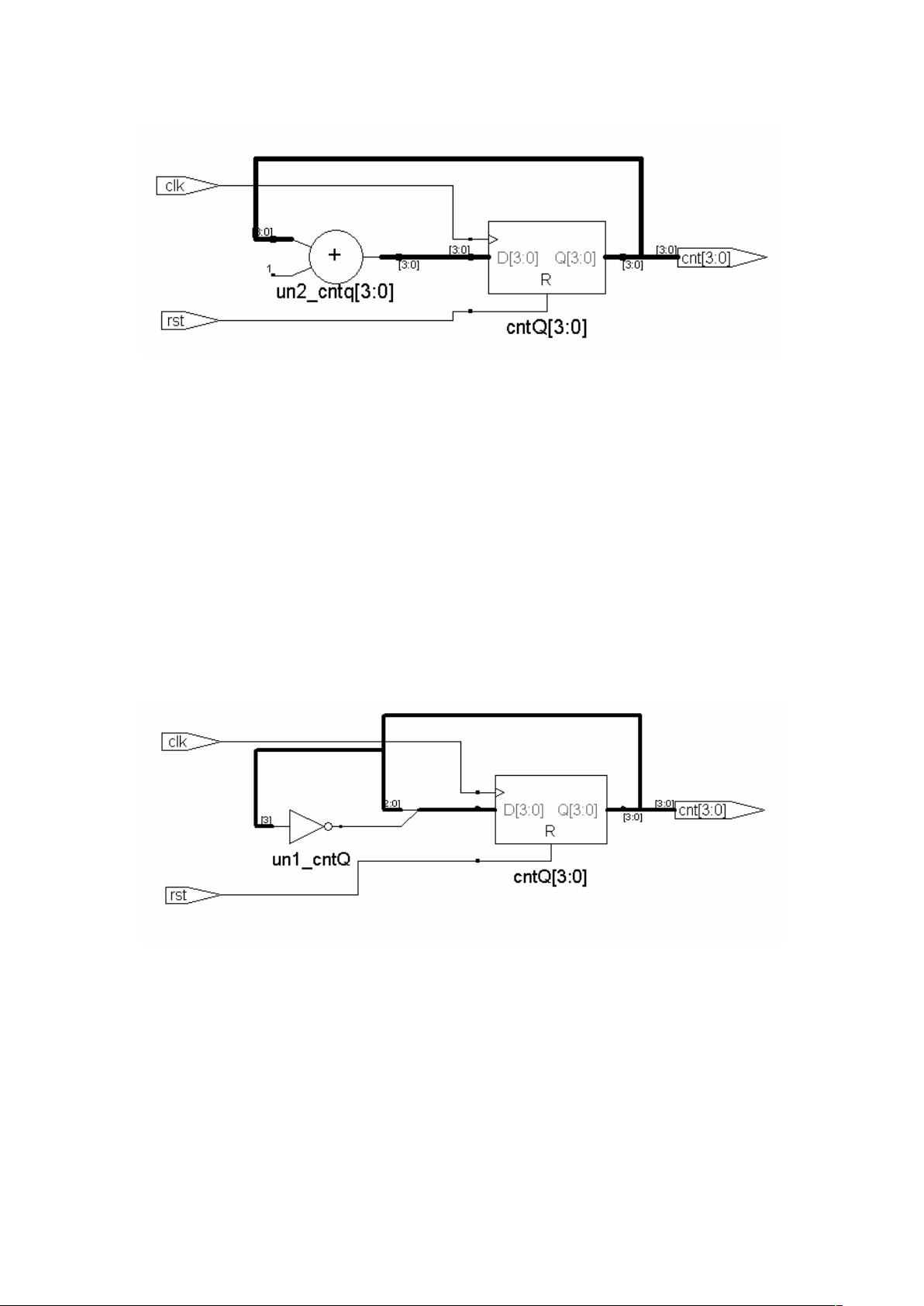

在电子系统中,滤波器是用于处理信号的关键元件,而分频器作为滤波器的一部分,能够改变输入信号的频率。本文首先介绍了分频器的基本概念,包括时序电路设计中的毛刺问题及其消除方法,以及计数器在分频器设计中的核心作用。

第二章深入到具体类型的分频器设计,涵盖了偶数分频器、非50%占空比的奇数分频器、50%占空比的奇数分频器以及半整数分频器。偶数分频器的设计通常相对简单,可以通过基本的计数机制实现。非50%占空比的奇数分频器设计需要考虑输出脉冲的宽度,而50%占空比的奇数分频器则需保证输出脉冲的对称性。半整数分频器的设计则更加复杂,需要精确控制输出频率与输入频率之间的比例。

第三章的重点在于任意小数分频器的设计,这是滤波器设计中的一大挑战。任意小数分频器的工作原理是通过连续的整数分频和位移操作来实现任意小数的频率分频。Verilog HDL被用来实现这一设计,它允许精确地描述数字逻辑电路,便于硬件的优化和综合。通过Verilog代码,可以创建灵活且高效的分频器结构,以适应各种不同的频率需求。

最后,通过QustusⅡ软件进行的仿真验证了所提出的分频器设计方案的有效性和可靠性。这表明,采用Verilog优化设计的分频器不仅满足了功能需求,还可能在实际硬件实现中实现高性能和低功耗。

这篇论文提供了一套完整的滤波器分频器设计方法,包括理论基础、具体实现和优化策略,对于理解和设计滤波器系统具有重要的指导价值。同时,该研究也对其他领域的数字信号处理和时钟管理应用具有借鉴意义。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2008-09-06 上传

2024-01-19 上传

2021-10-04 上传

2009-03-13 上传

2022-07-14 上传

2021-09-10 上传

baidu_16661229

- 粉丝: 0

- 资源: 1

最新资源

- UTD Comet Calendar-crx插件

- linuxboot:LinuxBoot项目正在努力使Linux能够在所有平台上替换固件

- elk-examples:麋鹿的示例集合

- SoftwareArchitect:通往软件架构师的道路

- Challenges in Representation Learning: Facial Expression Recognition Challenge(表征学习中的挑战:面部表情识别挑战)-数据集

- foundryvtt-lexarcana

- interpy-zh::blue_book:《 Python进阶》(中级Python中文版)

- 水平滚动菜单(Menu)效果

- food-drinkweb

- LED.zip_单片机开发_C/C++_

- distributed-mining-github

- Spring 2.0 技術手冊

- 信呼在线客服系统 1.0.0

- ant-design-pro-V5-multitab:基于 ant design pro V5 版本实现多标签切换 基于umi插件 umi-plugin-keep-alive 实现 (目前只支持layout

- pinba服务器:简单快速的pinba服务器,在Clickhouse中存储

- webgaim-开源