UNIVERSITY OF MARYLAND MEMORY SYSTEM SIMULATOR MANUAL – 6

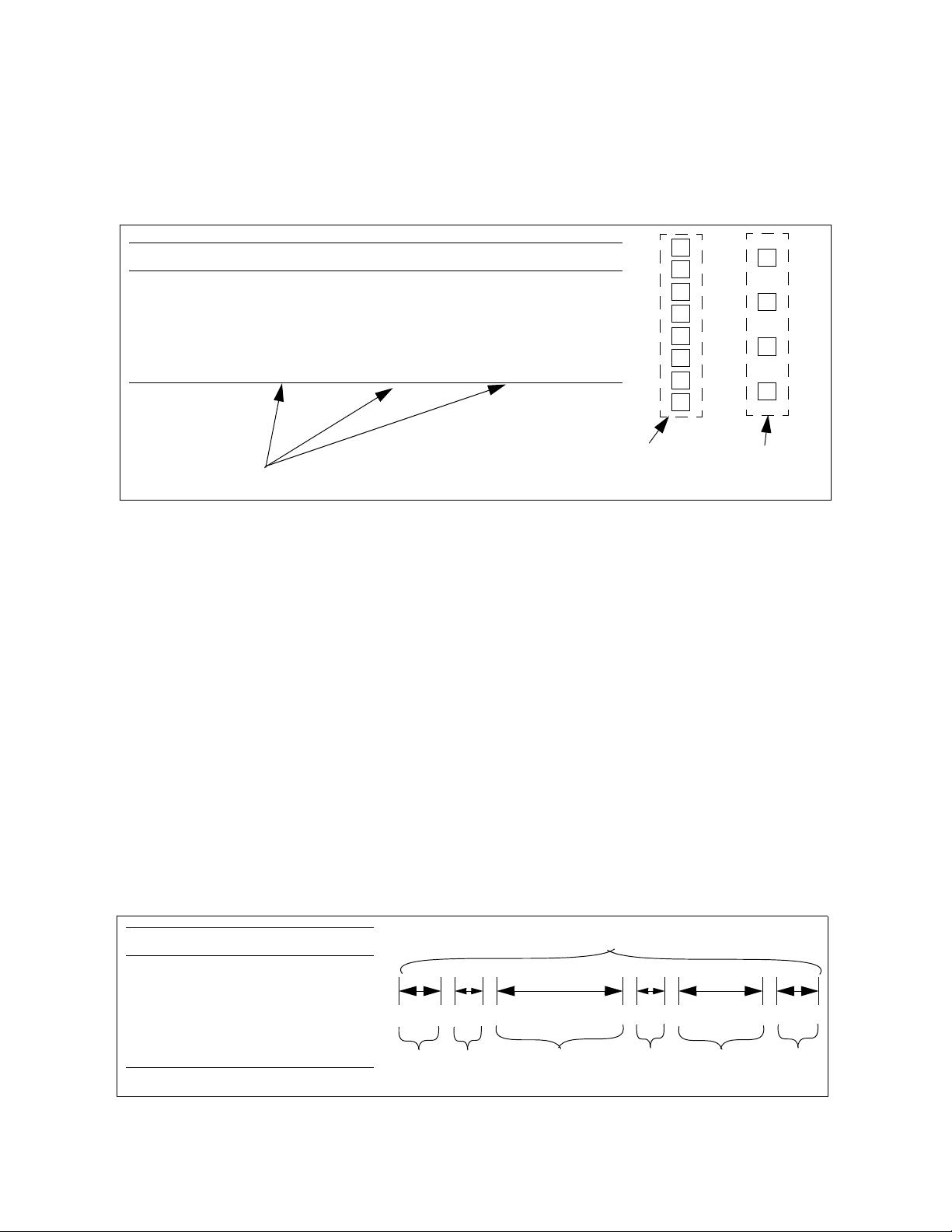

address 4 different banks, 13 bits to address 8192 rows, and 2 bits to address 4 ranks of memory. Altogether, 29 bits of

physical address is used here to address 512 Megabyte of memory. The address mapping policy illustrated in figure 5 is

optimized for an open page memory system, since the column ID’s are mapped to the lowest order bits, and multiple

accesses to the same array of memory would most likely be mapped to different columns within the saw row and same

bank of DRAM devices. Alternative memory address mapping schemes may achieve a higher degrees of performance

depending on the configuration and row buffer management policy. Finally, the memory addressing scheme presented in

figure 5 is specified for a single channel of memory. Multi-channel memory require an address mapping policy that can

adequately distribute the memory accesses to different channels.

D.BASIC TIMING PARAMETERS

In any DRAM memory-access protocol, a set of timing parameters is used to characterize various command

durations and latencies. Although the exacting desciption of a full and complete protocol requires the use of tens of

different timing parameters, a generic protocol can be well described with a subset of the timing parameters. The timing

parameters used in the simulation framework are summarized in table 1

Parameter Description Illust.

t

Burst

Data Burst duration. Time period that data burst occupies on the data bus. Typically 4 or 8 beats of

data. In DDR SDRAM, 4 beats of data occupies 2 full cycles. Also known as t

BL

.

figure 7

t

CAS

Column Access Strobe latency. Time interval between column access command and data return by

DRAM device(s). Also known as t

CL

.

figure 7

t

CMD

Command transport duration. Time period that a command occupies on the command bus as it is

transported from the DRAM controller to the DRAM devices.

figure 6

t

CWD

Column Write Delay. Time interval between issuance of column write command and placement of

data on data bus by the DRAM controller.

figure 7

t

DQS

Data Strobe turnaround. Used in DDR and DDR2 SDRAM memory systems. Not used in SDRAM

or Direct RDRAM memory systems. 1 full cycle in DDR SDRAM systems.

figure 12

t

FAW

Four bank Activation Window. A rolling time frame in which a maximum of four bank activation

may be engaged. Limits peak current profile.

figure 16

t

RAS

Row Access Strobe. Time interval between row access command and data restoration in DRAM

array. After t

RAS

, DRAM bank could be precharged.

figure 6

t

RC

Row Cycle. Time interval between accesses to different rows in same bank

t

RC

= t

RAS

+ t

RP

figure 7

t

RCD

Row to Column command Delay. Time interval between row access command and data ready at

sense amplifiers.

figure 6

t

RFC

Refresh Cycle. Time between refresh commands or refresh command and row activation. figure 10

t

RRD

Row activation to Row activation Delay. Minimum time interval between two row activation

commands to same DRAM device. Limits peak current profile.

figure 15

t

RP

Row Precharge. Time interval that it takes for a DRAM array to be precharged and readied for

another row access.

figure 9

t

WR

Write Recovery time. Minimum time interval between end of write data burst and the start of a

precharge command. Allows sense amplifiers to restore data to cells

figure 8

Table 1: Summary of DRAM Timing Parameters