机载雷达信号处理模块的创新设计与FPGA-DSP融合策略

107 浏览量

更新于2024-08-31

收藏 285KB PDF 举报

现代雷达信号处理模块的设计与实现面临了诸多挑战,特别是在机载雷达数字信号处理机中,由于数据输入量大、工作模式复杂以及信息处理需求多样,传统的基于任务的设计方法已显得不足。这种传统方法往往受限于硬件平台,难以适应算法升级和处理任务的多样性,例如,硬件升级可能导致运算量增加、数据存储压力增大,甚至影响控制流程。

为了解决这些问题,设计师们正在探索更灵活和高效的解决方案。雷达信号处理机的设计需要明确其核心目的,即在空空和空地模式下,处理AD数据,包括数字脉压处理、数据格式转换、加权降噪、匹配滤波或相参积累、CFAR处理、跟踪测角等,并在必要时进行图像成像处理。为了实现这些复杂任务,通常采用高性能的FPGA和DSP芯片,它们可以并行处理大量数据,提高系统效率。

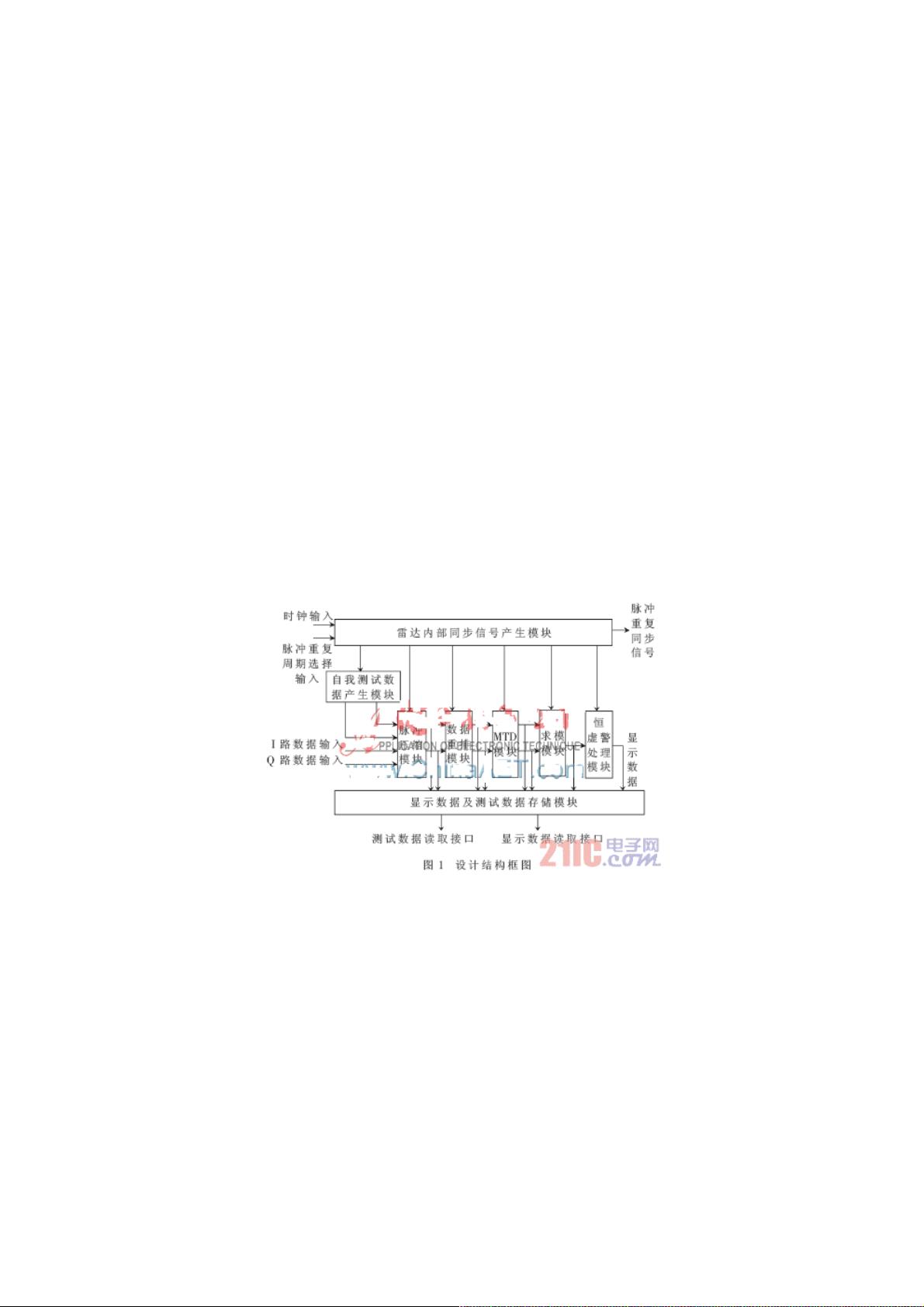

设计的关键在于模块化,如图1所示,包括以下几个关键模块:

1. 正交采样模块:负责信号的初始转换,通过A/D转换器将中频信号转换为I/Q信号,采样速率和精度直接影响后续处理的质量,必须控制在可接受的误差范围内,以减少失真。

2. 脉冲压缩模块:针对发射功率限制,通过匹配滤波器技术,将接收到的宽脉冲信号压缩为窄脉冲,提升距离分辨率和探测范围,优化雷达性能。

3. MTD(Minimum Detectable Target)模块:利用滤波器技术,减少干扰和噪声,确保目标检测的可靠性。

4. 数据格式转换和处理模块:执行数据的组织和优化,以便于后续算法的运行,可能涉及采样率转换、频率变换等操作。

5. 相关图像处理模块:针对空地模式,进行地图相关成像,如RBM(Range-Bearing Mapping)和SAR(Synthetic Aperture Radar)处理。

通过采用高速DSP和FPGA的结合,以及模块化的系统结构,现代雷达信号处理模块设计旨在提升系统的灵活性、通用性和处理能力,以应对现代雷达复杂多变的工作环境。这不仅能够满足当前的需求,也为未来的技术升级和扩展提供了坚实的基础。

548 浏览量

147 浏览量

200 浏览量

2024-11-01 上传

181 浏览量

158 浏览量

183 浏览量

413 浏览量

weixin_38721119

- 粉丝: 10

- 资源: 925

最新资源

- Perl 二十四小时搞定

- 简明 Python 教程 《a byte of python》中译本

- 3G技术普及手册(华为内部版)

- 广告公司固定管理系统-需求分析

- 相当全面的J2EE面试题!!!

- rails_plugins_presentation.pdf

- SOA 案例研究:不同应用程序的集成组织

- ajax--dwr测试

- Servlet_JSP

- java struts 教程

- Struts 中文简介

- 五星_中兴《GSM移动通信基本知识》_

- 数据库第四版答案 大学教材课后答案

- 正则表达式30分钟入门教程

- 三级C语言上机南开100题(2009年终结修订word版).doc

- 基于IBM DS4500磁盘阵列的配置实验