HLS优化:FPGA实现深度学习中卷积神经网络的硬件友好设计

"本文主要探讨了基于HLS(硬件描述语言)的高效深度卷积神经网络(DCNN)在FPGA(现场可编程门阵列)上的实现方法,重点介绍了如何考虑硬件友好性和网络小巧的设计思路,特别是针对卷积操作中的填充方式选择,包括'FULL'、'SAME'和'VALID'三种填充方式。"

深度卷积神经网络(DCNN)在图像识别、计算机视觉等领域中起着关键作用,而FPGA因其并行计算能力和低功耗特性,成为实现DCNN硬件加速的理想平台。在FPGA上实现DCNN时,设计思路需兼顾硬件效率和模型的计算需求。首先,我们需要关注网络结构的优化,使其适合硬件实现,这通常意味着要减少计算复杂度和内存需求。

1.1 考虑硬件友好和网络小巧的设计思路

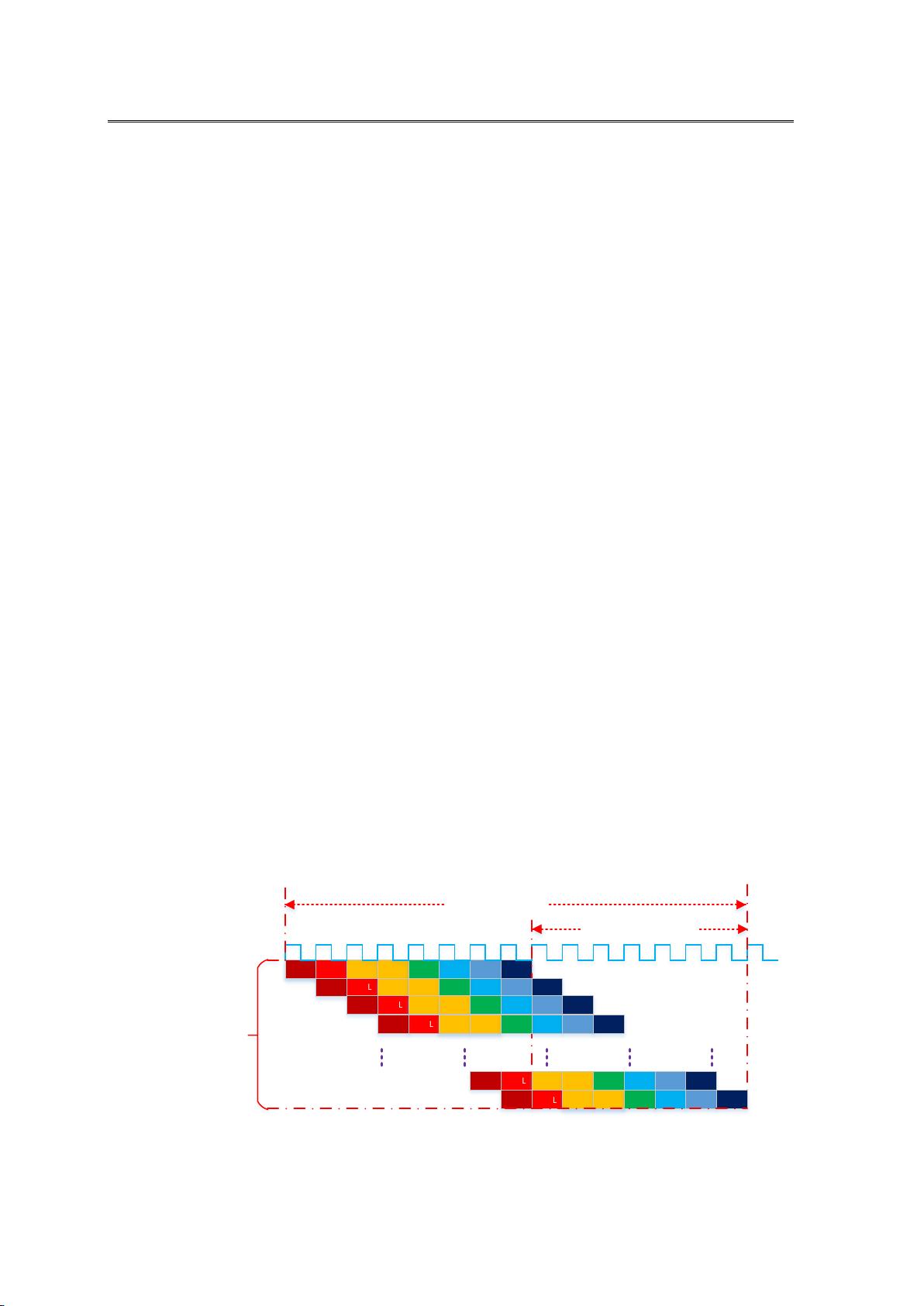

1.1.1 填充方式的选择对硬件实现的影响至关重要。填充(Padding)是为了保持输出特征图的尺寸不变或调整卷积的计算区域。对于'FULL'填充,它在图像边缘填充K-1维的0,确保每个位置都能进行卷积,输出尺寸为(R+K-1)×(C+K-1),但增加了额外的计算量和存储需求。

1.1.2 'SAME'填充则保持输入和输出特征图尺寸相同,通过不均匀填充0,使得卷积核可以在图像边界处完全覆盖,减少了计算区域的边缘处理,同时保持了尺寸的一致性。

1.1.3 'VALID'填充不进行填充,仅在图像内部进行卷积,输出特征图尺寸为(R-K+1)×(C-K+1),这种方式减少了计算量,但可能导致输出尺寸减小,可能不适合需要特定输出尺寸的应用。

1.1.4 在FPGA实现时,选择合适的填充方式可以有效控制硬件资源的使用和计算效率。例如,'VALID'填充减少了填充的计算,节省了硬件资源,但可能导致计算步骤增多,影响整体性能。

1.1.5 此外,考虑到FPGA的并行计算能力,选择较大的卷积步进(Stride)可以进一步减少计算量,但可能会导致信息损失,需要根据具体应用需求权衡。

1.1.6 在进行硬件实现时,还需要注意避免大量的乘除运算,因为它们在硬件中执行较慢,会增加延迟和资源消耗。通过精心设计网络结构和选择合适的填充方式,可以简化计算,提高执行速度。

实现基于HLS的FPGA上的高效DCNN,需要在满足模型精度的同时,充分考虑硬件资源限制,优化网络结构,合理选择填充方式,以达到最佳的性能与资源利用率。通过这样的设计思路,可以在保证模型性能的前提下,实现快速且高效的DCNN硬件加速。

2020-08-09 上传

2024-07-11 上传

2024-10-31 上传

2023-03-22 上传

2024-11-15 上传

2024-02-02 上传

2024-12-21 上传

贼仙呐

- 粉丝: 32

- 资源: 296

最新资源

- ema-for-mei-js:TypeScript中MEI的EMA实现(同构)

- cplusplus-helloworld:这是我的第一个C ++项目

- ng-bootstrap-loading:角度页面的加载蒙版显示功能

- johaneous.github.io:韦伯斯特无删节词典(免费的En-En-Cht词典)

- 超级万年历记录时间过程与节气,纪念日的C++版本的实现

- api-cng

- 基于Docker的MySQL+Bind9-dlz一主多从高可用DNS方案.zip

- node-webapp-step1:用于学习外语学习网络应用程序开发

- CalDash:CS294 Web应用程序

- 个人档案袋:个人档案库

- quickplot:这是quickplot模块的测试版,是pandas,matplotlib和seaborn的包装,用于快速创建漂亮的Viz进行分析

- DlvrMe-API

- azuredemoapp

- test2-solutions:CMP237 测试 2 实践解决方案

- emsi-devops:这是霍尔伯顿学校项目的资料库

- Finite-State-Machine-Model:延续2018年夏季开始的项目,其中Graeme Zinck和我在Ricker博士的带领下制作了Finite State Machines的专业模型,以实施理论并为正在进行的研究提供了试验平台。 允许生成FSM,并执行多项操作(例如“产品”和“并行组合”),并且目前已集成了U结构以用于进一步分析。 目前正在为Mount Allison大学的Ricker博士开发此工具。