MIPS微处理器实验:同步与异步数据RAM设计与验证

需积分: 0 130 浏览量

更新于2024-07-01

收藏 4.23MB PDF 举报

在MIPS微处理器设计实验中,学生需要完成不同类型的数据存储器模块的设计和实现。实验的主要内容包括:

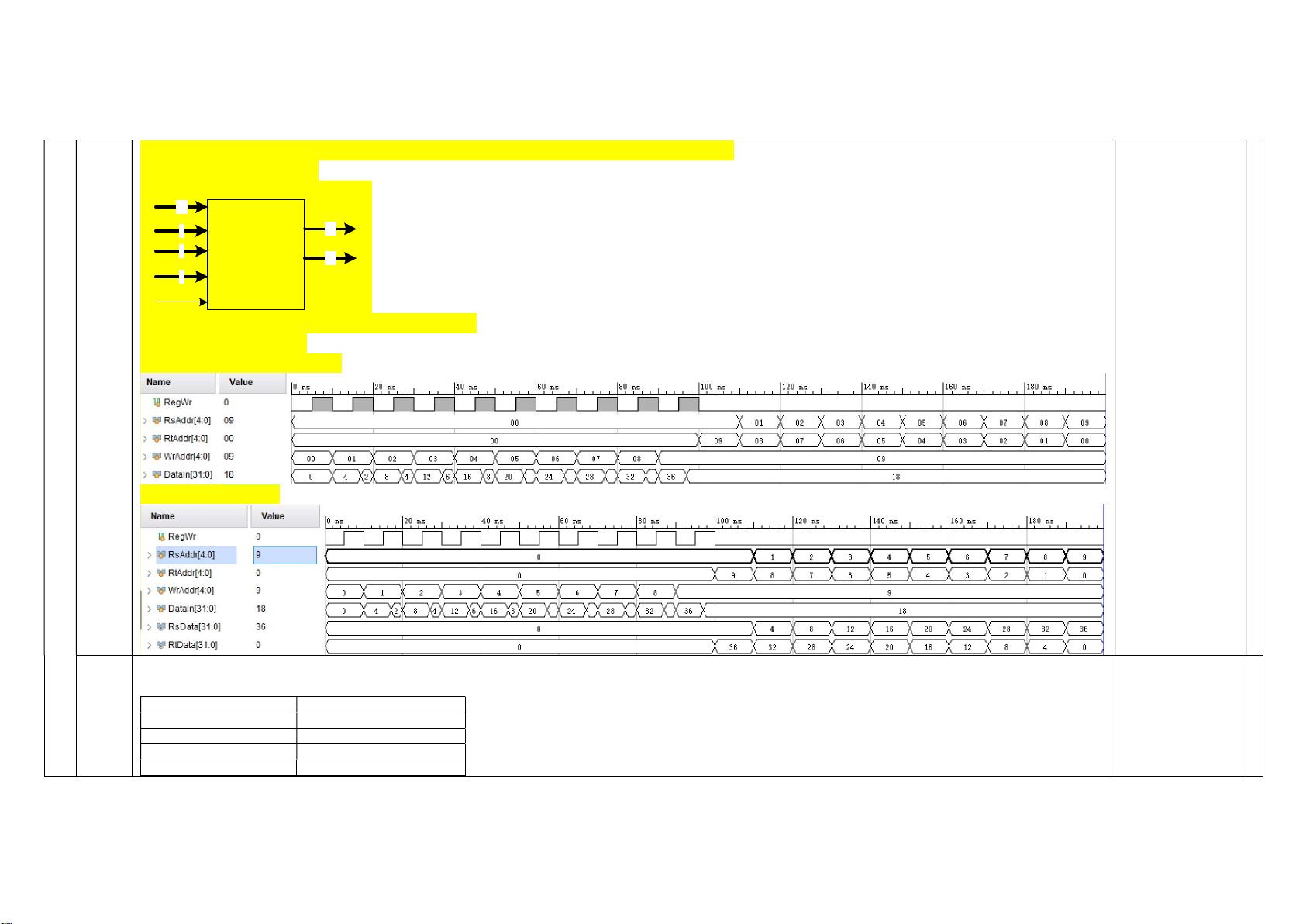

1. **模块类型实验**:分为三个部分,分别是同步(SyncRAM.v)、异步同步(DataRAM.v)和异步输出(AsyncRAM.v)数据存储器。同步数据存储器(SyncRAM)在时钟上升沿进行操作,地址线Addr有n位宽,输入数据线DataIn有m位宽,写控制信号MemWR用于区分读写操作,高电平表示写入,低电平表示读取,而DataOut作为输出数据线有保持功能。

- **SyncRAM.v**:示例代码展示了如何设计一个同步RAM,其特点是操作与系统时钟同步,输入和输出均在时钟上升沿触发。参数n和m分别定义了地址和数据的宽度。实验要求学生编写并测试此模块的正确性,包括实例化32个存储单元,设置初始值为0,并创建正确的输入输出波形,确保数据的一致性。

2. **异步同步数据存储器(DataRAM)**:与SyncRAM类似,但Write控制信号在上升沿有效。同样有地址线Addr、输入数据线DataIn和DataOut输出,但时钟不参与同步。仿真激励文件dataram_sim.v用于驱动存储器,检查存储单元的正确读写。

3. **异步输出数据存储器(AsyncRAM)**:在这个模块中,Write控制信号在输入信号的上升沿有效,这意味着写操作的时机不是由时钟决定,而是由外部输入决定。这增加了设计的复杂性,需要考虑不同输入信号之间的逻辑关系。

在整个实验中,学生将通过这些不同的RAM设计,学习和实践基础的硬件描述语言(如Verilog或 VHDL),以及掌握数据存储器的基本工作原理和接口设计。此外,他们还将测试并验证模块的功能,包括正确处理地址、数据和控制信号,以及输出数据的保持功能。这些技能对于理解和设计嵌入式系统、数字逻辑电路和计算机体系结构至关重要。

157 浏览量

135 浏览量

2022-08-03 上传

2022-06-20 上传

2022-06-20 上传

628 浏览量

1808 浏览量

224 浏览量

141 浏览量

大禹倒杯茶

- 粉丝: 24

- 资源: 331

最新资源

- PhalconPHP开发框架 v3.2.0

- 登记册

- Data-Structures-and-Algorithms

- SQL_Database

- webthing-rust:Web Thing服务器的Rust实现

- stock_112-数据集

- 三方支付接口自动到账程序 v1.0

- GlicemiaAppMobile

- data-pipeline-kit:数据管道开发套件

- NURBS 曲线:使用给定的控制点、顺序、节点向量和权重向量绘制 NURBS 曲线-matlab开发

- PJBlog2 绿色心情

- centos安装docker-compose

- Ralink 2070/3070芯片 MAC修改工具

- gz-data-数据集

- ExcavationPack

- GF-Space_Invaders:Greenfoot制造的太空侵略者