Vivado入门:创建并添加首个Verilog项目

需积分: 12 22 浏览量

更新于2024-08-28

收藏 5.94MB PDF 举报

本资源是一份详细的教程,旨在指导用户如何使用Xilinx的Vivado工具来创建和实现他们的第一个项目。Vivado是一个功能强大的硬件设计环境,主要用于FPGA和ASIC的设计流程,包括RTL设计和逻辑综合。

首先,用户需要启动Vivado 2018.2桌面图标,由于其内存占用较大,可能需要耐心等待加载。打开Vivado后,步骤如下:

1. 创建新项目:用户会看到一个创建项目对话框,需要指定工程名称和存储位置。选择RTLProject类型,因为它是描述数字逻辑门级行为的基础项目模板,它关注的是寄存器之间的数据流和处理。

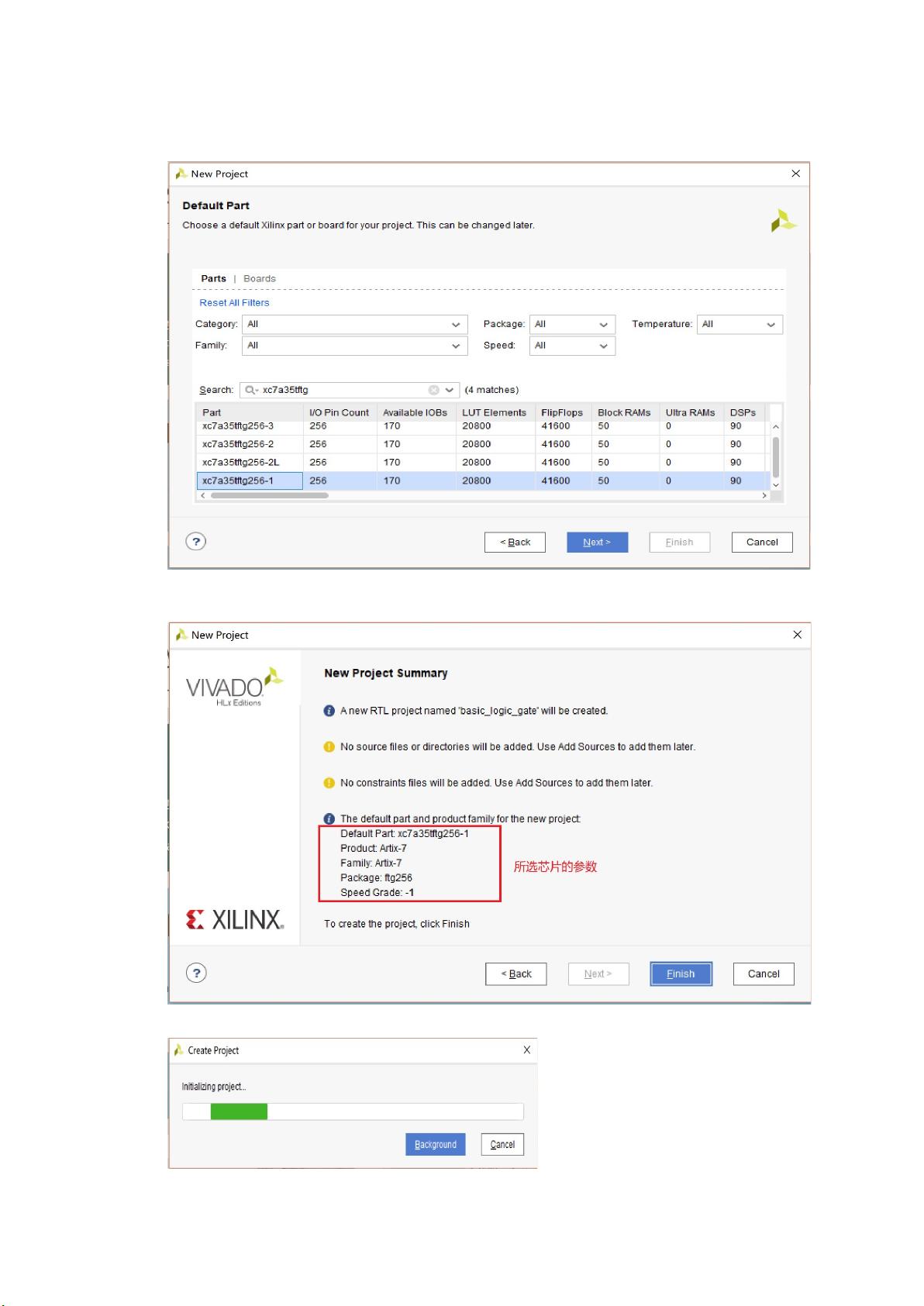

2. 设计设置:添加源文件之前,需要选择合适的芯片型号,这里选择了Xilinx Artix-7 FPGA系列的xc7a35tftg256-1作为软仿真目标。完成基本信息确认后,项目会被自动创建。

3. 添加源代码:在Project Manager中,通过"AddSource"功能添加Verilog源代码,例如命名为"basic_logic_gate.v",确保与工程名一致或区分以便管理。

4. 编写Verilog代码:用户在此阶段需要编写逻辑电路的描述,如实现与门(F1 = a•b)和可能的其他逻辑功能,如F2 = a。在这个过程中,用户需要明确输入(a, b)和输出(F1, F2, F3, F4)的定义,并根据需要添加额外行。

5. 验证和编辑:在Sources视图中,用户会看到已添加的源代码,可以在此编辑实际的代码实现。确保所有逻辑功能都正确无误后,保存并编译。

6. 逻辑综合与仿真:编写的Verilog代码经过Vivado的逻辑综合后,可以进行功能仿真,验证逻辑行为是否符合预期。这一步对调试和优化电路至关重要。

在整个过程中,Vivado提供了直观的界面和强大的功能,使得即使是初学者也能逐步掌握硬件设计的基本流程。通过这个项目,用户将学会如何在Vivado中构建、实现和测试简单的逻辑电路,这是深入学习硬件设计的第一步。

2023-04-23 上传

2021-11-24 上传

2023-04-23 上传

2024-04-16 上传

2024-04-16 上传

2021-05-12 上传

2021-06-16 上传

109 浏览量

点击了解资源详情

x66ccff

- 粉丝: 705

- 资源: 2

最新资源

- sls-nodejs-template:具有ES6语法的无服务器模板

- Santander Product Recommendation 桑坦德产品推荐-数据集

- Zigbee-CC2530实验03SYSCLOCK&POWERMODE实现睡眠定时器

- stocks-ticker:电子垂直股票代号

- grow-together:寻求向孩子介绍新技术,人文和文化的新颖方法

- 软件串口监视AccessPort

- Accuinsight-1.0.5-py2.py3-none-any.whl.zip

- GUI 中的拖动线:GUI 中的线可以拖动-matlab开发

- TextEncryption

- A3JacobDumas.appstudio

- Horiseon:地平线

- 串口通讯ET 200S 1SI模块应用范例.rar

- Nicky Jam Search-crx插件

- SymbolsVideo:SVG中的Symbols视频触发器

- C#桌面程序 获取机器码(CPU信息+硬盘信息+网卡信息)

- US Candy Production by Month 美国糖果月产量-数据集