Vivado HLS设计基础与优化详解

需积分: 0 29 浏览量

更新于2024-06-23

收藏 82.43MB DOCX 举报

"Vivado HLS设计简易概览与实践指南"

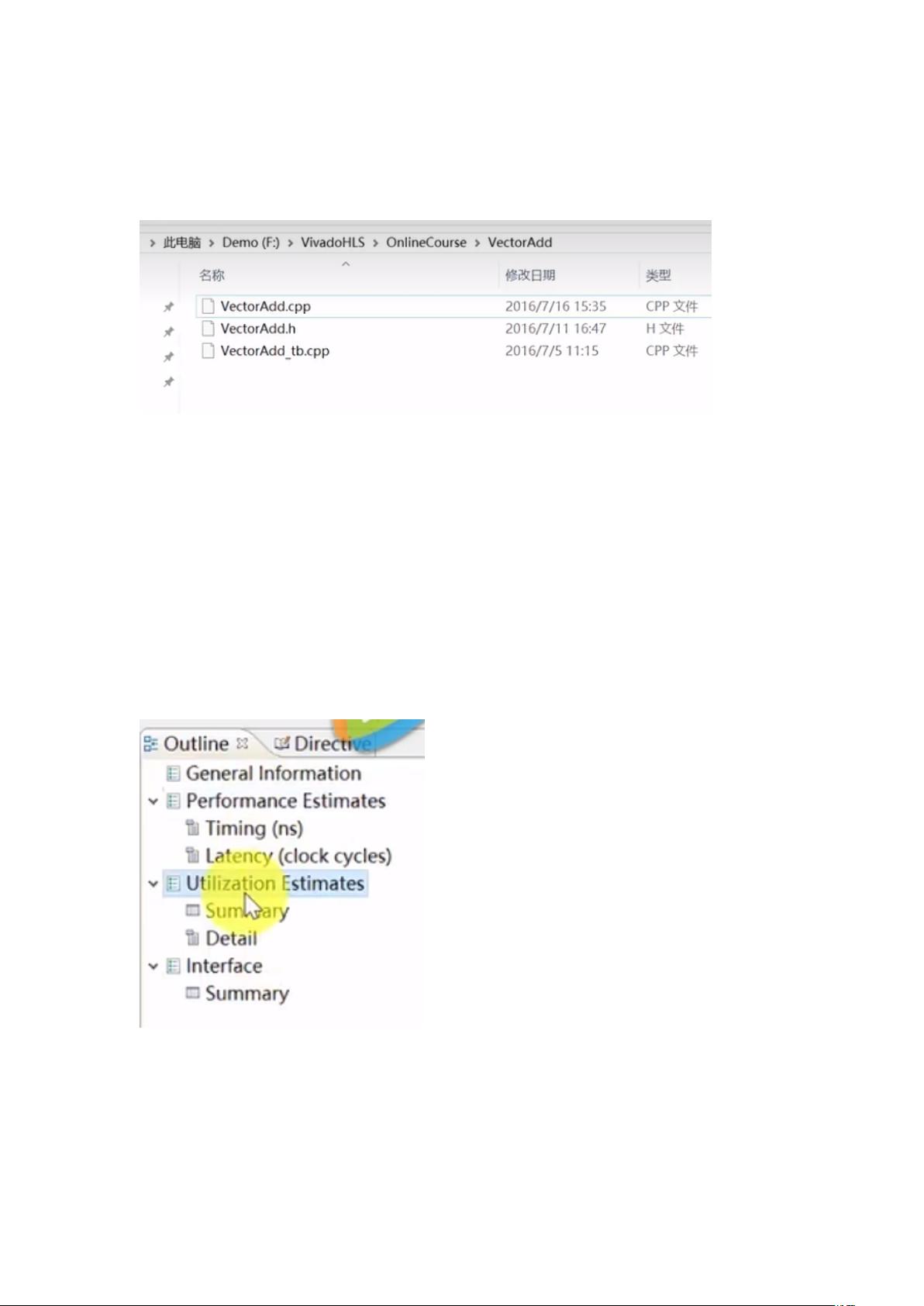

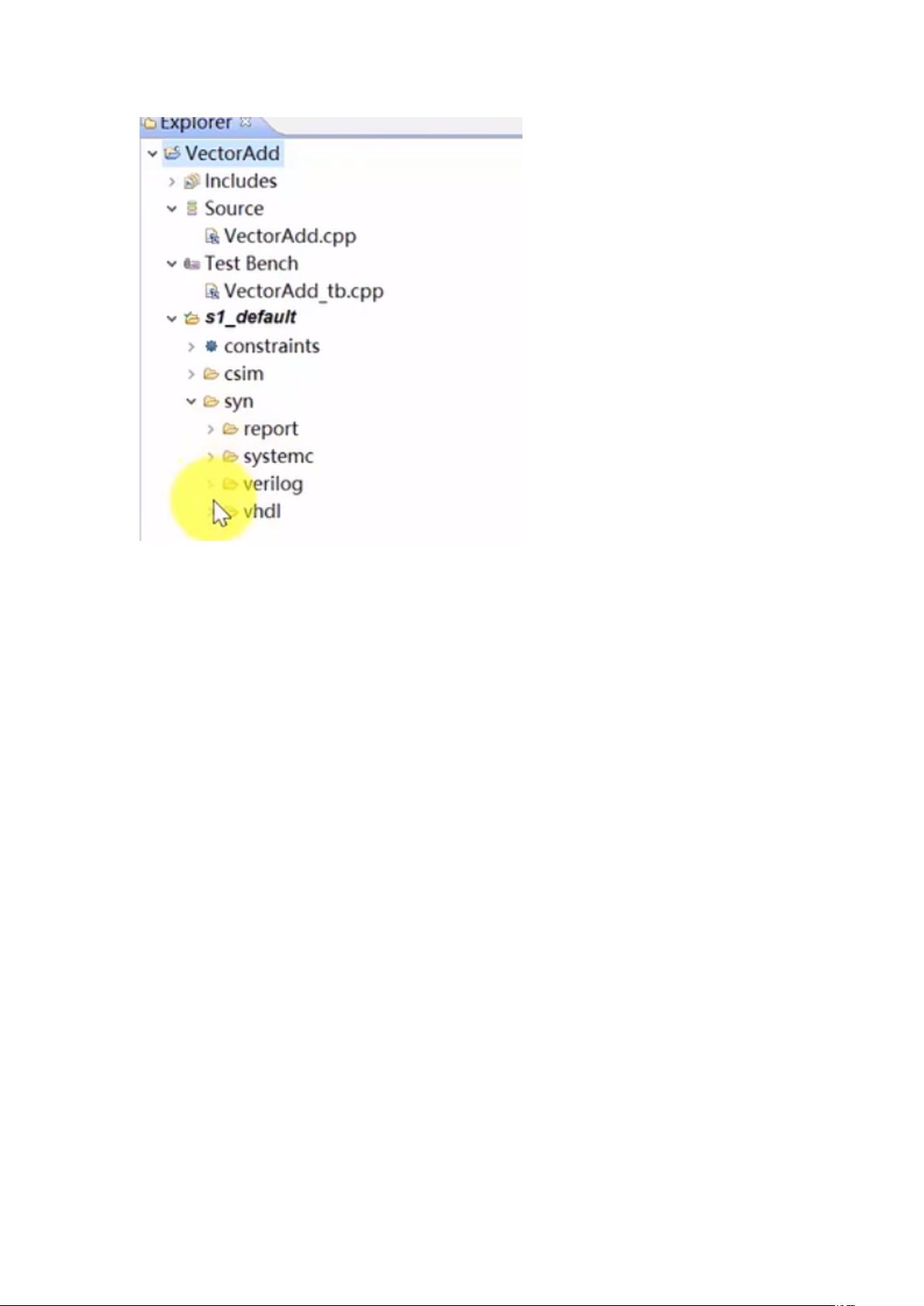

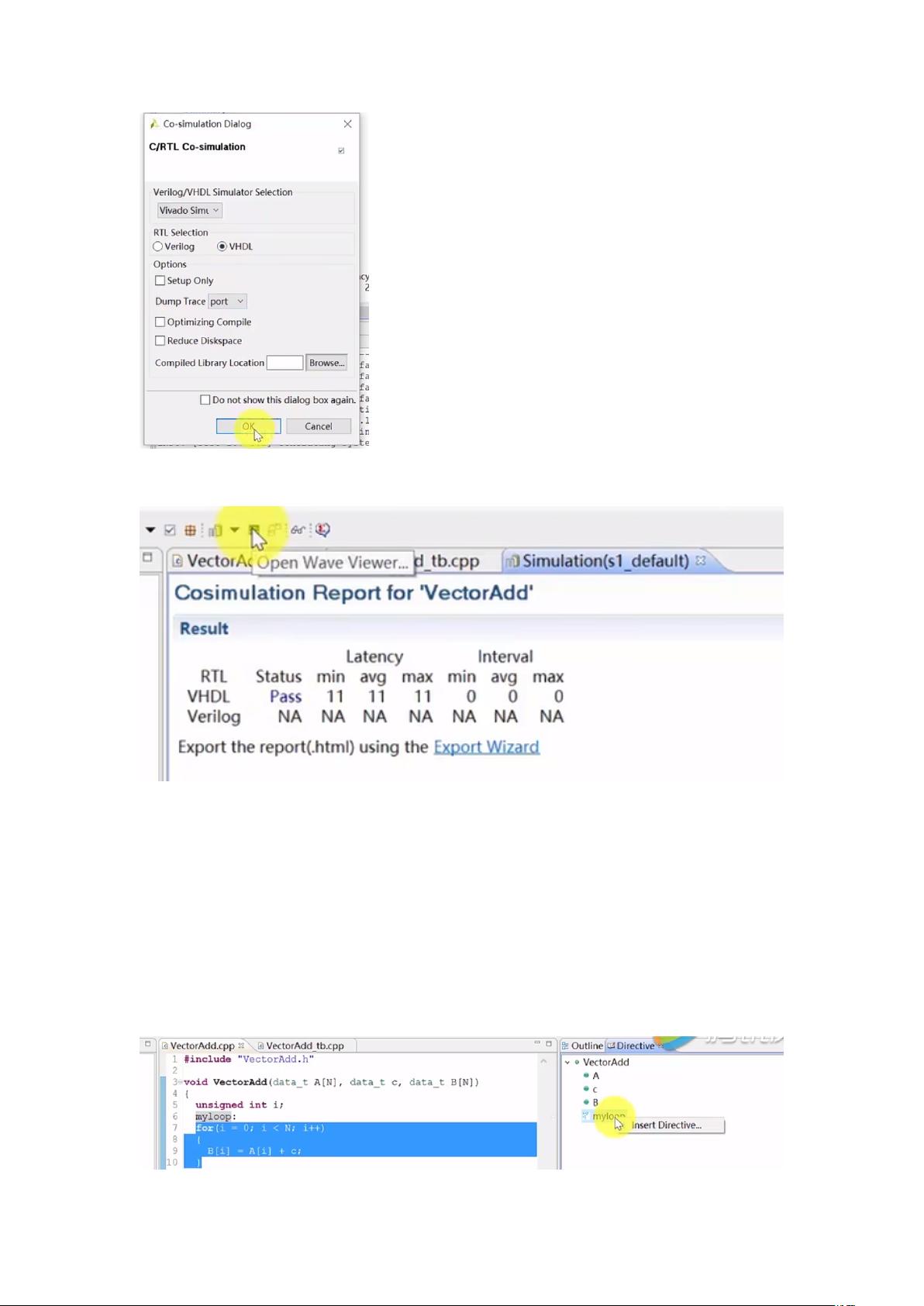

Vivado HLS(High-Level Synthesis)是一款由Xilinx公司提供的工具,它允许软件工程师使用C、C++或SystemC语言来设计和优化FPGA(Field-Programmable Gate Array)应用。通过将高级语言代码转换为硬件描述语言(HDL,如Verilog或VHDL),Vivado HLS简化了FPGA的开发流程,使得算法加速更为便捷。

1. 基本概念

- Latency: 指的是从输入数据到第一个输出数据产生的延迟,衡量单个数据处理的时间。

- Delay: 类似于Latency,表示处理一个输入数据所需的时间。

- Interval: 从第一个输入到第二个输入间的间隔,反映的是系统连续处理数据的能力,即吞吐率。

2. System Generator(SysGen)

SysGen是Xilinx的另一个工具,用于创建基于MATLAB和Simulink的嵌入式系统模型,它支持将这些模型转换为可部署的硬件代码。

3. 软件工程师在算法加速中的角色

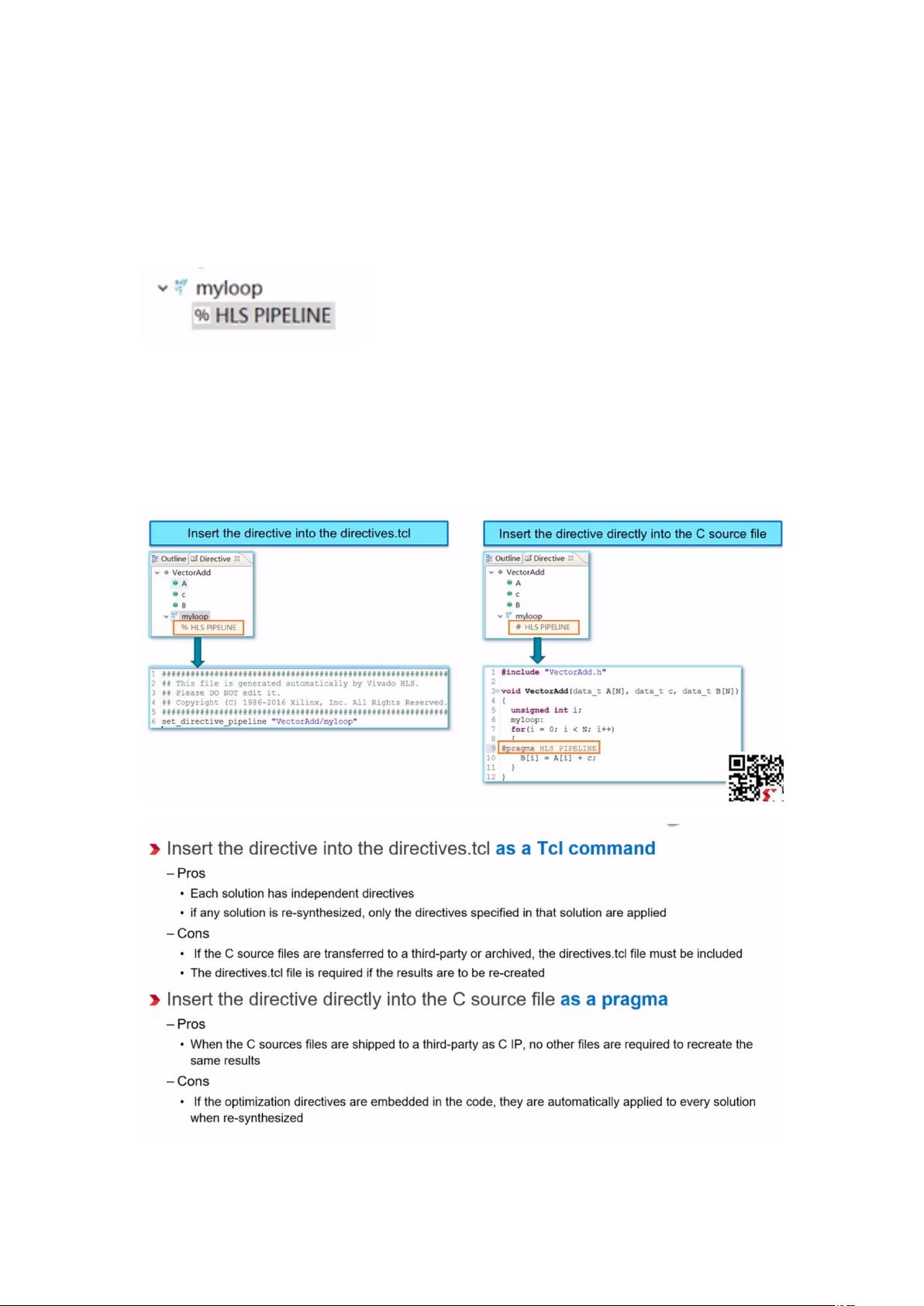

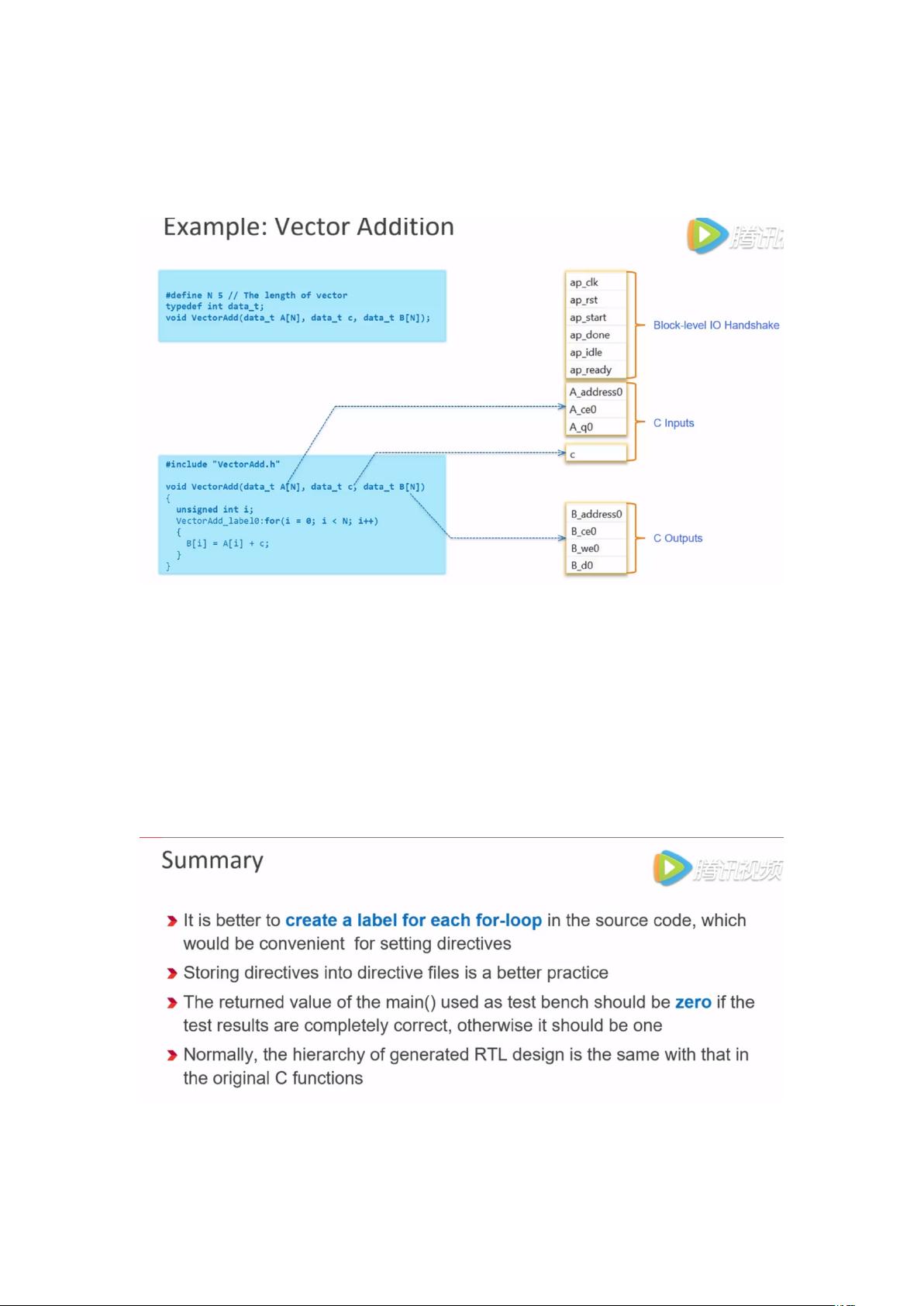

- 使用Vivado HLS进行设计,利用C/C++的编程风格进行硬件综合。

- 优化技巧,包括循环展开(For Loop Optimization)、数组操作优化等。

- 理解不同类型的处理器,如CPU、DSP和GPU的特性:

- CPU:擅长管理、调度任务,适合数据访问、文件管理和人机交互。

- DSP:适合递归和数字信号处理,具有高速乘法器,能高效处理数字信号算法。

- GPU:拥有多个处理器,适合并行处理大量数据流。

4. FPGA的优势与资源

- FPGA关注逻辑资源(LUTs、MUXes、carry chains)、存储资源和DSP blocks。

- LUTs用于实现逻辑运算,如与、或、非;DSP blocks则提供乘法、乘加和逻辑运算功能。

- FPGA的RAM资源可以配置为分布式RAM或块RAM,C代码中的数组可以映射到这些内存结构。

5. HLS设计挑战与解决方案

- 软件工程师需理解FPGA单元功能、算法与硬件的映射以及资源利用率。

- 优化算法以提高资源利用率,关注HLS综合报告,确保生成的HDL代码与硬件有效匹配。

6. HLS工作原理

- EDA工具(电子设计自动化)是HLS的基础,如Vivado HLS中的PSME(Processor System Model Editor)帮助用户观察硬件行为。

通过Vivado HLS,软件工程师可以充分利用FPGA的并行处理能力,实现高效的算法加速,同时减少了对底层硬件细节的理解需求。然而,为了获得最佳性能,仍需掌握一定的硬件知识,优化算法并考虑资源利用率。

点击了解资源详情

471 浏览量

2013-06-13 上传

204 浏览量

150 浏览量

624 浏览量

weixin_43708435

- 粉丝: 0

- 资源: 2

最新资源

- 大酒店员工手册

- xoak-feedstock:一个xoak的conda-smithy仓库

- 文件夹

- 易语言源码易语言使用脚本开关系统还原源码.rar

- SleepDisplay:命令行工具可让您的Mac显示器直接进入睡眠状态

- Papara Excel İşlem Özeti-crx插件

- python程序设计(基于网络爬虫的电影评论爬取和分析系统)

- OlaMundo:Primeiro存储库

- 零售业管理:价格策略

- 投资组合

- java笔试题算法-Complete-Striped-Smith-Waterman-Library:Complete-Striped-Smit

- ros_arm_control.7z

- tripitaka:Tripitaka的依赖性很低,没有针对Node.js的简洁记录器

- 以品类管理为导向的连锁企业管理功能重组

- 长颈鹿

- 三菱Q系列PLC选型工具软件.zip