Quartus II 6.0:Altera的FPGA/CPLD调试软件

需积分: 50 181 浏览量

更新于2024-07-29

收藏 2.63MB PDF 举报

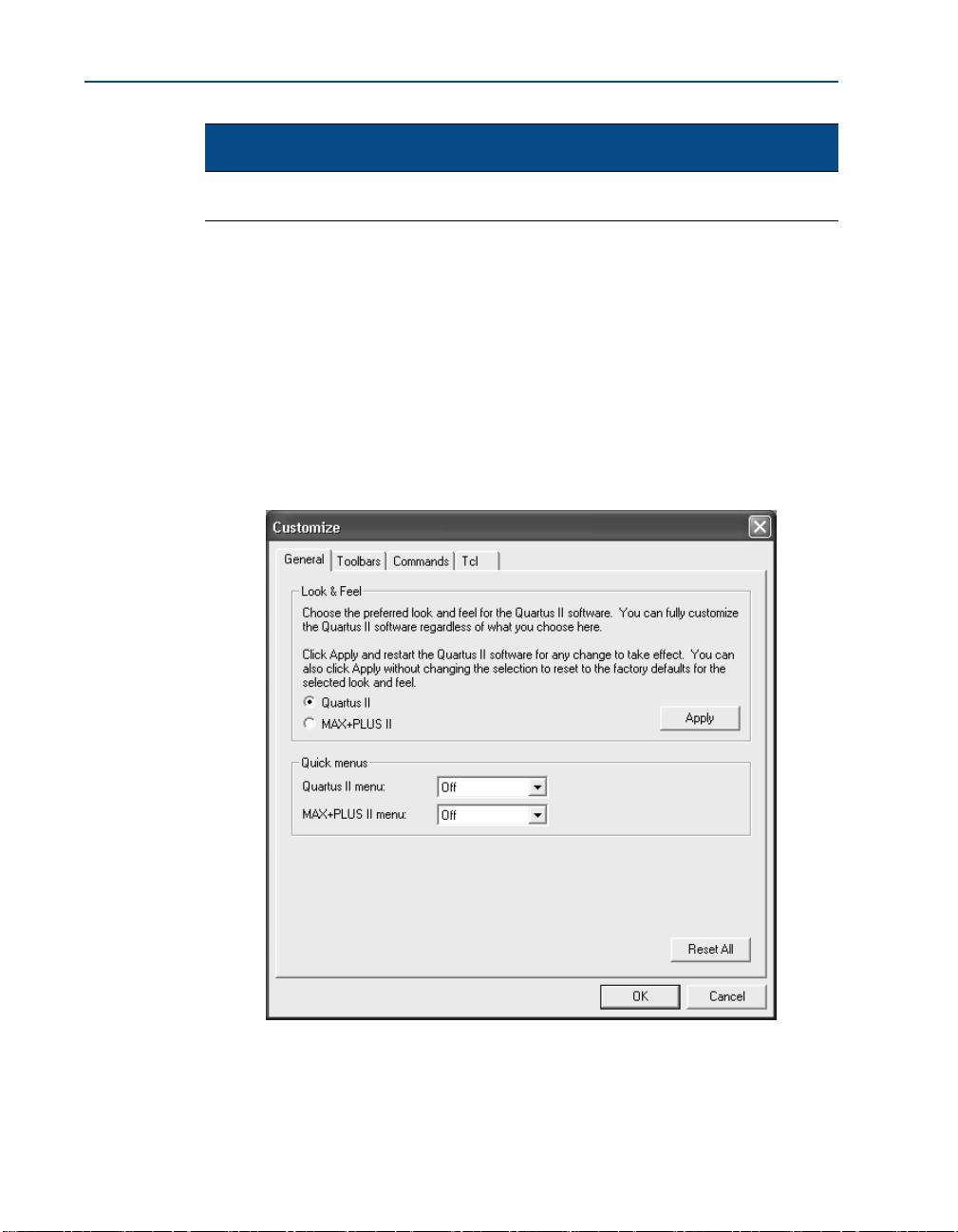

"Quartus II 是Altera公司推出的一款强大的硬件描述语言(HDL)编译器和调试软件,主要用于开发和调试CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)项目。Quartus II 提供了一整套设计、仿真、综合、布局布线和编程工具,适用于各种Altera的半导体产品,如MAX、Cyclone和Stratix系列。这款软件支持多种HDL语言,包括VHDL和Verilog,使得设计者能够方便地实现数字电路的设计和优化。"

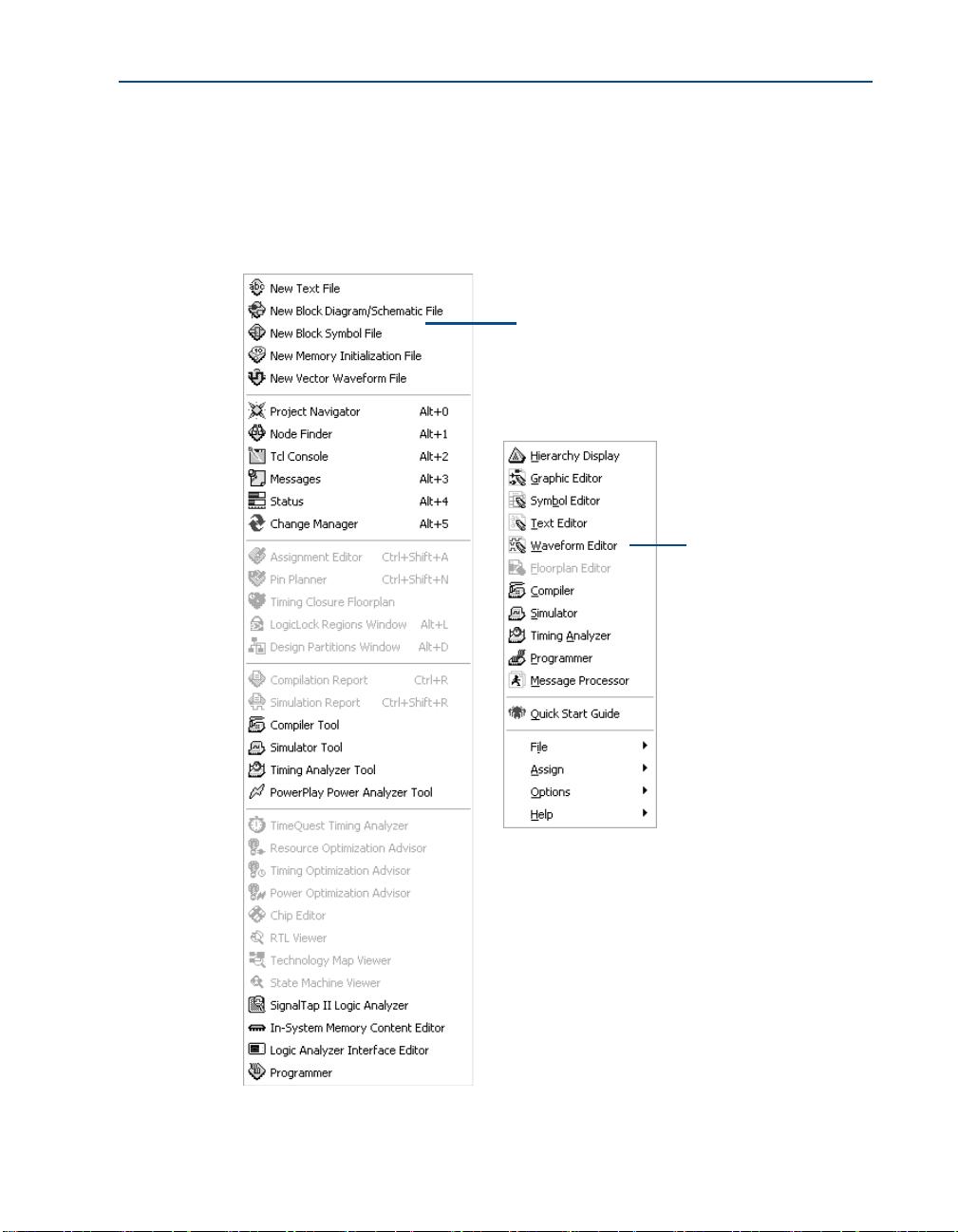

Quartus II 的主要功能包括:

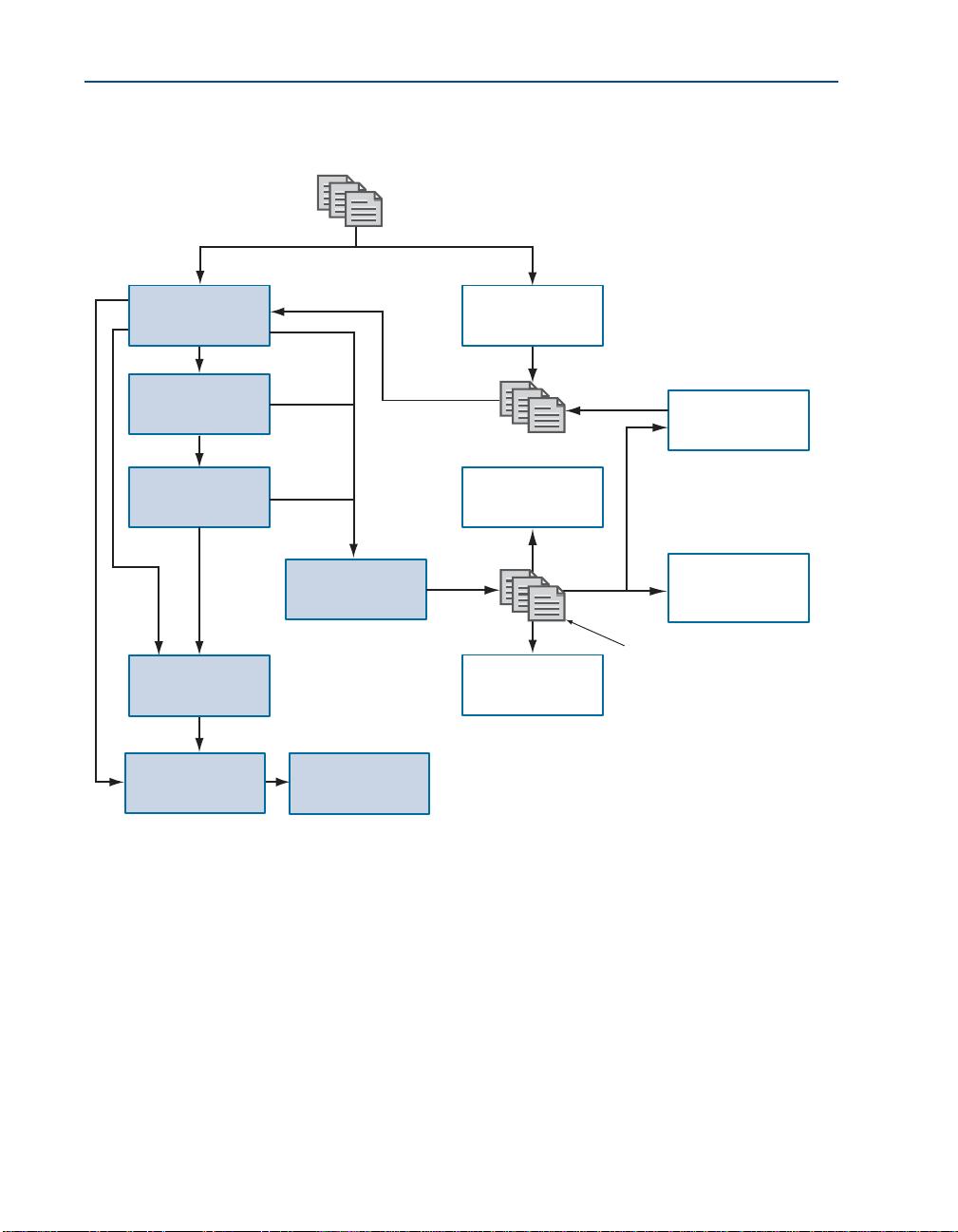

1. **设计输入**:用户可以通过VHDL或Verilog等HDL语言编写设计代码,或者利用Altera的MegaCore库中的预定义IP模块,快速构建复杂的系统。

2. **综合**:Quartus II 能够将HDL代码转化为门级网表,这个过程称为综合,它考虑了设计的逻辑优化和时序约束。

3. **仿真**:集成的ModelSim仿真器允许用户在硬件实施前验证设计的功能,确保设计在实际环境中能够正确工作。

4. **物理布局与布线**:在综合之后,Quartus II 将自动完成逻辑元件的物理布局和信号路径的布线,以优化性能和面积。

5. **时序分析**:软件提供详尽的时序报告,帮助设计者了解设计的延迟和满足时钟速度要求的能力。

6. **编程与配置**:支持各种编程设备,如JTAG接口的ByteBlaster,用于将设计烧录到目标FPGA或CPLD中。

7. **IP核管理**:IP MegaStore提供了丰富的第三方IP核,方便用户在设计中集成标准接口或特定功能模块。

8. **调试工具**:SignalTap内建逻辑分析器允许用户在运行时进行在线调试,无需额外硬件。

9. **版本更新**:6.0版的发布日期为2006年3月,随着Altera不断推出新版本,Quartus II 不断增强其功能和性能,以适应新的硬件技术和设计需求。

需要注意的是,Altera在法律声明中强调了对知识产权的尊重,表明他们不对因使用其产品导致的任何第三方专利或版权侵权承担责任。此外,他们保留对产品规格进行变更而不预先通知的权利,因此设计者应定期检查最新的器件规范以获取最准确的信息。

Quartus II 是一个综合性的设计环境,为电子工程师提供了一站式的FPGA和CPLD开发平台,简化了从概念到实现的整个流程,提升了设计效率和质量。

6552 浏览量

578 浏览量

4744 浏览量

151 浏览量

562 浏览量

135 浏览量

256 浏览量

311 浏览量

182 浏览量

bermingu

- 粉丝: 0

最新资源

- 解决TC2.0笔试题BUG与微软面试迷语解析

- 十分钟快速入门ModelSimSE:Verilog测试与分频示例

- 46家著名IT公司笔试题目集锦

- MATLAB实现数字信号处理基础教程与示例

- 优化无线网络的自适应TCP/IP头部压缩算法

- 两跳簇结构在多媒体传感器网络中的图像传输优化

- IOI冬令营动态规划详解:历年竞赛高频题解析

- 无线传感器网络QoS路由算法挑战与资源优化研究

- 多媒体传感器网络技术探析与研究趋势

- Allegro转Gerber详细步骤与注意事项

- 商场销售数据分析:关联规则挖掘的应用与价值

- 基于Internet的企业进销存管理系统设计与应用

- 掌握指针基础:类型、指向类型与地址理解

- JavaScript全攻略:从基础到高级应用

- 软件测试资格认证:高级检验员试题解析与重点

- C++编程高质量指南:结构、命名与内存管理