Verilog HDL华为内部入门教程

需积分: 44 100 浏览量

更新于2024-07-28

收藏 281KB PDF 举报

"这是一份华为内部使用的Verilog HDL入门教程,主要涵盖了Verilog HDL的基本语法、建模方式以及相关操作。教程分为多个章节,详细讲解了Verilog HDL的各种概念和用法,包括数据类型、运算符、建模方式等。"

Verilog HDL是一种广泛用于数字系统设计的硬件描述语言,特别是在FPGA(现场可编程门阵列)设计中。本入门教程由华为提供,适合初学者学习Verilog HDL的基础知识。

1. **Verilog HDL基本语法**

- **标识符** (4.1节):用于定义变量、模块等的名称,遵循特定的书写规范。

- **关键词** (4.1.2节):语言中预定义的特殊词汇,如`module`, `input`, `output`等。

- **注释** (4.2节):用于解释代码的文本,不参与程序执行。

- **数据类型** (4.5节):包括线网类型和寄存器类型,分别代表硬件连接和存储元素。

- **常量与值集合** (4.4节):定义不可变的数值或一组值。

- **运算符与表达式** (4.6节):涵盖算术、逻辑、关系和条件运算符,用于构建复杂的逻辑表达式。

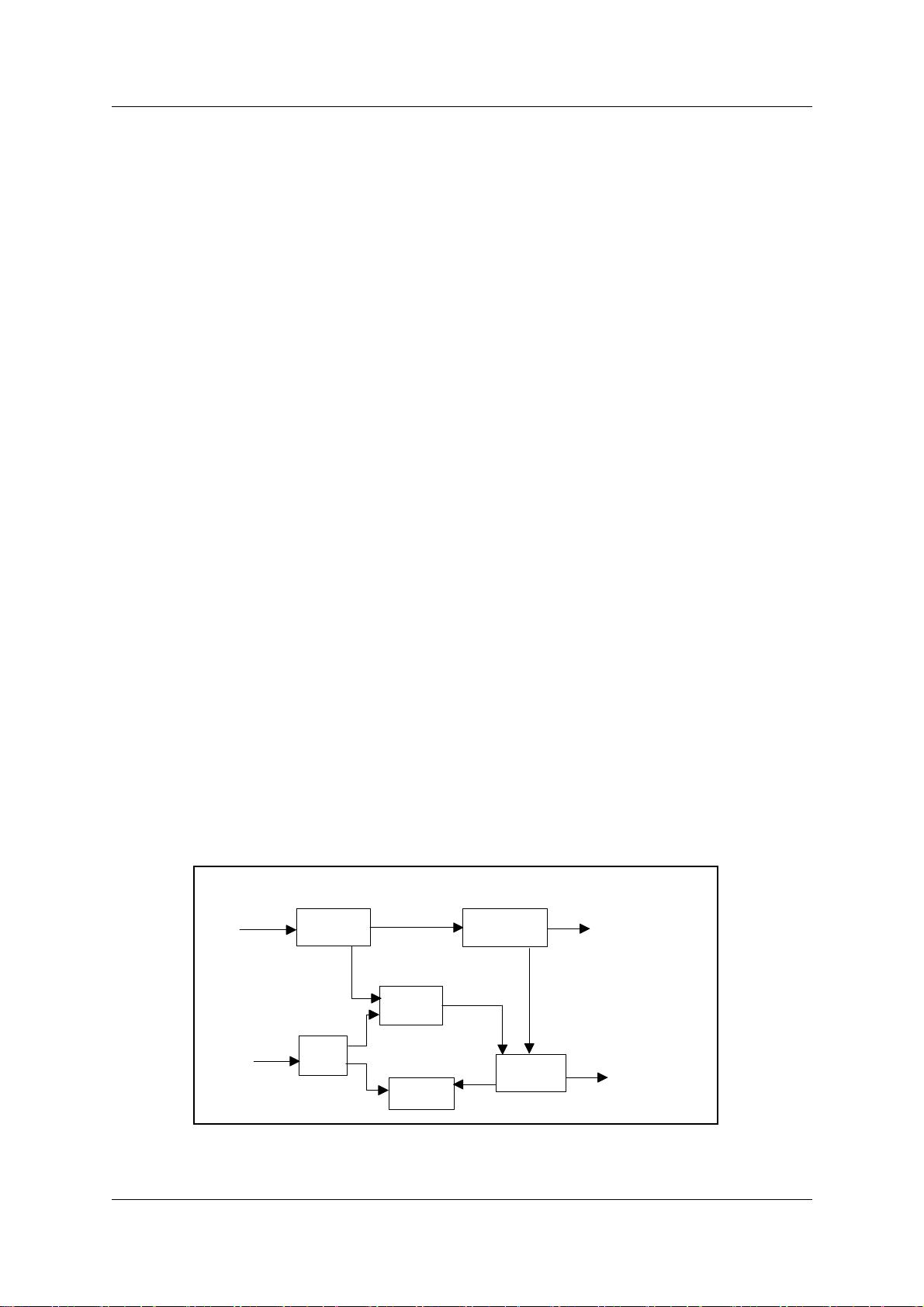

- **结构建模** (5章):描述硬件结构,包括并行和串行的组件连接。

2. **Verilog HDL建模概述**

- **模块** (3.1节):基本设计单元,包含输入、输出和内部逻辑。

- **时延** (3.2节):描述信号传输的时间延迟。

- **三种建模方式** (3.3节):

- 结构化描述(3.3.1节):根据实际硬件元件进行描述。

- 数据流描述(3.3.2节):强调数据处理过程。

- 行为描述(3.3.3节):模拟硬件行为,不直接对应硬件结构。

3. **行为建模**

- **顺序语句块** (7.2节):如`always`块,用于描述时间顺序的行为。

- **过程赋值语句** (7.3节):如`assign`,在特定条件下更新信号值。

- **行为建模具体实例** (7.4节):展示如何用Verilog实现特定功能的行为模型。

4. **数据流建模**

- **数据流建模具体实例** (6.3节):展示如何描述数据通过硬件结构流动的过程。

5. **其他方面**

- **附录A** (10章):列出Verilog HDL的所有保留字,是编写代码时需要避免使用的词汇。

- **习题** (9章):帮助巩固学习内容,提升实践能力。

这份教程详细介绍了Verilog HDL的基础知识,包括语法、建模方法和示例,是学习者掌握该语言的重要参考资料。学习者应通过这个教程,逐步理解Verilog HDL如何用于描述和实现数字系统的逻辑,并通过练习提高设计能力。

1670 浏览量

195 浏览量

141 浏览量

2012-10-20 上传

101 浏览量

154 浏览量

162 浏览量

2010-03-29 上传

点击了解资源详情

tank3508

- 粉丝: 8

最新资源

- 五子牛股票走势查询V1.60:六个月涨跌一目了然

- Python实现的联赛排名信息汇总工具

- 使用C#开发的类似资源管理器的应用程序

- Python开发的文件提取工具:简化更新流程

- PeerTube实时聊天插件:启用网络视频交流

- Kettle数据库迁移全流程实现指南

- discuzX3.0高仿得意门户模板php版v1.0安装教程

- 64位Java开发神器:eclipse-inst-win64.zip轻松获取

- OXYGEN V5.1 专注外贸时装独立站商城模板

- 构建待办事项应用程序的关键技巧

- ArcGIS 9.3详细安装操作指南

- MategoPlayer:强大的GPS轨迹播放软件

- 轻松整合支付宝接口至PHP在线订单系统

- iOS平台实现图片模糊效果的处理方法

- Nuxt与WordPress结合的JAM Stack模板使用指南

- REY V2.1.1.1 科技简约风外贸服饰商城WordPress主题