HYNIX HYSXS02647 SDRAM芯片详细规格介绍

需积分: 48 145 浏览量

更新于2024-09-08

收藏 116KB PDF 举报

"这份文档是HYNIX公司关于HYSXS02647 SDRAM芯片的详细资料,包括产品概述、修订历史以及关键参数的变更。"

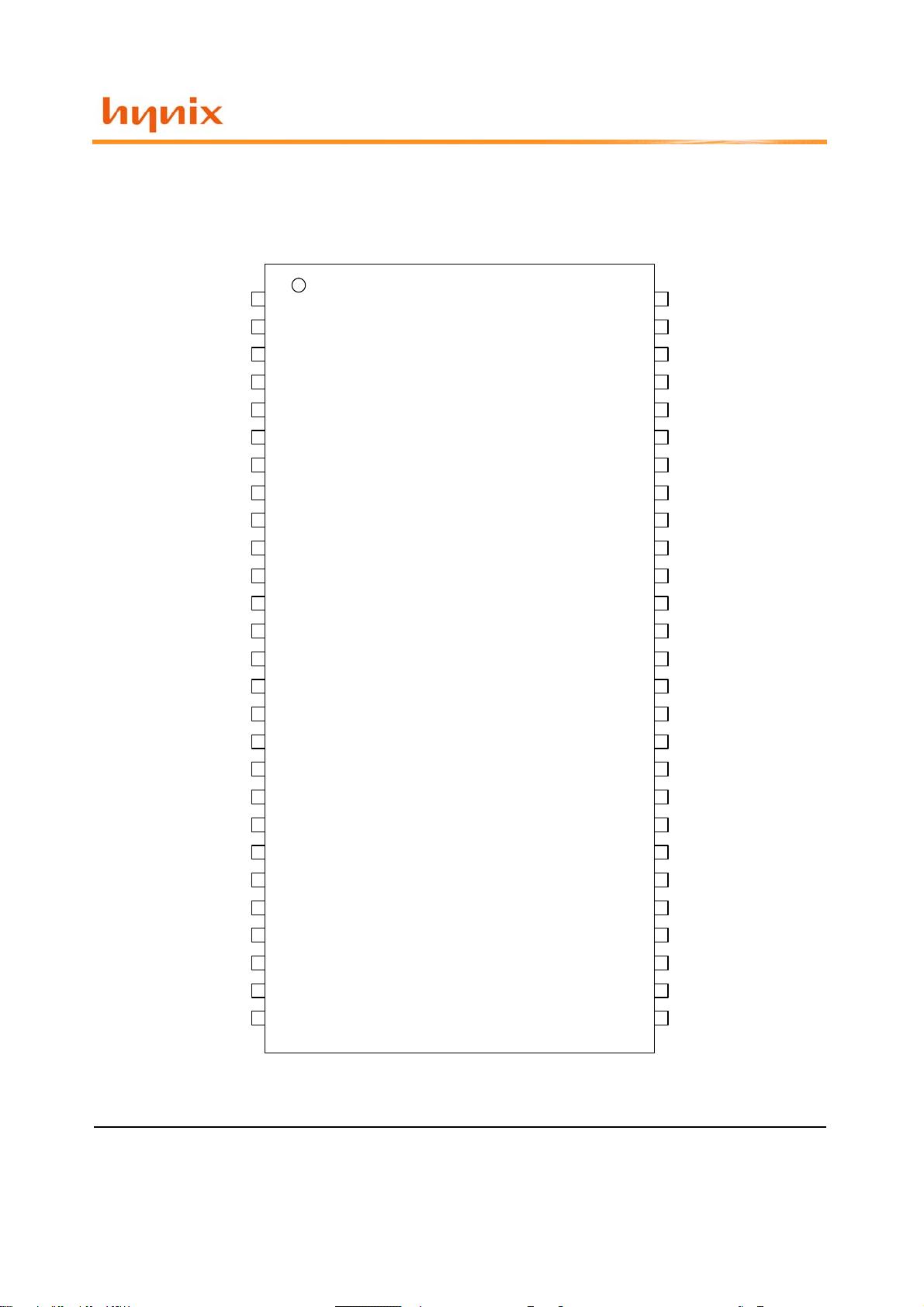

在电子设计领域,SDRAM(Synchronous Dynamic Random-Access Memory)是一种同步动态随机存取存储器,它与系统时钟同步工作,提高了数据传输速度。HYNIX公司的HYSXS02647是一款64Mb的同步DRAM芯片,基于1Mx4 Bankx16 I/O架构,即每个芯片有4个内存银行,每个银行的大小为1Mx16位,总共提供64Mb(8MB)的存储容量。

文档的修订历史显示了产品规格的不断更新和优化:

- 在Rev.1.0中,首次发布了该版本,时钟周期(tCK)的最小值从2.0ns变为2.5ns,对应7ns至7.5ns(CL3)的产品。

- Rev.1.1中,修改了输入高/低电压参数,直流特性中的IDD2NS电流从18mA降至15mA,IDD5电流也有所调整,针对不同速度(200/166/143/133MHz)进行了优化。同时,还调整了时钟高/低脉冲宽度时间、激活时间(tACT)和行到行的读取延迟时间(tRRD)。

- Rev.1.2对修订号进行了修正,并删除了修订历史中的备注,同时更新了交流操作条件,将CL从50pF更改为30pF,直流操作条件中VIH的最大值从VDDQ+2.0变为VDDQ+0.3,VIL的最小值从VSSQ-2.0变为-0.3。

- Rev.1.3在订购信息中对超低功耗做了修正。

- Rev.1.4纠正了引脚分配中的错误,将A12引脚标记为非连接(NC)。

- 最后的Rev.1.5版本主要是对之前的修订进行了一些修正。

这些变更体现了HYNIX公司在产品开发过程中对性能和兼容性的持续改进,以满足不同应用场景的需求。对于使用FPGA(Field-Programmable Gate Array)的工程师来说,了解这些参数和变更至关重要,因为FPGA常需要与SDRAM芯片进行接口设计,以实现高速的数据存储和处理。理解这些规格可以帮助设计者优化系统性能,确保电路的稳定性和可靠性。

2012-09-10 上传

2010-09-28 上传

2021-10-20 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

伟大的鱼香

- 粉丝: 0

- 资源: 2