ARM920T详解:16K Cache原理与全相联设计优化

ARM920T的Cache是针对ARM920T处理器设计的一种高速缓存系统,用于提升处理器对内存数据的访问速度。本文档提供了一篇深入介绍ARM920T Cache工作原理的文章,特别关注于数据Cache部分。ARM920T集成了16K的数据Cache和16K的指令Cache,它们虽然大小相同,但数据Cache增加了写回内存的机制。

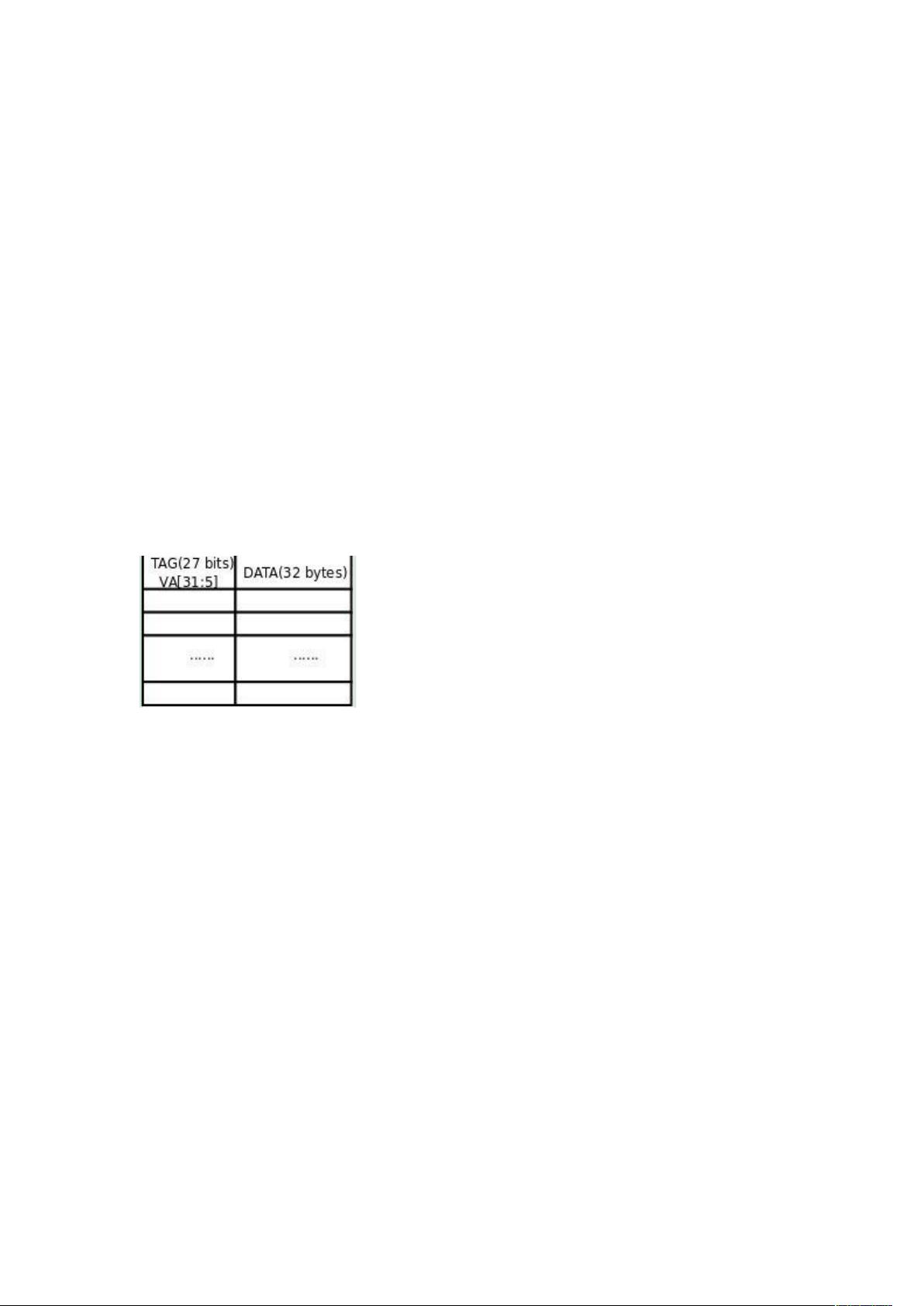

Cache的工作原理基于数据块(CacheLine)的概念,每个CacheLine大小为32字节,而16K的Cache由512条这样的CacheLine组成。为了定位特定数据,Cache利用虚拟地址(VA)的Tag来标记数据来源,即VATag[4],这部分包含了VA的低四位和末尾五位,以确保地址对齐。这种设计被称为全相联Cache,因为任何VA的32字节数据片段都可以映射到任意一条CacheLine上。

查找过程涉及将VA的Tag与Cache中的所有Tag进行比较,当找到匹配的CacheLine时,再通过VA的其他部分(如偏移地址)确定要访问的具体字节。然而,全相联Cache的查找时间复杂度较高,因为可能需要遍历整个Cache(512次)。为减少查找时间,文章提到了一种优化方式,即限制某个VA固定映射到某一条CacheLine,这称为直接映射或组相联Cache,这样查找速度会显著提高,因为只需检查一次就能确定命中与否。

此外,Cache还包括了CacheMiss和CacheHit的概念。当目标数据不在Cache中时,会发生CacheMiss,此时处理器会从主内存中读取数据,并将其加载到Cache中,随后进行处理。CacheHit则表示所需数据已存在于Cache中,可以迅速获取,从而减少了内存访问延迟。

ARM920T的Cache设计是现代处理器架构中提高性能的关键组件,通过优化查找策略和缓存分配,有效降低了内存访问的延迟,提升了系统的整体性能。理解这些细节对于深入研究和优化ARM处理器的性能至关重要。

2009-01-13 上传

318 浏览量

2023-09-01 上传

2023-06-08 上传

2023-02-20 上传

2023-12-28 上传

2023-06-09 上传

2023-05-17 上传

2023-06-09 上传

xiaohengtonxue

- 粉丝: 0

- 资源: 2

最新资源

- C++标准程序库:权威指南

- Java解惑:奇数判断误区与改进方法

- C++编程必读:20种设计模式详解与实战

- LM3S8962微控制器数据手册

- 51单片机C语言实战教程:从入门到精通

- Spring3.0权威指南:JavaEE6实战

- Win32多线程程序设计详解

- Lucene2.9.1开发全攻略:从环境配置到索引创建

- 内存虚拟硬盘技术:提升电脑速度的秘密武器

- Java操作数据库:保存与显示图片到数据库及页面

- ISO14001:2004环境管理体系要求详解

- ShopExV4.8二次开发详解

- 企业形象与产品推广一站式网站建设技术方案揭秘

- Shopex二次开发:触发器与控制器重定向技术详解

- FPGA开发实战指南:创新设计与进阶技巧

- ShopExV4.8二次开发入门:解决升级问题与功能扩展