DesignCompiler综合教程:从原理到实践

需积分: 18 151 浏览量

更新于2024-07-15

收藏 2.21MB PDF 举报

"该文档是关于Design Compiler的详细介绍,适合新手入门,涵盖了综合的基本概念、原理以及使用Design Compiler进行电路综合的全过程。"

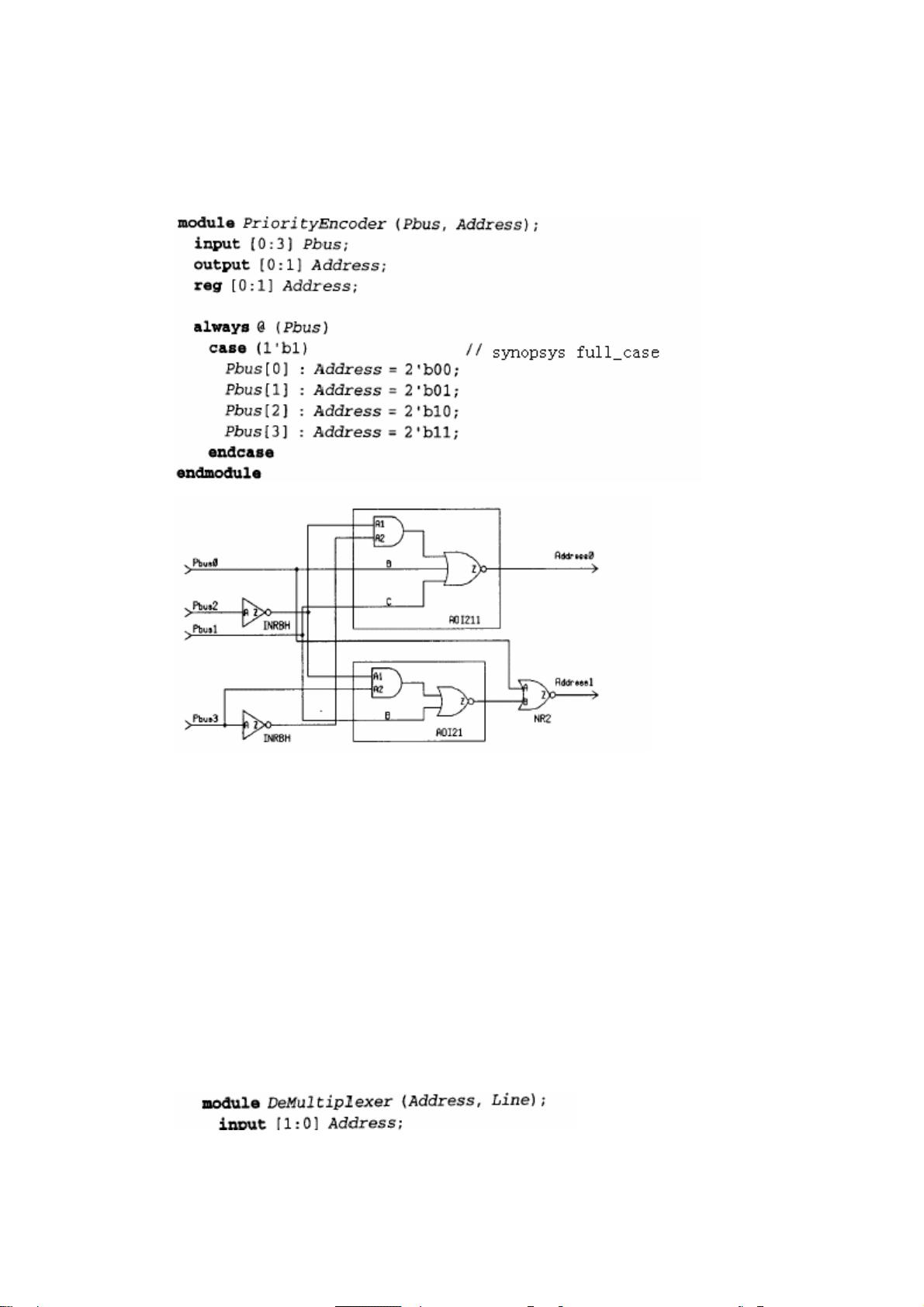

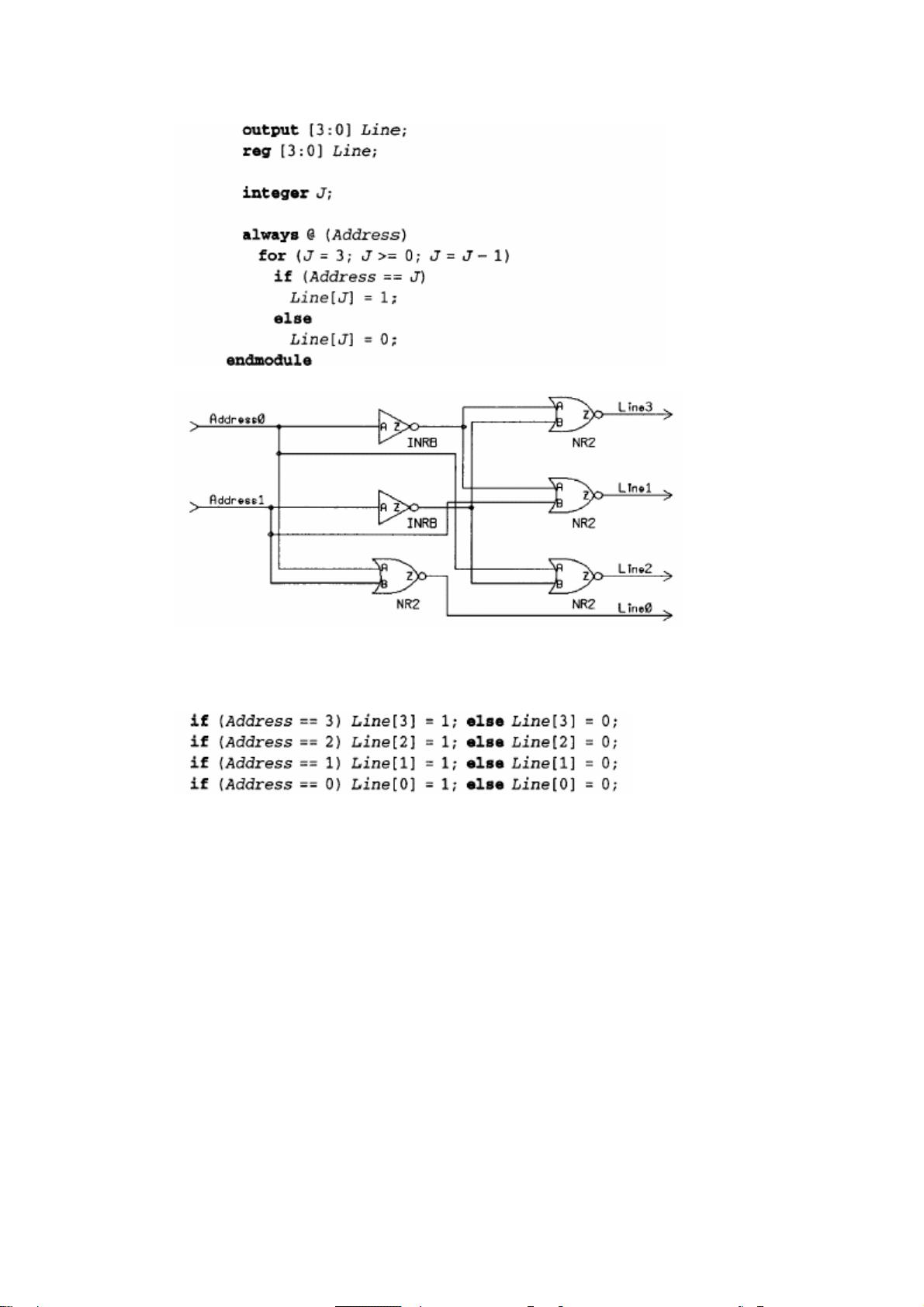

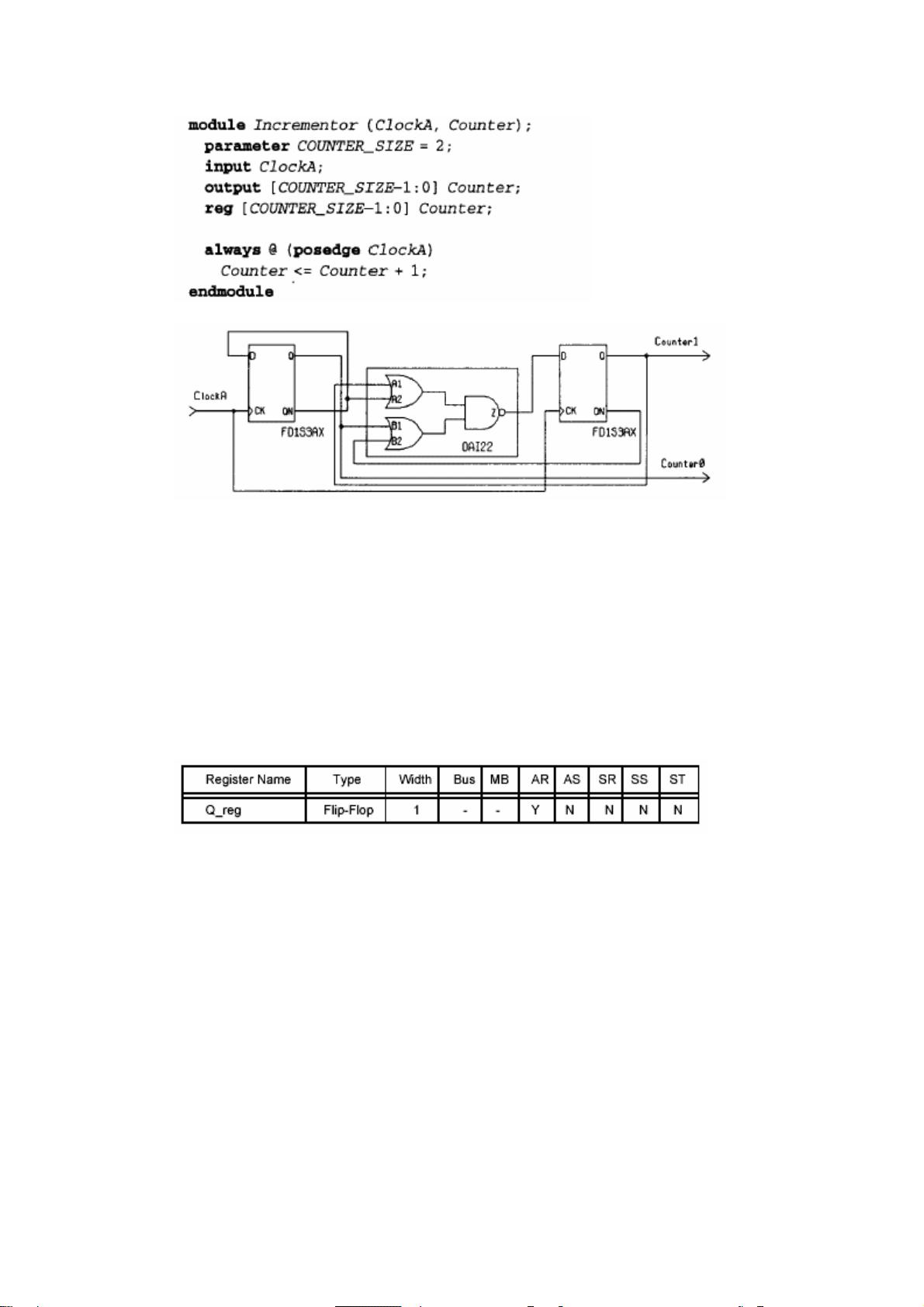

在集成电路设计领域,Design Compiler是一款由Synopsys公司提供的核心综合工具,它能够将高级的硬件描述语言(HDL,如Verilog或VHDL)编写的电路设计转换成基于特定工艺库的门级网表。这个过程被称为综合,是芯片设计流程中的关键步骤。

1. 综合概述

综合是将行为级别的电路设计转换为物理实现的过程,通过软件自动化完成。它涉及到将设计的功能、性能要求与已知的逻辑单元库结合,找出最佳的电路实现方式。这个过程中,综合工具会经历转换、映射和优化三个阶段,最终生成满足延迟、面积等约束条件的门级网表。

2. 综合的不同层次

设计者可以使用HDL在不同的抽象层次进行设计,包括逻辑级、RTL级和行为级。随着抽象层次的提升,设计者对最终硬件的直接控制减少,但设计的抽象程度提高,便于处理更复杂的问题。

- **逻辑级综合**:在这个层次,设计以布尔逻辑表达,触发器等基本单元明确表示。逻辑级描述通常包含对最终电路结构的直接暗示。

- **RTL级综合**:在RTL级,设计侧重于描述电路的行为和操作,而不是具体的布尔逻辑。通过HDL的运算符和行为描述,RTL级综合允许更灵活的设计表达,同时也提供了更多的优化机会。

- **行为级综合**:在最高抽象层次,设计者关注的是算法和系统功能,而不涉及具体的逻辑实现细节。行为级综合将这些描述转换为较低层次的逻辑表示。

3. Design Compiler的使用

Design Compiler作为综合工具,能有效地执行上述各阶段任务。首先,它将HDL代码转换为与工艺无关的RTL级网表,然后映射到特定工艺库的门级表示。最后,通过优化步骤,比如逻辑等效替换、门级并行化等技术,以优化电路的性能和面积。

在实际使用中,设计者会根据设计需求设置约束,如最大延迟、最小面积等,Design Compiler会据此调整其综合策略。通过这种方式,Design Compiler帮助设计师快速地将高层次的设计概念转化为可制造的电路布局。

Design Compiler是芯片设计中不可或缺的工具,它的综合流程确保了从高级设计到实际物理实现的平滑过渡,并通过优化实现性能与面积的平衡。这份文档对于想要了解和掌握Design Compiler的新手来说,是一份非常宝贵的资源。

309 浏览量

2922 浏览量

1258 浏览量

203 浏览量

320 浏览量

2025-03-14 上传

519 浏览量

223 浏览量

2024-12-12 上传

2025-03-09 上传

Wingsmengmengge

- 粉丝: 0

最新资源

- Android应用-Goldcard-Helper使用教程

- 探索iOS静态库中集成XIB文件的实现方法

- 51单片机实现1602液晶显示秒表的设计与实现

- LPC1768 EasyWEB网络开发与测试指南

- WebGIS地图开发实用代码示例与压缩技术

- ColorCols:挑战色彩匹配的开源平台游戏

- C++实现公司工资管理系统:增删改查与链表文件存储

- Android应用崩溃模拟工具Krasha介绍

- UDF编程心得:经验总结与推荐

- Craters.js:轻量级HTML5游戏引擎的构建与特性介绍

- 基于信息技术的学生考勤签到系统设计

- Golden Software Surfer 11.0.642汉化教程与win7兼容性

- 深入剖析Android热修复技术原理及应用

- 王晓东编著《数据结构与STL框架》PPT解析

- 51单片机实现可调占空比PWM方波输出教程

- C语言高精度加法算法实现与应用