Verilog实现32位多周期CPU设计详解与关键模块

需积分: 0 83 浏览量

更新于2024-08-04

收藏 158KB DOCX 举报

本Verilog多周期CPU设计文档详细介绍了如何用Verilog语言开发一款32位的复杂处理器。该CPU采用多周期架构,旨在提高执行效率并支持多种指令集操作,包括算术运算(如ADD、SUB、MULT等)、逻辑操作(AND、OR、XOR等)、移位和比较指令等。值得注意的是,设计中对某些特定指令(如ADDU、SUBU、ADDI等)处理时并不检查溢出,可能是出于教学目的或者特定应用场景的需求。

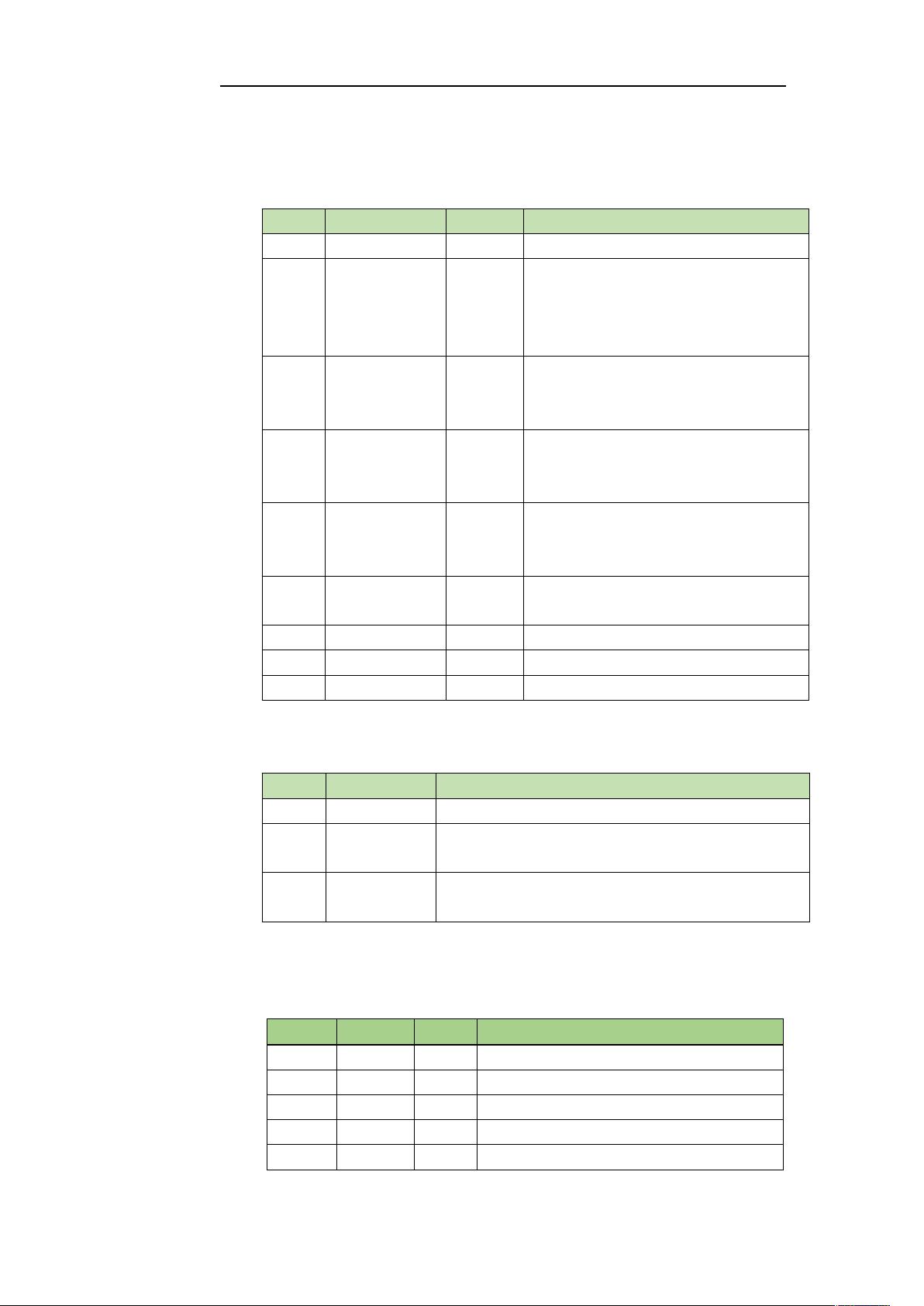

文档的核心部分包括了关键模块的设计与实现,例如程序计数器(PC)负责指令的地址管理,指令解码器(IM、IFID、NPC)负责解析和预取指令,通用寄存器文件(GRF)存储数据,比较单元(CMP)进行算术和逻辑比较,扩展单元(EXT)处理外部操作,以及数据转发和控制单元(Controller)协调各个模块的工作。

每个模块都有详细的端口说明和功能定义,比如PC接收和输出指令地址,IM根据指令类型选择执行路径,ALU执行算术和逻辑运算,而EXMEM可能与内存单元交互。此外,设计者还考虑了数据冲突的处理策略,即在数据写入寄存器时,如果发现数据源处于高阻态,就暂停操作,确保数据的一致性。

测试方案部分,设计者提供了一个简单的测试代码示例,展示了如何使用addi指令,并涉及到内存写入和数据传递。通过编写和执行这样的测试,可以验证CPU核心各组件的功能是否正常。

整个设计文档不仅涉及硬件实现,还包含了设计思路、模块间交互和错误处理机制,为读者提供了从概念到实践的完整设计流程,适合学习和研究Verilog在CPU设计中的应用。

110 浏览量

851 浏览量

201 浏览量

728 浏览量

1936 浏览量

428 浏览量

540 浏览量

1097 浏览量

119 浏览量

梁肖松

- 粉丝: 32

- 资源: 300