FPGA实现的SPI主机模块设计与Verilog仿真

97 浏览量

更新于2024-08-30

1

收藏 292KB PDF 举报

"基于FPGA的串行外围接口SPI设计与实现"

本文主要探讨了如何基于FPGA实现SPI(串行外围接口)总线的设计。SPI总线是一种高效的同步串行接口,具有全双工通信、线路简洁、协议简单以及高速传输的特点。在多种串行总线中,SPI因其高效性和易于实施,常被用于连接主机与各种外围设备,如存储器、传感器或显示设备。

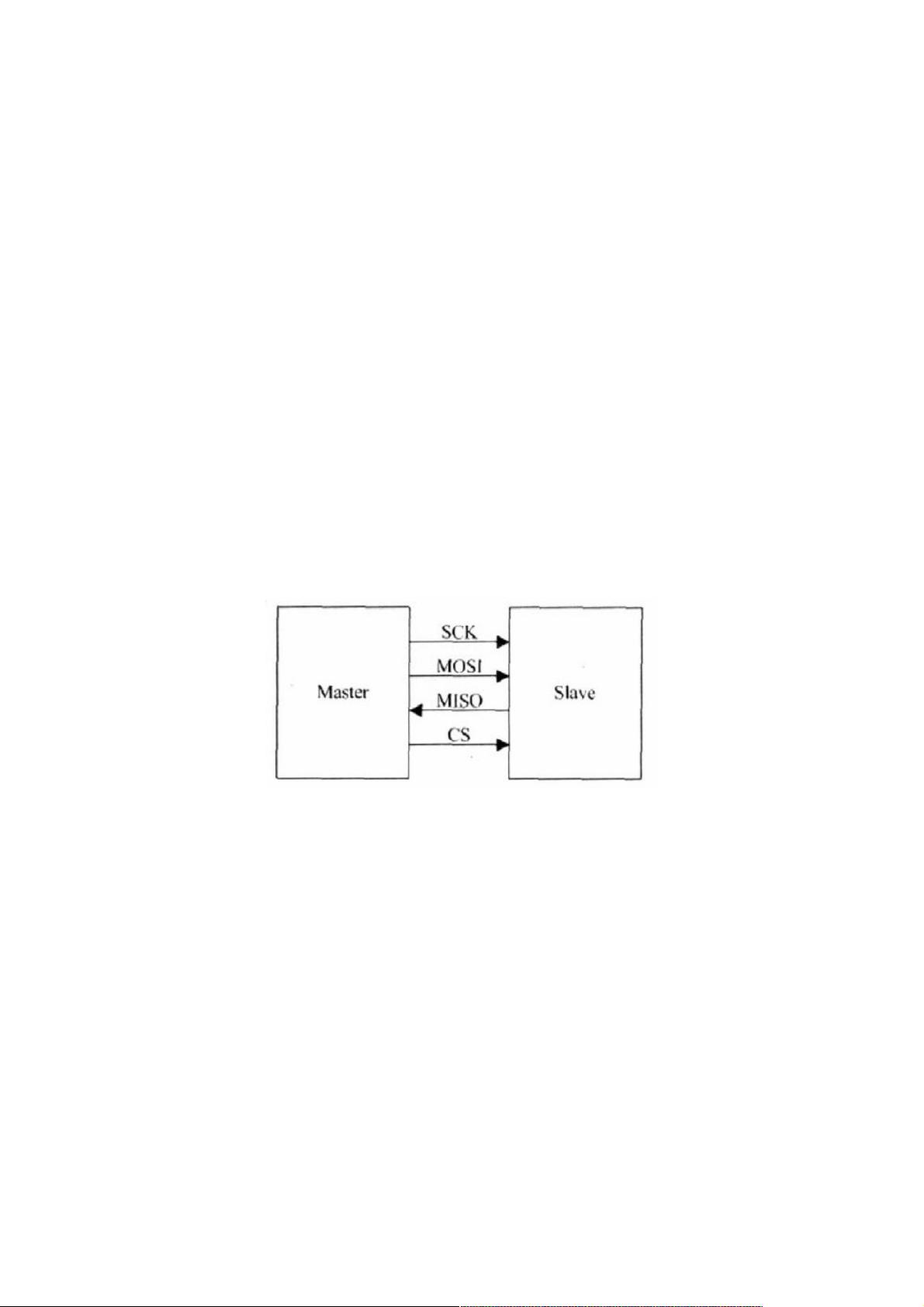

SPI总线的核心特点包括四条主要信号线:主设备输出/从设备输入(MOSI)、主设备输入/从设备输出(MISO)、串行时钟(SCLK)和芯片选择(CS)。这种通信方式支持四种不同的工作模式,分别是模式0、模式1、模式2和模式3,它们的主要区别在于数据在时钟边沿的上升或下降沿被采样,以及数据的输出是在时钟的高电平还是低电平期间。

设计中,作者使用Verilog硬件描述语言编写SPI主机模块。Verilog是一种广泛使用的硬件描述语言,能够用来描述数字系统的结构和行为。经过ModelSim仿真工具的验证,设计的SPI主机模块能够产生预期的波形,表明其功能正确无误。

接下来,该设计在Xilinx ISE集成开发环境中进行综合和实现。Xilinx ISE是Xilinx公司提供的一个用于FPGA设计的工具套件,它包含了从设计输入、逻辑综合、布局布线到编程下载的全套流程。将设计在FPGA上实现并验证,确保了设计的物理可行性。

在FPGA上的实现意味着SPI总线可以灵活地适应不同的应用需求,如通过更改设计参数来扩展数据位数或者调整工作模式。这种灵活性是FPGA相对于ASIC(应用专用集成电路)的一大优势,因为它允许设计者在不重新制造硬件的情况下修改和优化系统。

基于FPGA的SPI设计提供了一种高效且可定制的解决方案,适用于各种嵌入式系统和IoT(物联网)应用。通过理解和实现SPI总线的工作原理,设计者可以构建出适应不同外围设备的接口,以满足特定的系统需求。同时,FPGA的可编程性使得这种设计不仅限于基础功能,还能随着技术的发展进行升级和扩展。

2012-06-22 上传

2021-07-13 上传

2020-10-21 上传

2021-07-13 上传

2021-07-12 上传

2012-01-12 上传

2021-08-15 上传

2020-10-25 上传

2021-07-13 上传

weixin_38628150

- 粉丝: 4

- 资源: 936

最新资源

- forward_algorithm.zip_matlab例程_matlab_

- solrium:Solr的通用R接口

- newunobet:大pp

- project_euler:这是来自https的已解决问题的存储库

- webchem:来自网络的化学信息

- cartified:一个非常基本的购物车实施

- 7Applied-multi-dimensional-fusion-.zip_图形图像处理_PDF_

- risitas-uikit

- homework4-february-20-2021:Web API:代码测验

- astrofox:Astrofox是一种运动图形程序,可让您将音频转换为出色的视频

- SpotipyProject

- tdd-blog:只是学习TDD的一个示例

- ezknitr:使用“ knitr”时避免典型的工作目录痛苦

- webPass-crx插件

- vue+node少儿编程项目.zip

- test-workflow