VHDL实现的数字时钟设计与功能解析

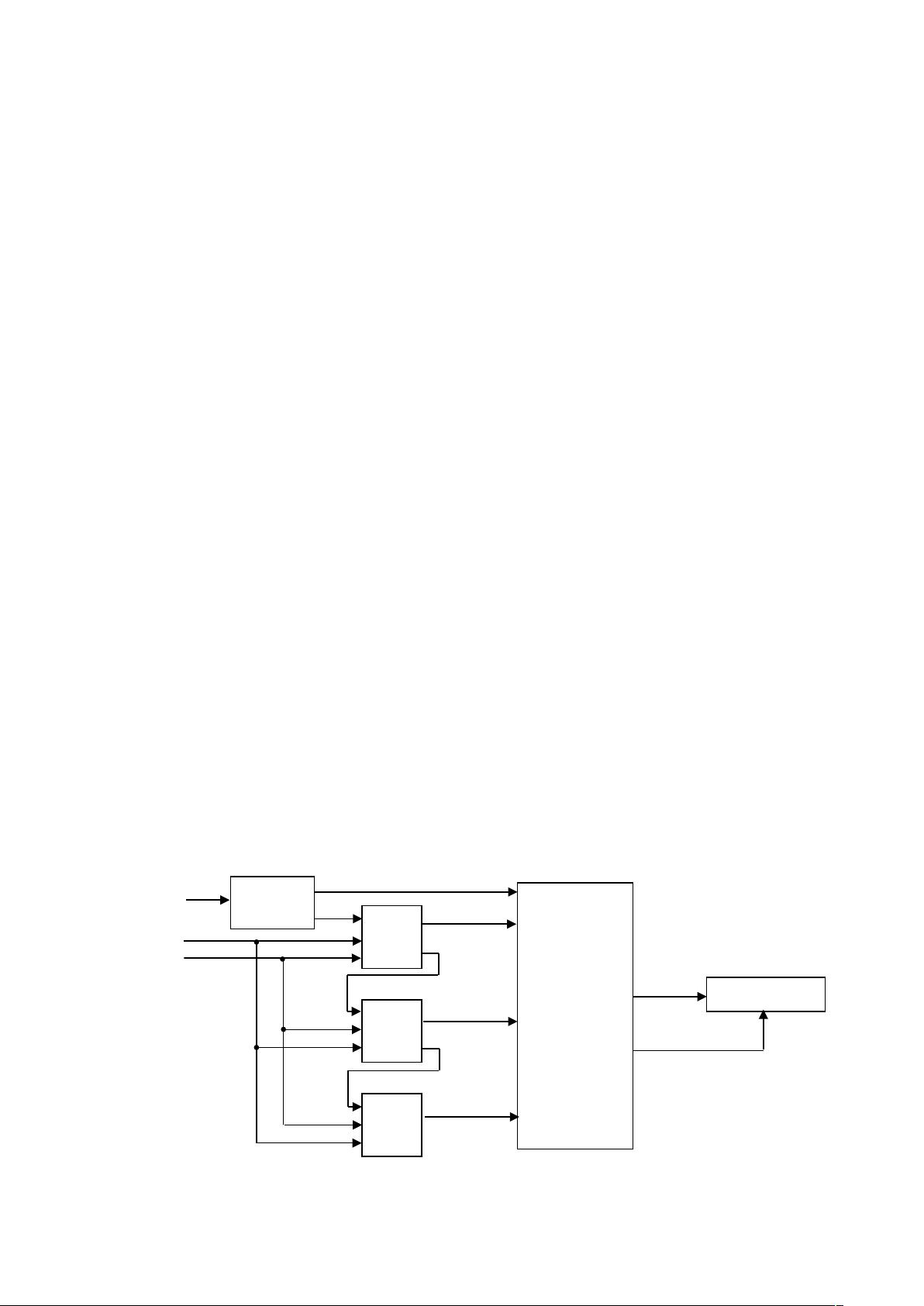

“数字时钟设计VHDL”实验旨在设计一个能够计时并显示00:00:00到23:59:59时间范围的数字时钟,具备暂停和清零功能。实验涉及到的关键技术包括VHDL编程、时钟设计以及EDA工具的使用,如QuartusII7.0。实验内容涵盖了秒脉冲发生、计数、译码显示和时钟调整四个核心部分。

实验原理详解:

1. 秒脉冲发生:时钟的精度主要取决于秒脉冲的准确性。通常,会通过分频电路将较高频率的系统时钟(例如50MHz)分频得到稳定的1Hz秒脉冲。这里采用50000000分频,设计一个计数器,其进位输出即为所需的1Hz信号。

2. 计数部分:计数器分为秒、分和时三个层次,分别是60进制的秒计数器、分计数器,以及24进制的时计数器。每个计数器都有时钟输入(clk)、复位(rst)输入,以及相应的进位和数据输出。为了实现设置时间的功能,还可以添加置数控制引脚(Set)和置数输入引脚(d0~d7)。

3. 译码显示部分:这一模块接收时分秒计数数据,并将其转换成适合数码管显示的格式。它有25个输入引脚,包括时钟信号和计数数据,以及14个输出引脚,包括8位显示码和6位数码管选通信号。译码器按照时钟信号的节奏依次选择并显示十时、时、十分、分、十秒和秒。

4. 时钟调整部分:这部分可能包括暂停和清零功能。暂停功能可以通过控制时钟输入的信号来实现,清零则可以通过复位引脚或特定的置数操作完成。

VHDL代码示例:

在VHDL中,我们可以创建一个实体`clk_1Hz`来实现1Hz时钟分频器。架构`Bhv`中,声明内部计数信号`clk_1Hz_r`和计数器变量`count`。当`sys_clk`上升沿到来时,计数器加1,当`count`达到最大值时,`clk_1Hz_r`翻转,输出1Hz的时钟信号。计数器在达到最大值后重置。

实验过程:

1. 理解数字时钟的工作原理。

2. 编写各部分的VHDL代码,如秒脉冲发生器、计数器和译码器。

3. 使用QuartusII7.0进行仿真和综合,验证设计的正确性。

4. 将设计下载到SOPC实验箱中,观察实际运行效果。

通过这个实验,学生可以深入理解数字时钟的工作机制,掌握VHDL编程技巧,以及如何利用EDA工具实现硬件逻辑设计。同时,也能提高对定时和计数器设计的理解,为更复杂的数字系统设计打下基础。

431 浏览量

369 浏览量

760 浏览量

196 浏览量

514 浏览量

409 浏览量

415 浏览量

279 浏览量

179 浏览量

lsw59

- 粉丝: 7

- 资源: 33

最新资源

- 中国项目管理师培训讲义——费用管理

- SWF:一些用于处理SWF文件的python脚本

- 作品集:专为展示我的所有作品而创建的项目

- neural_network_projects:这是一些基本的神经网络

- STSensNet_Android:“ ST BLE StarNet” Android应用程序源代码-Android application source code

- SLIC-ImageSegmentation:基于SLIC图像分割算法实现一个比PS魔棒工具还方便的抠图工具

- yet-another-istanbul-mocha-no-coverage

- 四卡功能

- android 一个杀进程 程序分享,包含源代码-网络攻防文档类资源

- babel_pug_project:通过babel,pug,node,express进行Web服务器教育.....

- 爱普生7710 7720l免芯片固件刷rom附安装说明

- GenericInstsBenchmark

- AK_Lab2

- MADSourceCodes:“使用Android移动应用程序开发”课程源代码-Android application source code

- themeweaver:使用设计标记在浏览器中创建kick-ass IDE主题!

- oo-way-getonboard中的战舰:GitHub Classroom创建的oo-way-getonboard中的战舰