FPGA设计中的时序挑战与共同时钟系统解析

"FPGA时序系统理论:共同时钟与源同步系统解析"

在FPGA设计中,时序系统理论是至关重要的,特别是在高速数字系统设计中,时序问题直接影响着系统的性能和稳定性。随着技术的进步,时钟频率不断提升,这使得数据传输的有效窗口变得极其短暂,对时序计算和分析的精度提出了更高的要求。时序不仅涉及到数据传输的正确性,还与信号完整性紧密相连。信号质量的好坏会直接影响时序的稳定,任何由于信号反射、串扰导致的信号劣化都可能导致时序偏移或紊乱。

一、普通时序系统(共同时钟系统)

普通时序系统是指所有模块共享同一个系统时钟源。在这种系统中,所有的数据传输和处理都在统一的时钟周期内进行。以下是一个典型共同时钟系统的例子,如处理器与芯片组之间的通信:

[在此插入时序系统示意图]

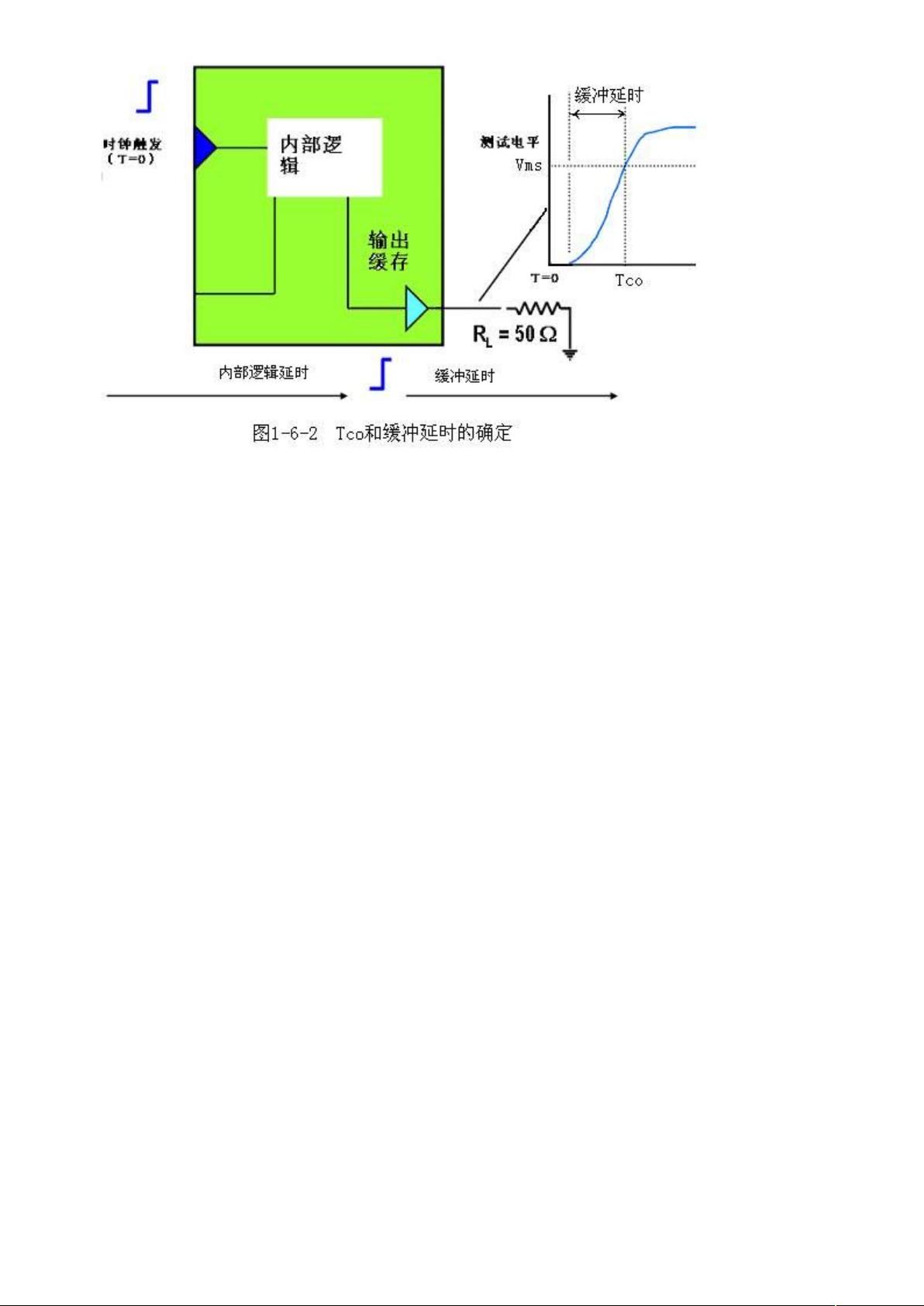

在这个例子中,数据在时钟上升沿被锁存并输出,然后通过传输线传递,在下一个时钟上升沿到达时被接收端读取。为了保证数据的正确传输,必须确保传输延迟(Tflight)小于一个时钟周期,以满足建立时间要求。如果传输延迟过长,可能导致接收端读取到的数据错误,这是由于建立时间不足引起的时序违规。

二、源同步系统时序

源同步系统时序则是数据和时钟信号一起从驱动端发出,旨在减少由于公共时钟传播延迟引起的不确定性。这种设计可以显著减小建立时间和保持时间的约束,因为时钟和数据是同时到达接收端的。源同步系统常用于高速串行接口,如PCI Express和USB等,它们能够支持更高的数据速率,但同时也需要更复杂的信号调理和时序分析。

源同步系统的主要优势在于减少了时钟路径的长度,降低了时钟延迟的不确定性,从而提高了时序的裕量。然而,它也带来了新的挑战,例如需要解决时钟恢复和数据眼图分析等问题,以及需要考虑数据和时钟信号间的相位噪声和抖动。

总结来说,理解和掌握FPGA设计中的时序系统理论,无论是共同时钟还是源同步系统,对于设计出高效、可靠的系统至关重要。时序分析不仅涉及硬件层面的计算,还包括对信号完整性的深入理解,只有这样,才能确保在高频环境下数据的准确无误传输。随着FPGA技术的不断发展,时序设计的复杂性和重要性只会继续增加,因此,对于工程师来说,不断学习和掌握这些理论知识是保持竞争力的必要条件。

2010-06-23 上传

2012-05-22 上传

2010-05-19 上传

2018-01-02 上传

2021-10-03 上传

2021-10-02 上传

2021-05-25 上传

2022-06-26 上传

2018-11-22 上传

yhk2006

- 粉丝: 0

- 资源: 2

最新资源

- CoreOS部署神器:configdrive_creator脚本详解

- 探索CCR-Studio.github.io: JavaScript的前沿实践平台

- RapidMatter:Web企业架构设计即服务应用平台

- 电影数据整合:ETL过程与数据库加载实现

- R语言文本分析工作坊资源库详细介绍

- QML小程序实现风车旋转动画教程

- Magento小部件字段验证扩展功能实现

- Flutter入门项目:my_stock应用程序开发指南

- React项目引导:快速构建、测试与部署

- 利用物联网智能技术提升设备安全

- 软件工程师校招笔试题-编程面试大学完整学习计划

- Node.js跨平台JavaScript运行时环境介绍

- 使用护照js和Google Outh的身份验证器教程

- PHP基础教程:掌握PHP编程语言

- Wheel:Vim/Neovim高效缓冲区管理与导航插件

- 在英特尔NUC5i5RYK上安装并优化Kodi运行环境