ModelSim-Altera 6.5入门教程:从新建工程到仿真实践

需积分: 3 88 浏览量

更新于2024-07-29

1

收藏 1.13MB DOC 举报

本篇教程是关于如何使用ModelSim-Altera 6.5e仿真器进行Verilog/VHDL设计的入门指南,它结合了实际操作步骤与清晰的图片说明,旨在帮助初学者快速上手。教程主要分为两个部分:

**第一部分:设计流程**

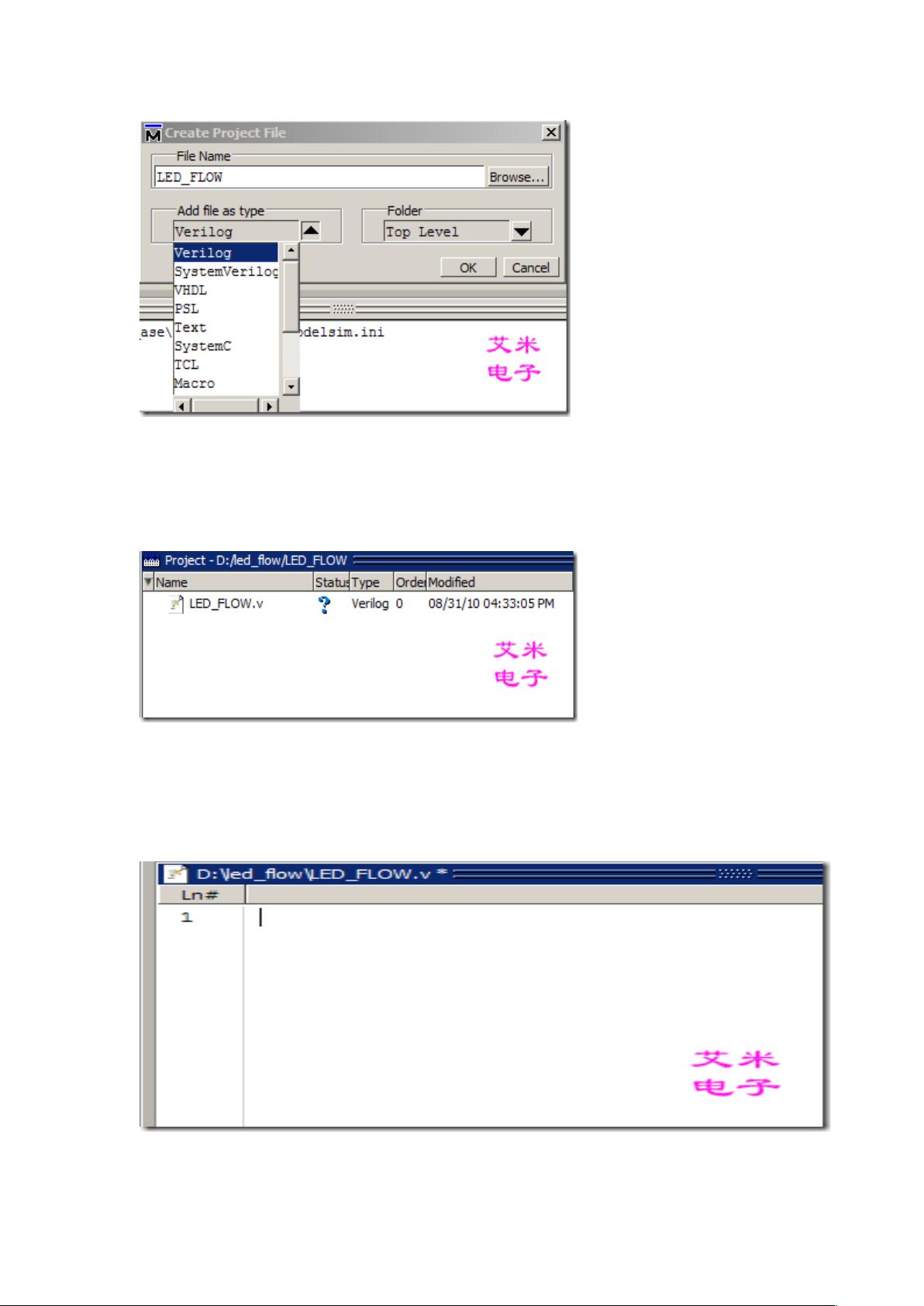

1. **新建工程** - 在ModelSim环境中,首先打开软件,选择“File”菜单中的“New Project”,设置工程名称(如LED_FLOW)、路径(如D:/led_flow)和默认库名(通常设为work)。可以通过ini文件映射库设置,或者直接复制至工程文件夹。

2. **添加新项目** - 在Project标签下,点击“Add Item to the Project”,选择“Create New File”来创建一个新的Verilog文件。用户会被引导输入文件名和类型,例如LED_FLOW.v,并确认文件类型为Verilog。

**第二部分:具体操作**

- **创建源文件** - 用户会看到一个空白的源文件编辑器窗口,用于编写Verilog或VHDL代码。这里需输入LED Flow的设计代码,例如门级电路或模块定义。

- **仿真配置** - 一旦文件创建,可以选择“CreateSimulation”来配置仿真选项,如时序分析、逻辑综合等,以便对电路进行功能和性能验证。

- **文件管理** - 通过“AddExistingFile”或“CreateNewFolder”功能,可以组织和管理工程中的其他文件和子目录,保持代码结构清晰。

整个教程注重实践操作,通过一步步的指导,使读者熟悉ModelSim的基本界面和常用功能,从而掌握在Altera Quartus II 10.0环境下使用ModelSim进行数字逻辑电路设计和仿真的过程。这对于学习和理解数字电子设计至关重要,无论是对初学者还是进阶工程师,都是一份宝贵的参考资料。

160 浏览量

151 浏览量

181 浏览量

160 浏览量

128 浏览量

2011-03-10 上传

125 浏览量

118 浏览量

点击了解资源详情

remote2

- 粉丝: 0

- 资源: 3

最新资源

- OnlineConverter for onliner-crx插件

- jazmimukhtar.github.io

- 初级java笔试题-awesome-stars:我的GitHub星星精选列表

- arduinomega2560_driver.zip

- python-ternary:带有matplotlib的python三元绘图库

- 在家:预测AT家庭组的销售收入

- 实现简单的缓存功能的类库

- 不同销售业务的需用用人才标准

- Royal-Parks-Half-Marathon:该网站将宣布2021年皇家公园半程马拉松

- SoundWave:动态显示声波:rocket:

- Debuger.zip

- nodejs-express-猫鼬书

- XX战略模式研讨报告

- Payfirma-Woocommerce-Plugin:带V2 API的Payfirma Woocommerce插件

- brig:在ipfs上使用git之类的界面和基于Web的UI进行文件同步

- java笔试题算法-aho-corasick:DannyYoo在Java中实现的Aho-Corasick算法,几乎没有改进