USB IP核设计与FPGA验证实践

48 浏览量

更新于2024-09-01

收藏 192KB PDF 举报

"USB IP核设计与FPGA验证"

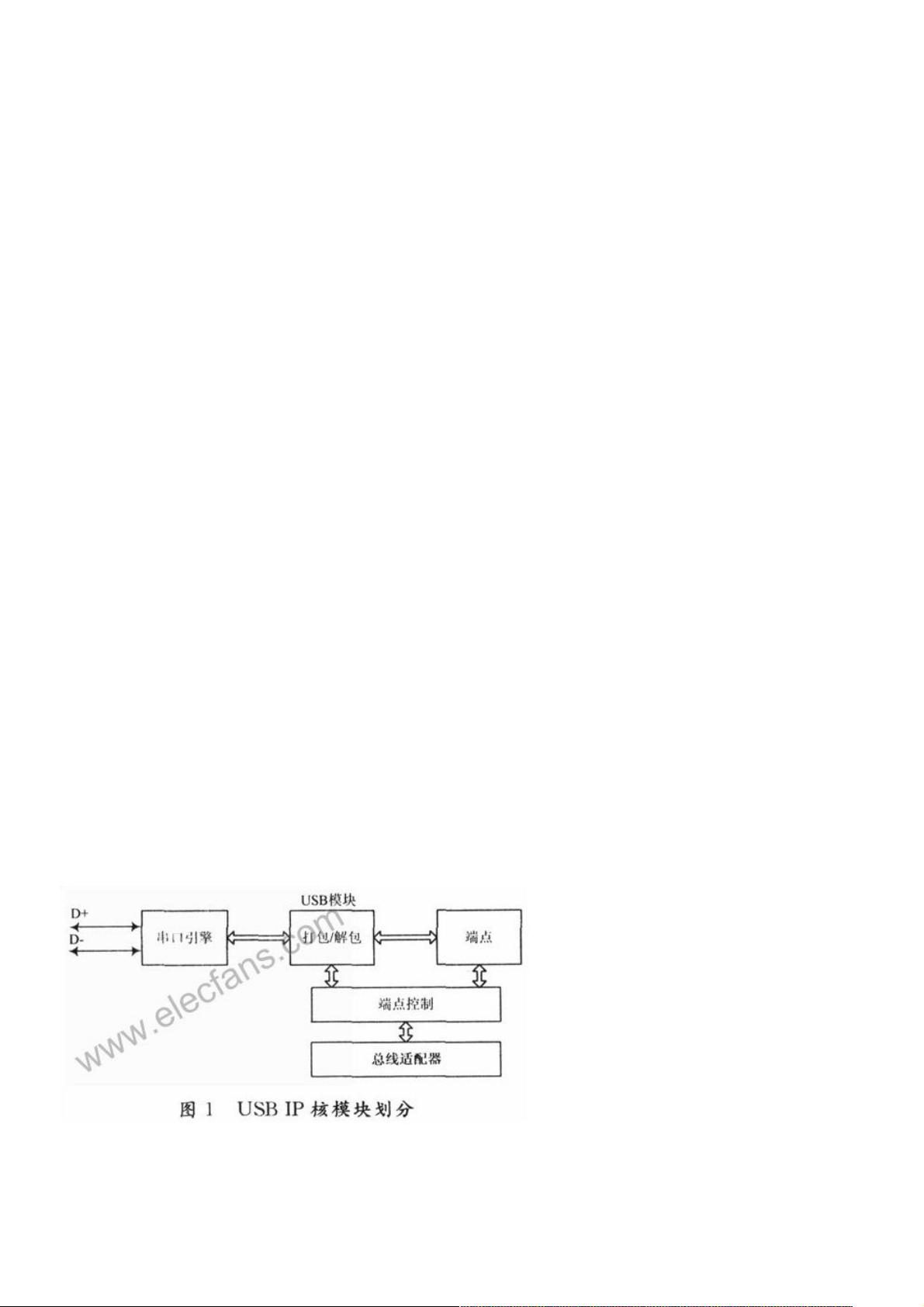

本文主要介绍了如何设计一款可配置的USB IP核,并通过FPGA验证其在SoC系统中的应用。USB IP核因其即插即用、广泛的软硬件支持、低功耗以及多种速度模式等特性,在现代电子设备中得到了广泛应用。随着SoC(System on Chip)技术的发展,IP核的复用成为提高设计效率的关键。

在设计USB IP核时,考虑到了可重用性,特别设计了一个总线适配器模块。这个模块允许IP核灵活地适应不同的片上总线架构,如AMBA ASB (Advanced Microcontroller Bus Architecture - Advanced System Bus) 和WishBone。总线适配器的作用在于处理协议转换,使得IP核的内部逻辑保持不变,仅需调整适配器的配置就能接入不同的SoC总线环境。

AMBA是由ARM公司提出的片上系统总线标准,包含多种协议,ASB是其中之一,用于连接低带宽外设。WishBone则是Silicore公司推出的一种开放源码的SoC互连架构,适用于各种微控制器和数字系统。Avalon总线则是Altera公司的总线规范,常用于FPGA设计。

在本文实现的USB IP核中,总线适配器被设计为一个独立组件,可以在综合前根据目标总线类型(如WishBone或AMBA ASB)进行配置。这种设计方法增强了IP核的灵活性和可移植性,使其能够在不同类型的SoC平台上无缝集成。

FPGA验证是确保IP核功能正确性和性能的关键步骤。通过在FPGA上实现和测试USB IP核,可以验证其在实际操作中的行为,包括数据传输的正确性、速度性能以及与其他系统组件的兼容性。验证结果表明,该USB IP核可以作为一个独立的模块成功地嵌入到SoC系统中,为系统设计者提供了一个可靠的USB接口解决方案。

这篇文章除了介绍USB IP核的基本设计思路和模块划分,还强调了总线适配器的重要性,以及在FPGA验证过程中所验证的功能和性能。对于那些从事SoC设计和嵌入式系统开发的工程师来说,这样的设计方法和验证过程提供了宝贵的经验和参考。

1351 浏览量

135 浏览量

2022-03-03 上传

1136 浏览量

200 浏览量

136 浏览量

2010-04-09 上传

weixin_38523618

- 粉丝: 8

- 资源: 914

最新资源

- dejalist:Dejalist Android应用程序背后的开源代码-Android application source code

- java毕业设计-基于SSM的社区疫情签到管理系统源码+数据库.zip

- leetcode答案-leetcode-answers:这是一个存储leetcode答案的项目。Leetcode是一个专门针对程序员面试的在线

- hiera-eyaml:Hiera的后端,它提供敏感数据的按值非对称加密

- 基于STM32的温度测量系统.zip

- 国际收支分析

- Freedominthesky.GitHub.io

- Ziarmandhost

- Sign_Language_Interpreter:Android应用程序源代码-Android application source code

- JobPriorityQueue:基于优先级的作业队列,可以更好地处理Android项目的不同类型的作业

- leetcode答案-code-challenges:代码挑战

- CIS2348-Ratner

- 策略培训 英文版(十二)

- 51单片机STC89C52RC开发板例程之模拟广告牌字体流动显示.rar

- SafeSlinger-Android:SafeSlinger Android客户端应用程序的开源代码-Android application source code

- google-react-maps:一种使用React的Google Maps API的新方法