TL16C550D , , TL16C550DI

SLLS597E – APRIL 2004 – REVISED DECEMBER 2008 ..................................................................................................................................................

www.ti.com

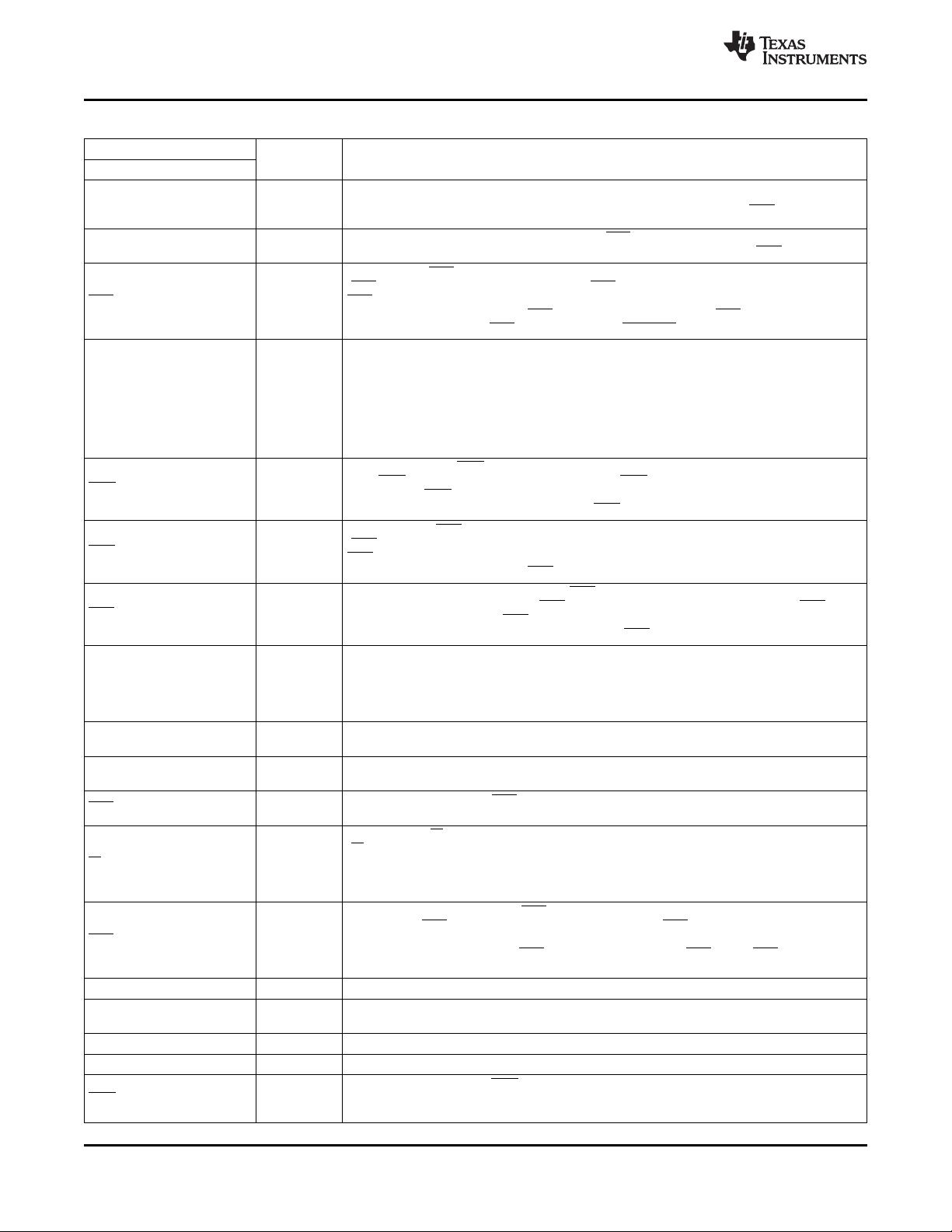

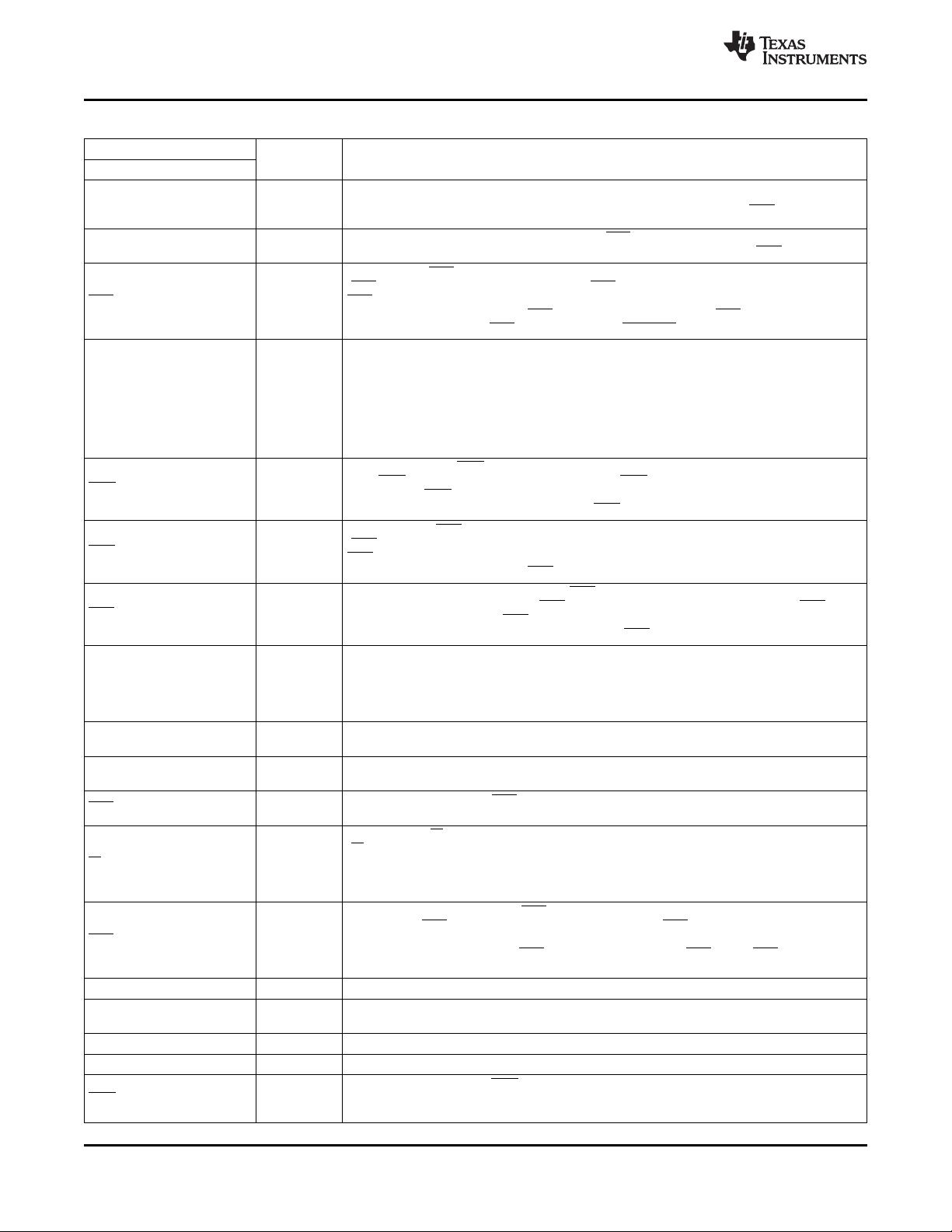

TERMINAL FUNCTIONS (FOR RHB PACKAGE)

TERMINAL

I/O DESCRIPTION

NAME NO.

A0 19

Register select. A0 − A2 are used during read and write operations to select the ACE register

A1 18 I

to read from or write to. See Table 1 for register addresses, and see the ADS description.

A2 17

Chip select. When CS0 and CS1 are high and CS2 is low, these three inputs select the ACE.

CS2 8 I

When any of these inputs are inactive, the ACE remains inactive (see the ADS description).

Clear to send. CTS is a modem status signal. Its condition can be checked by reading bit 4

( CTS) of the modem status register. Bit 0 ( Δ CTS) of the modem status register indicates that

CTS 24 I CTS has changed states since the last read from the modem status register. If the modem

status interrupt is enabled when CTS changes levels and the auto- CTS mode is not enabled,

an interrupt is generated. CTS is also used in the auto-CTS mode to control the transmitter.

D0 29

D1 30

D2 31

D3 32 Data bus. Eight data lines with 3-state outputs provide a bidirectional path for data, control,

I/O

D4 1 and status information between the ACE and the CPU.

D5 3

D6 4

D7 5

Data carrier detect. DCD is a modem status signal. Its condition can be checked by reading

bit 7 ( DCD) of the modem status register. Bit 3 ( Δ DCD) of the modem status register

DCD 26 I

indicates that DCD has changed states since the last read from the modem status register. If

the modem status interrupt is enabled when DCD changes levels, an interrupt is generated.

Data set ready. DSR is a modem status signal. Its condition can be checked by reading bit 5

( DSR) of the modem status register. Bit 1 ( Δ DSR) of the modem status register indicates

DSR 39 I

DSR has changed levels since the last read from the modem status register. If the modem

status interrupt is enabled when DSR changes levels, an interrupt is generated.

Data terminal ready. When active (low), DTR informs a modem or data set that the ACE is

ready to establish communication. DTR is placed in the active level by setting the DTR bit of

DTR 33 O

the modem control register. DTR is placed in the inactive level either as a result of a master

reset, during loop mode operation, or clearing the DTR bit.

Interrupt. When active (high), INTRPT informs the CPU that the ACE has an interrupt to be

serviced. Four conditions that cause an interrupt to be issued are: a receiver error, received

INTRPT 30 O data that is available or timed out (FIFO mode only), an empty transmitter holding register, or

an enabled modem status interrupt. INTRPT is reset (deactivated) either when the interrupt

is serviced or as a result of a master reset.

Master reset. When active (high), MR clears most ACE registers and sets the levels of

MR 35

various output signals (see Table 2).

2,9,

NC I No connection

15, 16,

Read inputs. When either RD1 or RD2 is active (low or high, respectively) while the ACE is

RD1 14 I

selected, the CPU is allowed to read status information or data from a selected ACE register.

Ring indicator. RI is a modem status signal. Its condition can be checked by reading bit 6

( RI) of the modem status register. Bit 2 (TERI) of the modem status register indicates that RI

RI 27 I has transitioned from a low to a high level since the last read from the modem status

register. If the modem status interrupt is enabled when this transition occurs, an interrupt is

generated.

Request to send. When active, RTS informs the modem or data set that the ACE is ready to

receive data. RTS is set to the active level by setting the RTS modem control register bit and

RTS 21 O is set to the inactive (high) level either as a result of a master reset or during loop mode

operations or by clearing bit 1 ( RTS) of the MCR. In the auto- RTS mode, RTS is set to the

inactive level by the receiver threshold control logic.

SIN 6 I Serial data input. SIN is serial data input from a connected communications device.

Serial data output. SOUT is composite serial data output to a connected communication

SOUT 7 O

device. SOUT is set to the marking (high) level as a result of master reset.

V

CC

28 2.25-V to 5.5-V power supply voltage

V

SS

13 Supply common

Write inputs. When either WR1 or WR2 is active (low or high, respectively) and while the

WR1 12 I ACE is selected, the CPU is allowed to write control words or data into a selected ACE

register.

10 Submit Documentation Feedback Copyright © 2004 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TL16C550D TL16C550DI