2003 Oct 30 11

Philips Semiconductors Product specification

Low power single card reader TDA8029

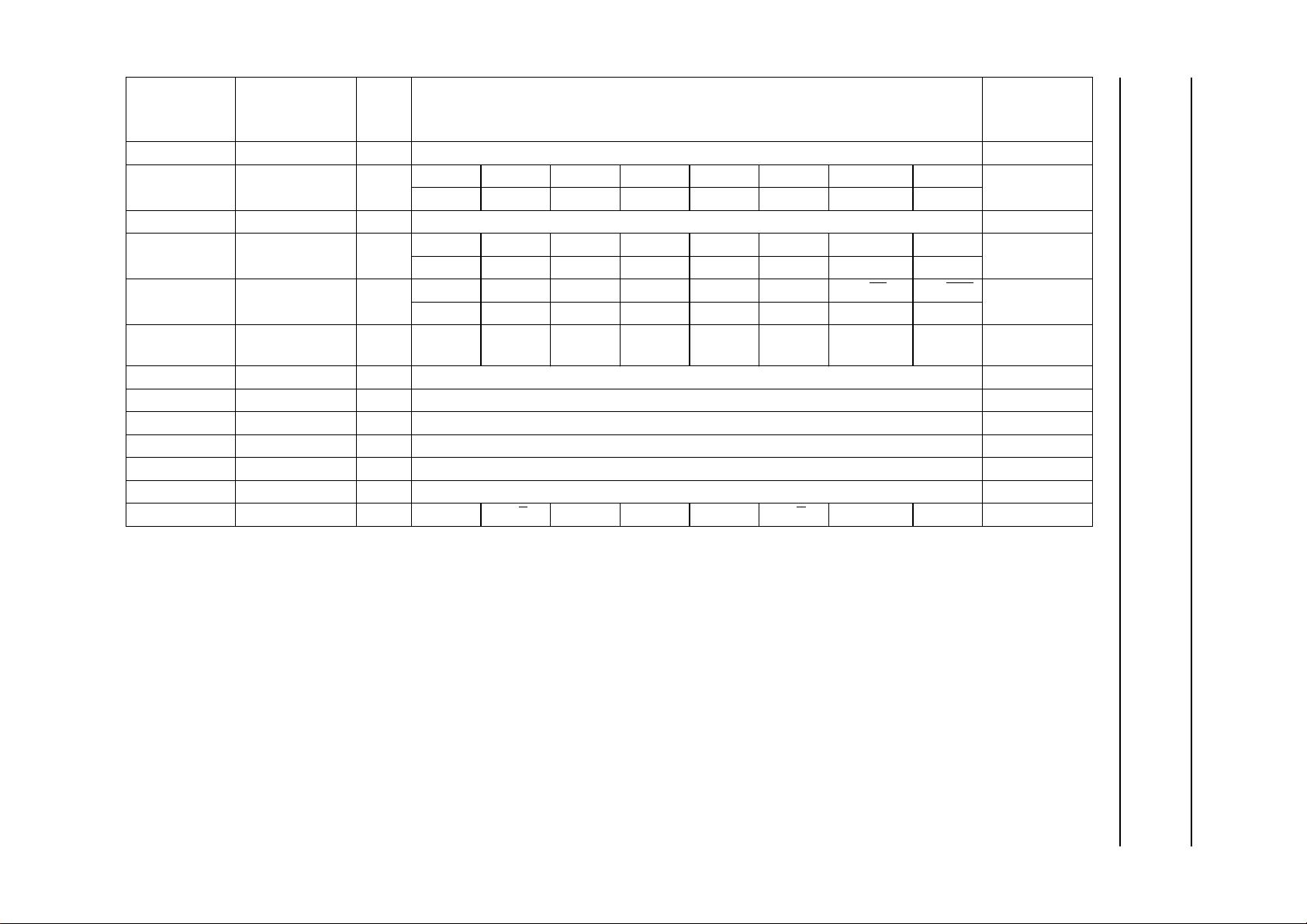

8.1.1 PORT CHARACTERISTICS

Port 0 (P0.7 to P0.0): Port 0 is an open-drain,

bidirectional, I/O timer 2 generated commonly used baud

rates port. Port 0 pins that have logic 1s written to them

float and can be used as high-impedance inputs. Port 0 is

also the multiplexed low-order address and data bus

during access to external program and data memory.

In this application, it uses strong internal pull-ups when

emitting logic 1s. Port 0 also outputs the code bytes during

program verification and received code bytes during

EPROM programming. External pull-ups are required

during program verification.

Port 1 (P1.7 to P1.0): Port 1 is an 8-bit bidirectional

I/O-port with internal pull-ups. Port 1 pins that have

logic 1s written to them are pulled to HIGH level by the

internal pull-ups and can be used as inputs. As inputs,

port 1 pins that are externally pulled LOW will source

current because of the internal pull-ups. Port 1 also

receives the low-order address byte during program

memory verification. Alternate functions for port 1 include:

• T2 (P1.0): Timer/counter 2 external count input / clock

out (see programmable clock out)

• T2EX (P1.1): Timer/counter 2 reload/capture/direction

control.

Port 2 (P2.7 to P2.0): Port 2 is an 8-bit bidirectional I/O

port with internal pull-ups. Port 2 pins that have logic 1s

written to them are pulled to HIGH level by the internal

pull-ups and can be used as inputs. As inputs, port 2 pins

that are externally being pulled to LOW will source current

because of the internal pull-ups. Port 2 emits the

high-order address byte during fetches from external

program memory and during access to external data

memory that use 16-bit addresses (MOVX @DPTR). In

this application, it uses strong internal pull-ups when

emitting logic 1s. During access to external data memory

that use 8-bit addresses (MOV @Ri), port 2 emits the

contents of the P2 special function register. Some port 2

pins receive the high order address bits during EPROM

programming and verification.

Port 3 (P3.7 to P3.3, P3.1 and P3.0): Port 3 is a 7-bit

bidirectional I/O port with internal pull-ups. Port 3 pins that

have logic 1s written to them are pulled to HIGH level by

the internal pull-ups and can be used as inputs. As inputs,

port 3 pins that are externally being pulled LOW will source

current because of the pull-ups.

Port 3 also serves the special features of the 80C51 family:

• RxD (P3.0): Serial input port

• TxD (P3.1): Serial output port

• INT0 (P3.2): External interrupt 0 (pin INT0_N)

• INT1 (P3.3): External interrupt 1 (pin INT1_N

• T0 (P3.4): Timer 0 external input

• T1 (P3.5): Timer 1 external input

• WR (P3.6): External data memory write strobe

• RD (P3.7): External data memory read strobe.

8.1.2 OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively,

of an inverting amplifier. The pins can be configured for

use as an on-chip oscillator. To drive the device from an

external clock source, XTAL1 should be driven while

XTAL2 is left unconnected. There are no requirements on

the duty cycle of the external clock signal, because the

input to the internal clock circuitry is through a

divide-by-two flip-flop. However, minimum and maximum

HIGH and LOW times specified must be observed.

8.1.3 RESET

The microcontroller is reset when the TDA8029 is reset, as

described in Section 8.11.

8.1.4 LOW POWER MODES

This section describes the low power modes of the

microcontroller. Please refer to Section 8.15 for additional

information of the TDA8029 power reduction modes.

Stop clock mode: The static design enables the clock

speed to be reduced down to 0 MHz (stopped). When the

oscillator is stopped, the RAM and special function

registers retain their values. This mode allows

step-by-step utilization and permits reduced system power

consumption by lowering the clock frequency down to any

value. For lowest power consumption the Power-down

mode is suggested.

Idle mode: In the Idle mode, the CPU puts itself to sleep

while all of the on-chip peripherals stay active. The

instruction to invoke the Idle mode is the last instruction

executed in the normal operating mode before the Idle

mode is activated. The CPU contents, the on-chip RAM,

and all of the special function registers remain intact during