Verilog设计的数字频率计课程实战与模块详解

版权申诉

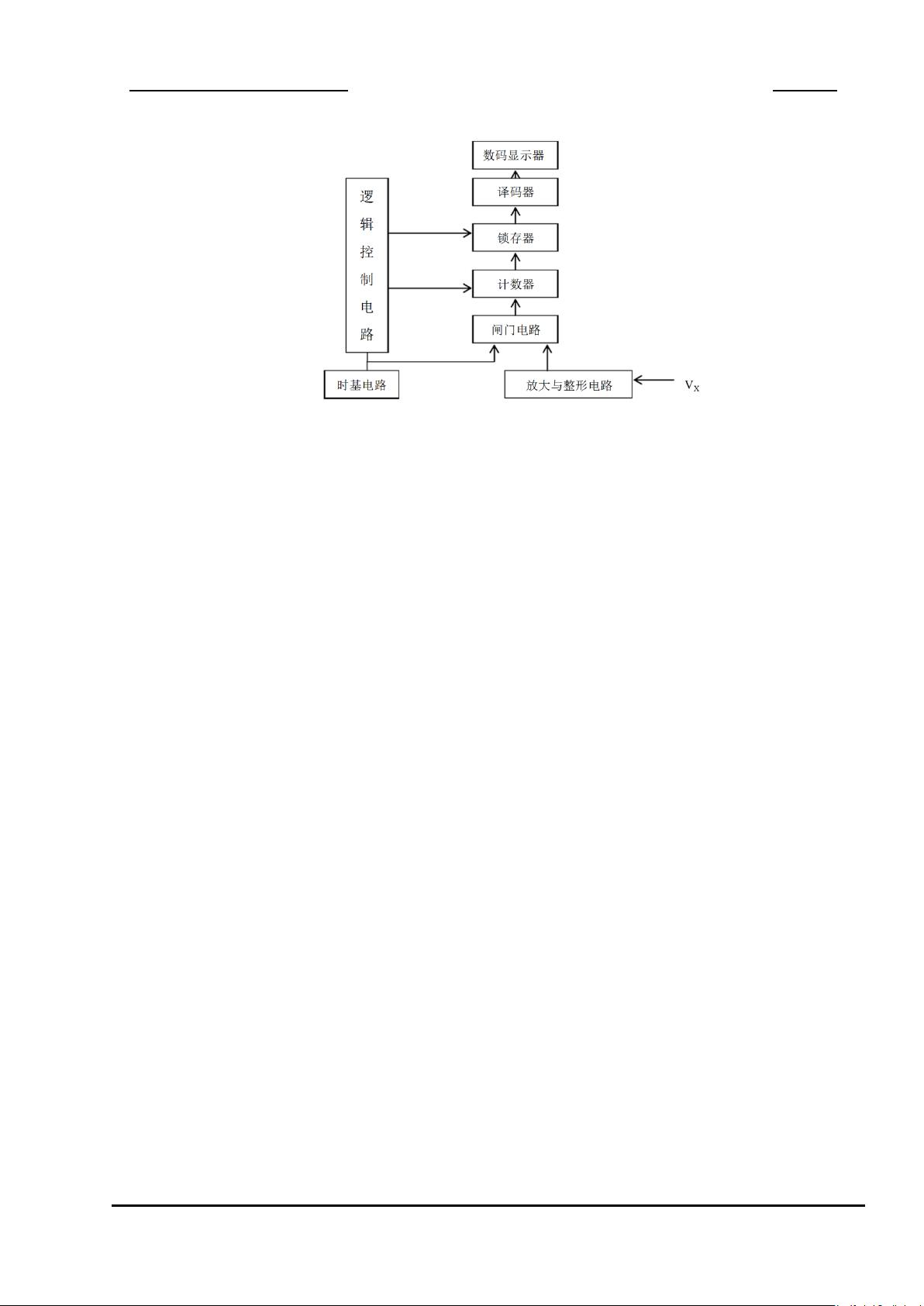

本篇文档详细介绍了数字频率计课程设计的过程和实现。设计者旨在通过电子设计自动化(EDA)提高动手能力和综合技能,选择数字频率计作为研究课题,因其在多个领域,如转速和振动频率测量,具有广泛应用。课程设计采用了Verilog HDL设计方法,这是一种硬件描述语言,它允许设计者以类似于编程的方式描述电子系统的逻辑功能、电路结构和连接方式,相比传统计算机语言如C和Pascal,它更适合于FPGA和CPLD的逻辑实现。

设计分为几个关键部分:

1. 前言:阐述了EDA在电子设计中的重要性,并解释了选择数字频率计设计的原因,强调了Verilog HDL的灵活性和优势。

2. 总体方案设计:讨论了不同设计方法的比较,最终选择了基于FPGA的Verilog设计,因为它可以提供更高的灵活性和效率。

3. 单元模块电路设计:涉及到了多个子模块的详细设计,包括二分频模块、测量校验选择模块、计数器模块、送存选择报警电路模块、锁存器模块以及扫描显示模块,每个模块都有其特定的功能和实现步骤。

4. 软件设计:介绍了软件设计的基本原理,Quartus II的使用,以及设计流程框图,展示了软件如何与硬件协同工作。

5. 系统调试:详细描述了各个模块的仿真调试过程,确保了设计的正确性和稳定性。

6. 系统功能和指标:明确了设计的目标,包括系统功能和性能指标,通过测试和分析,验证了设计的有效性。

7. 结论:总结了整个设计项目,可能包括了学习到的关键技能和收获,以及对未来改进的思考。

8. 总结:对设计进行了深入反思,提出设计的优点和改进之处,表达了对参与者的感谢,并列举了参考文献。

在整个设计过程中,文档强调了理论与实践相结合的重要性,以及在选择元器件时对技术理解的深化。此外,附录提供了各个模块的程序代码、最小系统原理图和PCB图,供读者进一步理解和学习。

290 浏览量

115 浏览量

375 浏览量

290 浏览量

455 浏览量

123 浏览量

209 浏览量

121 浏览量