CPLD优化的FPGA快速并行加载策略

148 浏览量

更新于2024-08-29

收藏 774KB PDF 举报

CPLD对FPGA从并快速加载的解决方案

在现代电子设计中,FPGA(Field-Programmable Gate Array)因其高度灵活性和可重构性,在通信设备和嵌入式系统中扮演着关键角色。FPGA的工作原理基于SRAM结构,这意味着它们在断电后会丢失存储的信息,每次上电时都需要重新配置。随着技术的发展,FPGA的规模不断增大,例如Xilinx的Spartan-6系列的6SLX150T,其加载容量可达4.125 MB,这就对配置效率提出了更高的要求。

FPGA的配置方式主要有四种:JTAG、从串、主从和从并。其中,从并加载方式因其效率和实用性备受关注。从并加载通过并行数据传输,相较于串行方式能显著提高加载速度,减少了配置时间。这种方式的优势在于它可以直接将整个配置文件一次性写入FPGA,无需逐个位进行传输,大大提升了加载过程的效率。

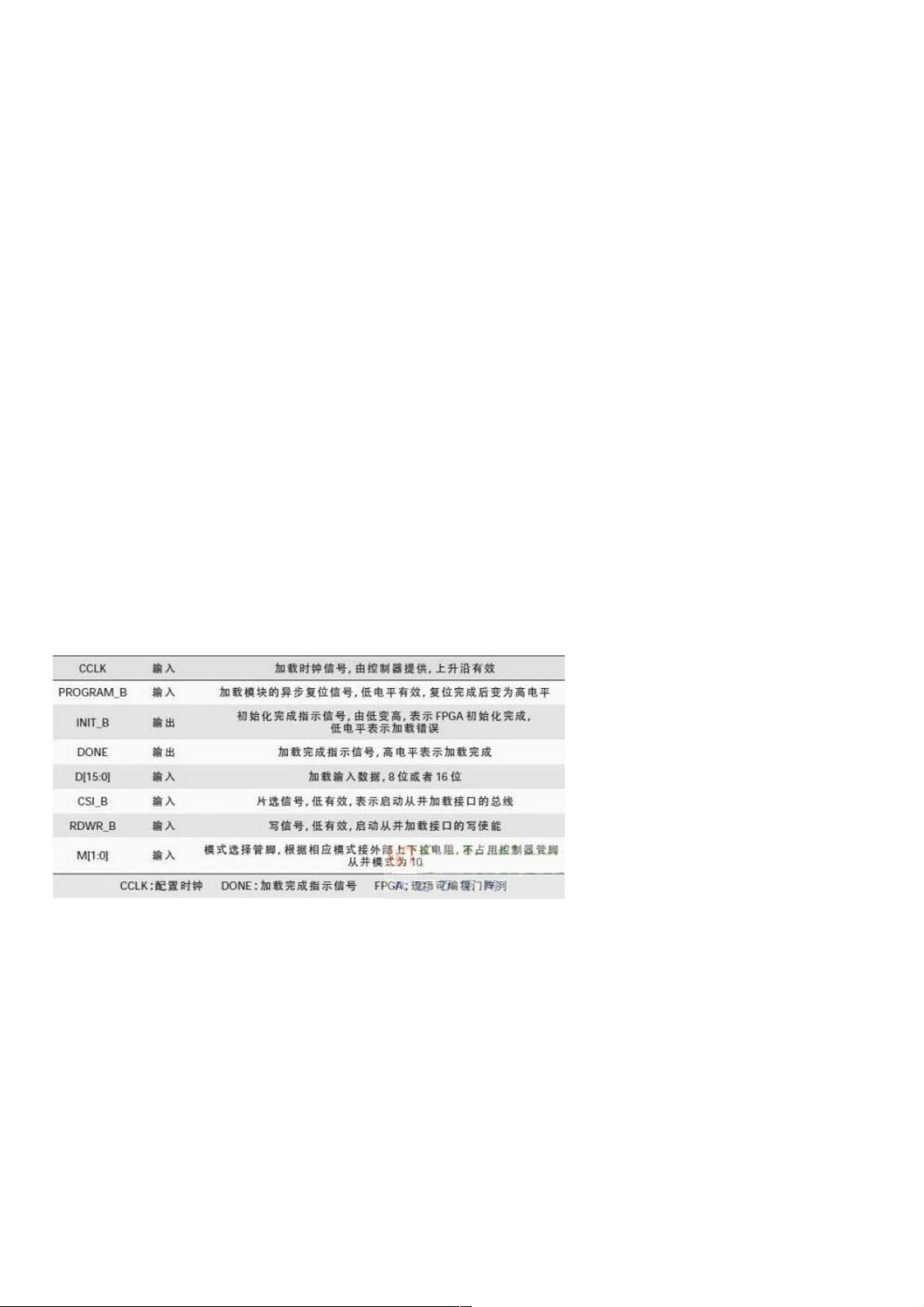

Xilinx的Spartan-6系列FPGA提供了相应的从并接口,用于连接专用的配置器件,如Table 1所示的管脚列表。这些接口通常包括控制信号线、数据线以及时钟线,以确保数据在正确的时间和顺序下被写入。从并加载接口占用较多的硬件资源,但它对于大型FPGA的快速初始化至关重要。

从并加载的实现需要精心设计的硬件和软件配合。硬件方面,需要确保配置电路能够处理高带宽的数据传输,并提供必要的时序控制。软件方面,则需要编写高效的配置工具,以驱动数据流并处理可能的错误检测和纠正机制。

然而,从并加载并非没有挑战。首先,它的实施依赖于特定的硬件配置,如果配置不当,可能会导致数据传输错误。其次,虽然提高了加载速度,但增加了硬件成本,特别是在需要额外存储器的情况下。此外,设计者还需考虑功耗和散热问题,因为高速数据传输可能会带来额外的功耗和热量。

总结来说,CPLD对FPGA的从并快速加载解决方案是一种有效的优化策略,它利用了FPGA的并行特性,降低了配置时间和成本,但同时也需要在硬件设计和软件优化上进行细致的权衡。在实际应用中,工程师需要根据项目需求和资源限制,选择最适合的配置方法,以实现系统的高效和可靠运行。

2020-10-19 上传

2021-07-13 上传

2020-10-19 上传

2021-01-19 上传

2019-09-15 上传

点击了解资源详情

2021-07-13 上传

2021-03-28 上传

2020-08-05 上传

weixin_38692162

- 粉丝: 4

- 资源: 904

最新资源

- Android圆角进度条控件的设计与应用

- mui框架实现带侧边栏的响应式布局

- Android仿知乎横线直线进度条实现教程

- SSM选课系统实现:Spring+SpringMVC+MyBatis源码剖析

- 使用JavaScript开发的流星待办事项应用

- Google Code Jam 2015竞赛回顾与Java编程实践

- Angular 2与NW.js集成:通过Webpack和Gulp构建环境详解

- OneDayTripPlanner:数字化城市旅游活动规划助手

- TinySTM 轻量级原子操作库的详细介绍与安装指南

- 模拟PHP序列化:JavaScript实现序列化与反序列化技术

- ***进销存系统全面功能介绍与开发指南

- 掌握Clojure命名空间的正确重新加载技巧

- 免费获取VMD模态分解Matlab源代码与案例数据

- BuglyEasyToUnity最新更新优化:简化Unity开发者接入流程

- Android学生俱乐部项目任务2解析与实践

- 掌握Elixir语言构建高效分布式网络爬虫