单周期数据通路与处理器性能分析

需积分: 0 162 浏览量

更新于2024-08-04

收藏 1.1MB DOCX 举报

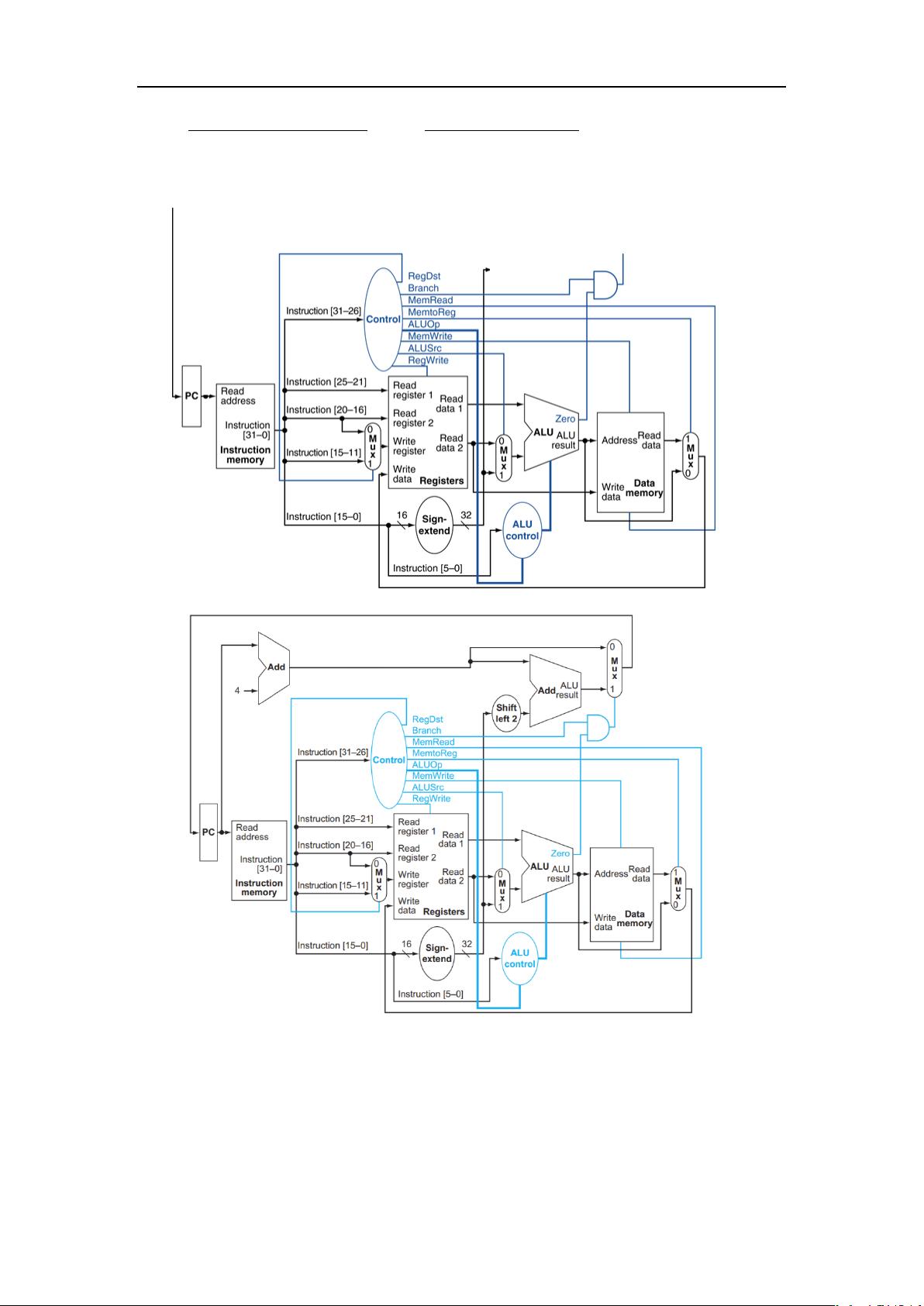

本资源是一份关于计算机系统测试题的答案文档,包含两部分的问题解答。首先,涉及到单周期数据通路的设计问题。在单周期数据通路中执行加法指令(addt0,t1,s2),当t0、t1和s2寄存器的值分别为10、15和20时,由于寄存器地址与实际数值相对应,寄存器部件readregister1和readregister2输入的数值分别是t1寄存器的地址9和s2寄存器的地址18,而Readdata2输出的数值则是s2寄存器的初始值20。

其次,文档涉及的是处理器性能比较以及指令执行效率计算。题目给出了三个处理器P1、P2和P3,它们的时钟频率和指令周期数(CPI)不同。根据MIPS(每秒百万指令数)指标,P2处理器的性能最高,因为其时钟频率较高且CPI较低。当每个处理器执行10秒的程序时,计算了它们的时钟周期数和指令数,P1的周期数为3x10^10,指令数为15;P2的周期数为2.5x10^10,指令数为10;P3的周期数为4x10^10,指令数为22。最后,通过改变时钟频率来实现30%的时间减少,但CPI增加了20%,解得新的时钟频率约为原始频率的1.71倍。

这些内容详细解释了单周期数据通路的工作原理、寄存器操作和处理器性能评估方法,对于理解计算机系统内部结构和性能优化策略具有重要意义。

141 浏览量

237 浏览量

点击了解资源详情

2022-11-11 上传

2018-03-23 上传

2010-05-14 上传

2012-05-18 上传

2021-09-02 上传

2012-03-05 上传

兰若芊薇

- 粉丝: 31

- 资源: 301

最新资源

- Virtex- II 开发流程

- C语言学习100例实例程序.pdf

- 目前最好的JSP分页技术.txt

- gnu-make中文使用手册

- Dojo完美中文手册

- EXT 完美中文手册

- 354235233523452352

- (java笔试)你必须掌握的题目

- Installation Guide for Microsoft Office SharePoint Server 2007

- Thinking.In.Java.3rd.Edition.Chinese.eBook.pdf

- 电脑知识大全 应用资源

- 什么是数据库范式?什么是设计范式?

- java笔试题大汇总

- Scripting in Java 英文版 (pdf)

- MyEclipse 6 Java 开发中文教程.pdf

- redhat安装orcle手册