Verilog实现32位多周期CPU设计与关键模块详解

下载需积分: 0 | DOCX格式 | 157KB |

更新于2024-08-04

| 96 浏览量 | 举报

本Verilog多周期CPU设计文档详细介绍了使用Verilog语言开发一款32位多周期CPU的设计思路和关键模块实现。CPU设计包含以下几个主要部分:

1. **总体设计概述**:

- CPU是32位的,这意味着它能处理32位的数据宽度,具有较高的计算能力。

- CPU采用多周期设计,这意味着指令执行过程被分解为多个时钟周期,提高执行效率和并行性。

- 支持的指令集包括addu(无符号加法)、subu(无符号减法)、ori(原码或)、lw(字节加载)、sw(字节存储)、beq(条件分支)、lui(高20位加载)、jal(跳转并链接)、jr(无条件跳转)、以及nop(无操作)。

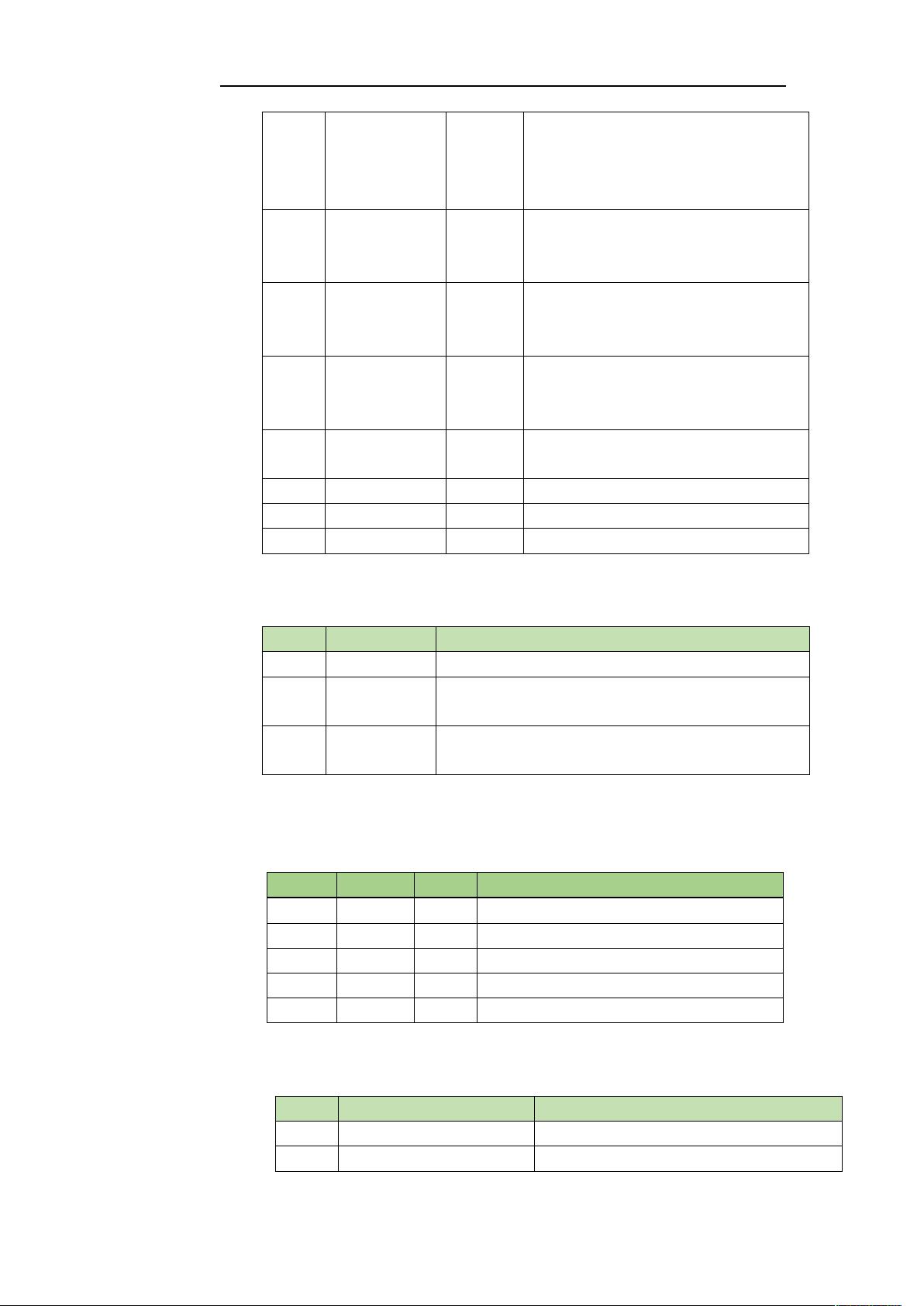

2. **关键模块定义**:

- PC(程序计数器):管理指令执行流程,记录下一条指令地址。

- IM(指令解码器):负责解析指令,提取操作码、源/目的地址等信息。

- IFID(指令格式识别):确认指令格式是否正确。

- NPC(下一周期控制):决定下一周期的操作。

- GRF(通用寄存器文件):存放操作数和临时结果。

- CMP(比较器):用于比较操作数。

- EXT(扩展部件):可能与外部内存交互。

- IDEX(指令解码与执行控制):控制指令执行路径。

- ALU(算术逻辑单元):执行基本算术和逻辑运算。

- EXMEM(执行内存):存储中间结果。

- DM(数据总线管理):处理数据传输。

- Controller(控制器):核心逻辑单元,协调各个模块的工作。

3. **端口说明和功能定义**:

对每个模块都列出了详细的端口说明和功能定义,包括输入、输出和控制信号,以及它们在CPU执行流程中的作用。

4. **测试方案**:

文档提供了测试代码,通过一系列的系统级测试用例来验证CPU的功能,如数据加载、运算、条件转移等。

5. **特殊设计策略**:

该CPU设计采用了不同于传统教程的方法,具有指令暂停控制机制,根据数据冲突情况在D级或E级暂停,确保数据一致性。同时,控制转发和暂停的操作有明确的优先级。

通过阅读这份文档,设计者能够了解如何使用Verilog实现一个复杂的多周期CPU,并理解各部分组件的功能及其相互协作。对于CPU设计、Verilog编程和微处理器原理的学习者来说,这是一份宝贵的学习资料。

相关推荐

傅融

- 粉丝: 32

最新资源

- R14平台上的VLISP - 提升Lisp编程体验

- MySQL5.7数据库管理完全学习手册

- 使用vaadin-material-styles定制Vaadin材料设计主题

- VB点对点聊天与文件传输系统设计及源代码下载

- 实现js左侧竖向二级导航菜单功能及源代码下载

- HTML5实战教程:.NET开发者提升技能指南(英文版)

- 纯bash脚本实现:Linux下的程序替代方案

- SLAM_Qt:简易SLAM模拟器的构建与研究

- 解决Windows 7升级至Windows 10报错0x80072F8F问题

- 蓝色横向二级导航菜单设计及js滑动动画实现

- 轻便实用的tcping网络诊断小工具教程

- DiscordBannerGen:在线生成Discord公会横幅工具介绍

- GMM前景检测技术在vs2010中的实现与运行

- 剪贴板查看工具:文本与二进制数据的终极查看器

- 提升CUBA平台开发效率:集成cuba-file-field上传组件

- Castlemacs: 将简约Emacs带到macOS的Linux开发工具

已收录资源合集

已收录资源合集