i.MX 6Dual/6Quad Applications Processors for Industrial Products, Rev. 4, 07/2015

16 Freescale Semiconductor Inc.

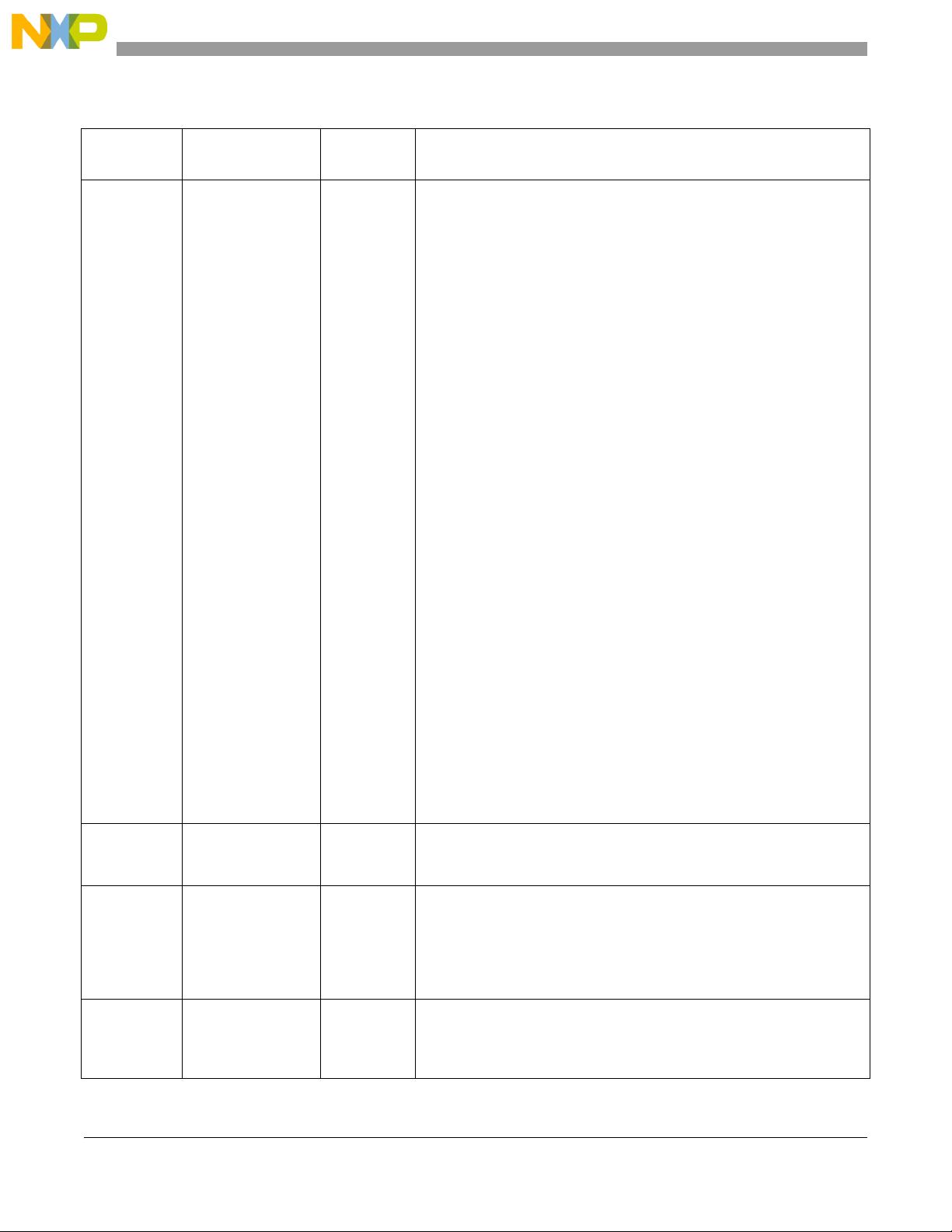

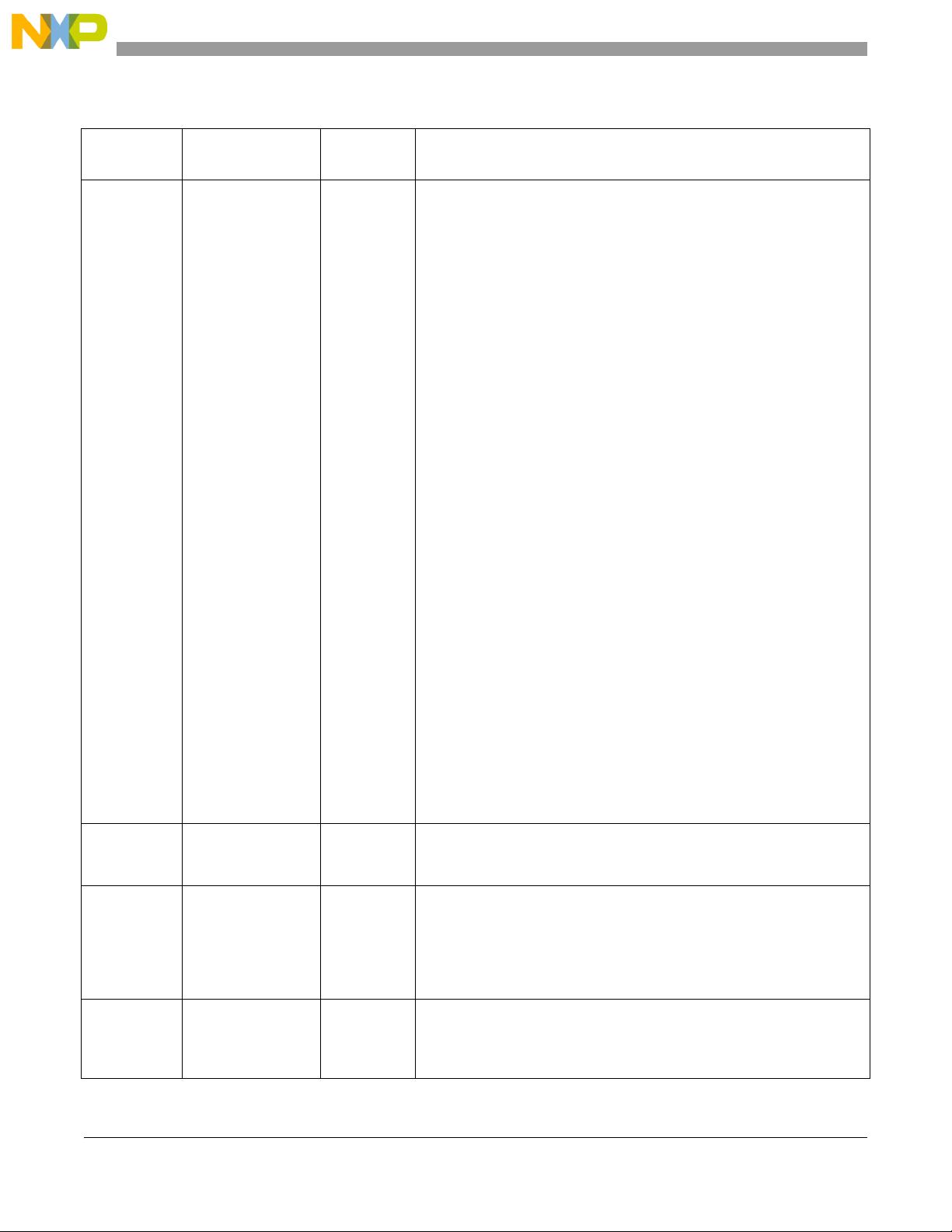

Modules List

uSDHC-1

uSDHC-2

uSDHC-2

uSDHC-4

SD/MMC and SDXC

Enhanced

Multi-Media Card /

Secure Digital Host

Controller

Connectivity

Peripherals

i.MX 6Dual/6Quad specific SoC characteristics:

All four MMC/SD/SDIO controller IPs are identical and are based on the

uSDHC IP. They are:

• Conforms to the SD Host Controller Standard Specification version 3.0

• Fully compliant with MMC command/response sets and Physical Layer

as defined in the Multimedia Card System Specification,

v4.2/4.3/4.4/4.41 including high-capacity (size > 2 GB) cards HC MMC.

Hardware reset as specified for eMMC cards is supported at ports #3

and #4 only.

• Fully compliant with SD command/response sets and Physical Layer

as defined in the SD Memory Card Specifications, v3.0 including

high-capacity SDHC cards up to 32 GB and SDXC cards up to 2TB.

• Fully compliant with SDIO command/response sets and

interrupt/read-wait mode as defined in the SDIO Card Specification,

Part E1, v1.10

• Fully compliant with SD Card Specification, Part A2, SD Host

Controller Standard Specification, v2.00

All four ports support:

• 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to

UHS-I SDR104 mode (104 MB/s max)

• 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52

MHz in both SDR and DDR modes (104 MB/s max)

However, the SoC-level integration and I/O muxing logic restrict the

functionality to the following:

• Instances #1 and #2 are primarily intended to serve as external slots or

interfaces to on-board SDIO devices. These ports are equipped with

“Card Detection” and “Write Protection” pads and do not support

hardware reset.

• Instances #3 and #4 are primarily intended to serve interfaces to

embedded MMC memory or interfaces to on-board SDIO devices.

These ports do not have “Card detection” and “Write Protection” pads

and do support hardware reset.

• All ports can work with 1.8 V and 3.3 V cards. There are two completely

independent I/O power domains for Ports #1 and #2 in four bit

configuration (SD interface). Port #3 is placed in his own independent

power domain and port #4 shares power domain with some other

interfaces.

VDOA VDOA Multimedia

Peripherals

The Video Data Order Adapter (VDOA) is used to re-order video data from

the “tiled” order used by the VPU to the conventional raster-scan order

needed by the IPU.

VPU Video Processing

Unit

Multimedia

Peripherals

A high-performing video processing unit (VPU), which covers many

SD-level and HD-level video decoders and SD-level encoders as a

multi-standard video codec engine as well as several important video

processing, such as rotation and mirroring.

See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for complete

list of VPU’s decoding/encoding capabilities.

WDOG-1 Watchdog Timer

Peripherals

The Watchdog Timer supports two comparison points during each

counting period. Each of the comparison points is configurable to evoke

an interrupt to the ARM core, and a second point evokes an external event

on the WDOG line.

Table 2. i.MX 6Dual/6Quad Modules List (continued)

Block

Mnemonic

Block Name Subsystem Brief Description