Cortex-M处理器架构详解:编程模型与安全特性

149 浏览量

更新于2024-08-30

收藏 385KB PDF 举报

"一文解析Cortex-M处理器架构特性"

Cortex-M处理器是ARM公司推出的微控制器系列,旨在提供高效能、低功耗的解决方案,广泛应用于单片机和深度嵌入式系统。其架构特性包括以下几个核心方面:

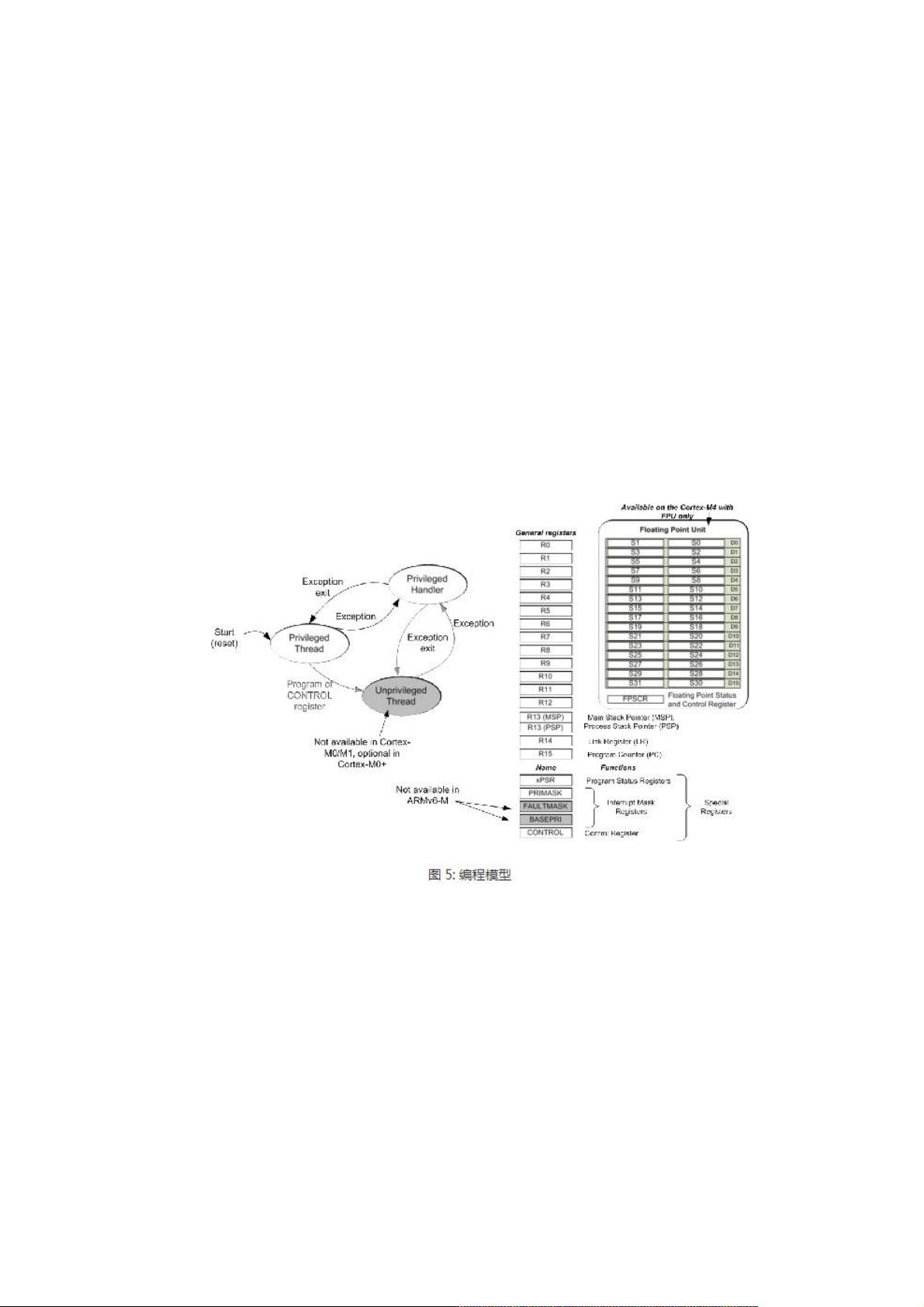

1. **编程模型**:

Cortex-M处理器家族的编程模型统一,使得开发者在不同型号之间切换时能保持一致性。所有Cortex-M处理器都包含通用寄存器R0到R15、程序状态寄存器PSR以及控制寄存器CONTROL和PRIMASK。其中,FAULTMASK和BASEPRI寄存器是特定于Cortex-M3、M4、M7和M33的,用于中断管理。例如,BASEPRI寄存器允许设定一个阈值,低于这个阈值的中断将被禁止,这样可以精细控制中断处理流程。浮点单元(FPU)的浮点寄存器和FPSCR寄存器在具备FPU的Cortex-M处理器上可用。

2. **异常处理模型**:

Cortex-M处理器使用嵌套向量中断控制器(NVIC)来管理和调度中断。NVIC提供了有序的中断处理机制,并且能够支持中断嵌套,确保高优先级中断可以立即中断低优先级中断。这对于实时系统至关重要,因为它确保了响应时间的确定性。

3. **操作系统支持**:

Cortex-M处理器的设计考虑到了实时操作系统(RTOS)的需求。它具有硬件上下文切换的能力,便于OS快速保存和恢复任务状态。此外,硬件还提供了预取中断(PRIVileged Access Never,PAN)和控制寄存器(CONTROL)等功能,以支持特权级别和用户级别的操作,增强了安全性。

4. **TrustZone安全扩展**:

针对安全应用,Cortex-M处理器集成了TrustZone技术,创建了安全和非安全两种执行状态。这使得系统可以划分出敏感区域,保护关键数据和代码免受恶意攻击。

5. **错误处理**:

在Cortex-M架构中,错误处理机制非常健全。FAULTMASK寄存器在复杂的错误场景下特别有用,它允许在发生错误时暂时屏蔽中断,以便进行安全的故障恢复。此外,系统还支持多种故障状态,如BusFault、MemoryManagement Fault和UsageFault,以帮助调试和诊断问题。

总结来说,Cortex-M处理器以其高度一致的编程模型、强大的中断处理能力、对RTOS的支持、高级安全特性和完善的错误处理机制,在微控制器领域占据重要地位。这些特性使得Cortex-M系列成为从简单物联网设备到复杂工业控制系统的理想选择。

131 浏览量

710 浏览量

2023-03-09 上传

2023-03-09 上传

199 浏览量

199 浏览量

点击了解资源详情

点击了解资源详情

weixin_38735101

- 粉丝: 1

最新资源

- React.js实现的简单HTML5文件拖放上传组件

- iReport:强大的开源可视化报表设计器

- 提升代码整洁性:Eclipse虚线对齐插件指南

- 迷你时间秀:个性化系统时间显示与管理工具

- 使用ruby-install一次性安装多种Ruby版本

- Logality:灵活自定义的JSON日志记录器

- Mogre3D游戏开发实践教程免费分享

- PHP+MySQL实现的简单权限账号管理小程序

- 微信支付统一下单签名错误排查与解决指南

- 虚幻引擎4实现的多边形地图生成器

- TouchJoy:专为触摸屏Windows设备打造的屏幕游戏手柄

- 全方位嵌入式开发工具包:ARM平台必备资源

- Java开发必备:30个实用工具类全解析

- IBM475课程资料深度解析

- Java聊天室程序:全技术栈源码支持与学习指南

- 探索虚拟房屋世界:house-tour-VR应用体验