DDR SDRAM规格与特性:双倍数据速率内存标准

需积分: 43 79 浏览量

更新于2024-07-25

收藏 672KB PDF 举报

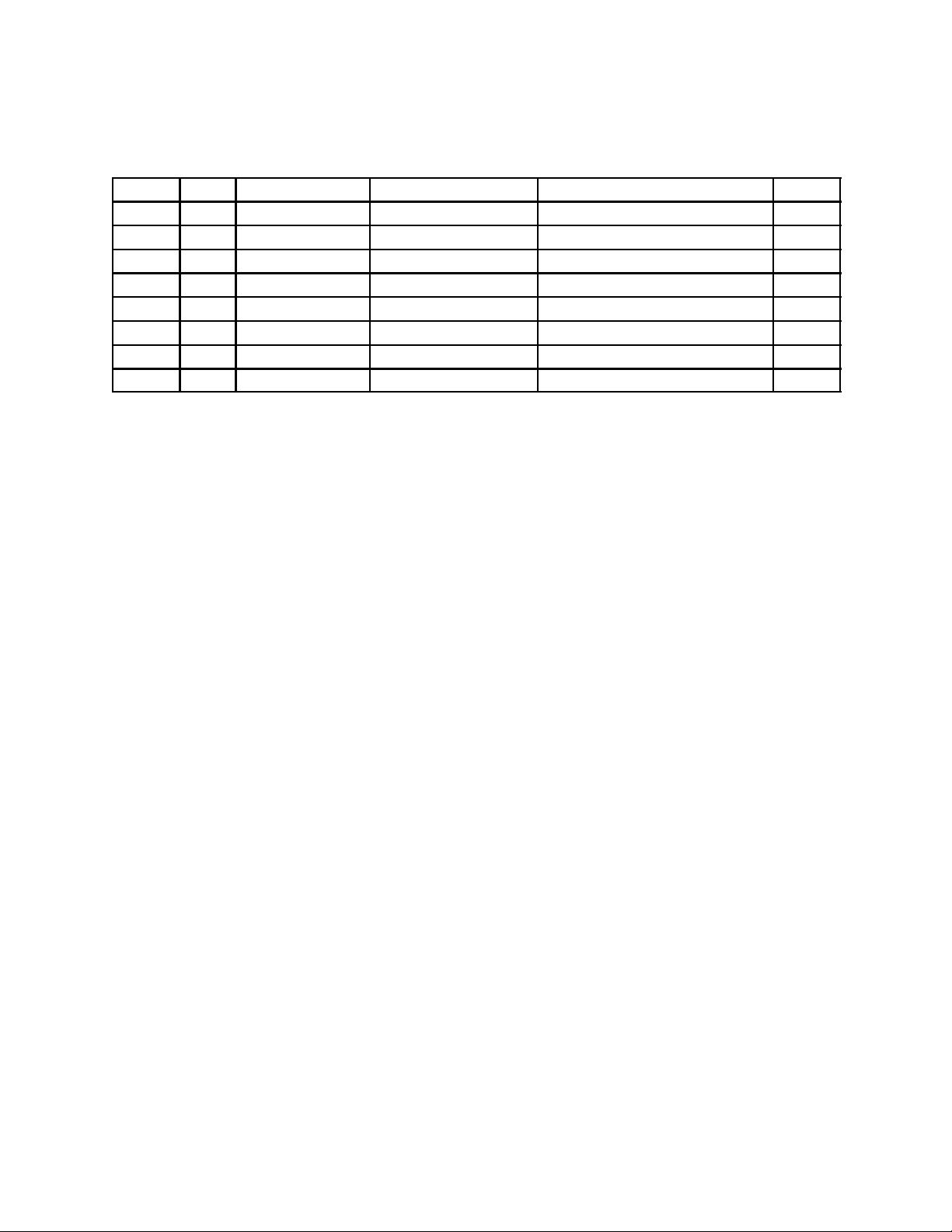

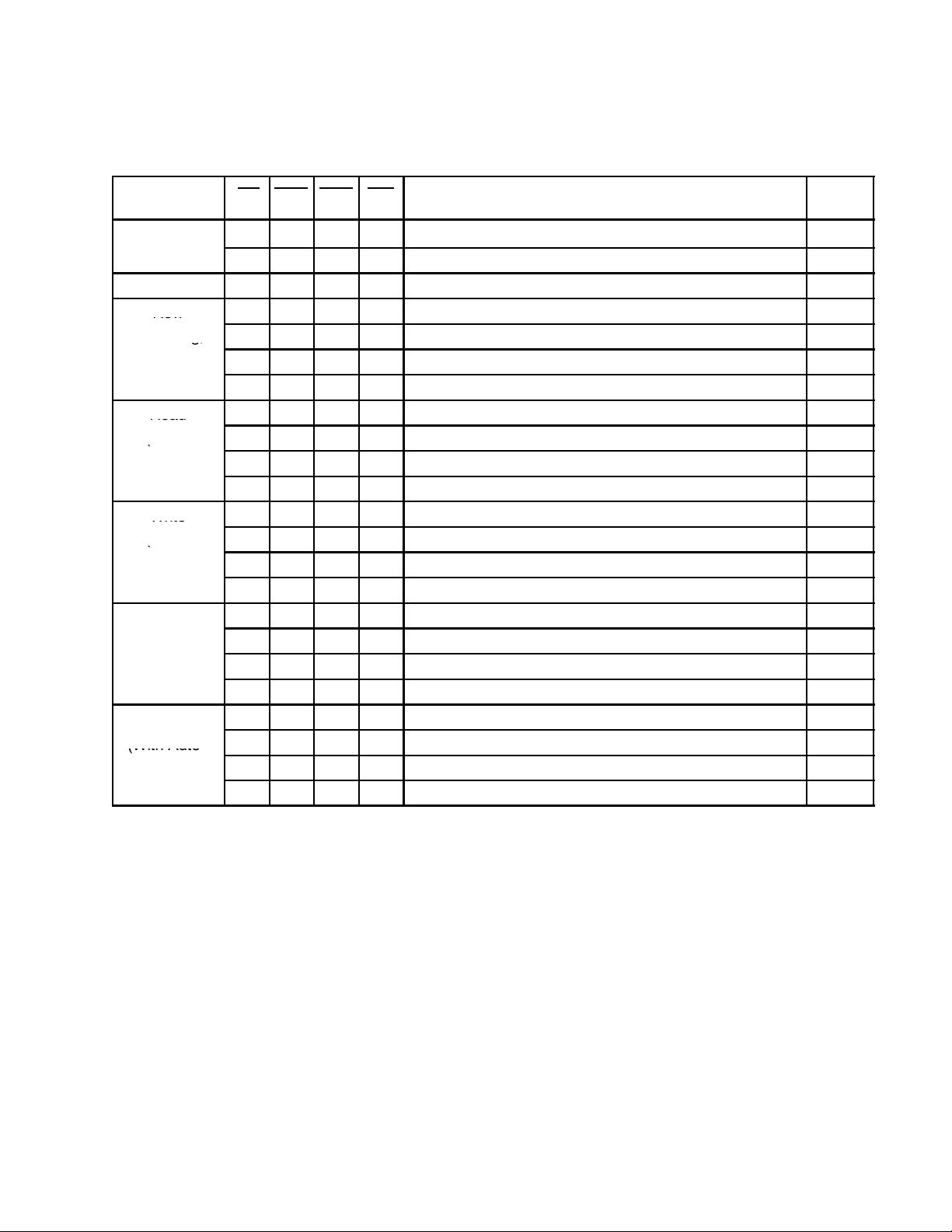

"JESD79F标准详细介绍了Double Data Rate (DDR) SDRAM的规范,这是一种高速CMOS动态随机存取存储器,内部配置为四银行结构。该规格涵盖了不同容量的DDR SDRAM,从64 Mb到1 Gb不等。设备的数据传输率翻倍,每个时钟周期可进行两次数据传输。此外,它还具备双向数据 strobe (DQS) 功能,用于接收和发送数据,并与数据同步,以便在接收端捕捉数据。DQS信号在读取操作中与数据边缘对齐,而在写入操作中则与数据中心对齐。"

DDR SDRAM的主要特点包括:

1. 双倍数据速率架构:DDR SDRAM能在每个时钟周期的上升沿和下降沿传输数据,从而实现了比传统SDRAM更高的数据传输速度。

2. 数据 strobe (DQS):DQS信号与数据一起发送和接收,为数据捕获提供精确的时钟参考。在读取操作中,DQS信号与数据边缘对齐;在写入操作中,DQS信号位于数据的中心,确保数据传输的准确性。

3. 差分时钟输入:使用CK和CK#(反相时钟)信号,提高了信号完整性,降低了干扰。

4. 时钟和数据对齐:DLL(延迟锁相环)用于同步DQ和DQS信号与时钟CK的转换,确保数据传输的精确时序。

5. 命令输入:命令在每个时钟CK的正沿进入,而数据和数据掩码则参照DQS的两个边沿。

6. 四个内部银行:允许并发操作,提高了内存访问效率。

7. 写入数据的datamask (DM):允许在写操作中选择性地忽略某些数据位。

8. 不同的突发长度:支持2、4或8个连续的地址访问。

9. CAS延迟:提供2或2.5的CAS延迟选项,DDR400还支持CL=3的更低延迟。

10. 自动预充(AUTO PRECHARGE)功能:每个突发访问后自动进行预充操作,提高内存操作的连续性。

11. 自动刷新和自刷新模式:确保内存数据的完整性,即使在系统待机时也能保持数据。

12. I/O接口电压:采用2.5V(SSTL_2兼容)接口,确保低功耗和稳定性。

13. VDDQ:这是数据线电源电压,与VDD主电源电压一起,为设备提供稳定的电源环境。

DDR SDRAM的设计和特性使其成为高性能计算、图形处理和其他需要高速数据传输的应用的理想选择。这些技术进步对于满足不断增长的系统带宽需求至关重要。

2018-04-26 上传

104 浏览量

144 浏览量

307 浏览量

215 浏览量

192 浏览量

205 浏览量

justin_2007

- 粉丝: 0

- 资源: 1

最新资源

- Matrix:开发用于使用pygame学习矩阵的教具

- Termy:具有自动完成功能的终端

- Catfish BLOG 鲶鱼博客系统 v2.0.51

- em算法matlab代码-Digital-Device-Design-for-Power-Factor-Calculation:功率因数(PF

- OSEMR-开源

- adb驱动亲测可用解压即可

- GitHub-Health-Project-Article:关于我对免费和开源,非限制性,道德和安全的医疗健康项目的计划和贡献的文章

- disaster_response_NLP_pipeline:用于灾难响应消息分类的NLP管道

- benchdb-accumulation-register:ouchdb的累积寄存器

- keil3/4 采用单片机或ARM控制路灯四季不同天黑时间的路灯开关控制,且能根据节假日单独设置开关时间。

- matlab标注字体代码-figexp:将Matlab图形导出为各种格式

- 西门子ET_200S +6 ES7_131_4BB00外形图.zip

- RxBasicsKata:RxJava学习者的实际挑战

- postgres_dba:缺少用于Postgres DBA和所有工程师的有用工具集

- NetEpi-开源

- typescript-express-static-analysis-template