FPGA实现的DVI输出图像选区截取技术

需积分: 9 103 浏览量

更新于2024-09-09

收藏 350KB PDF 举报

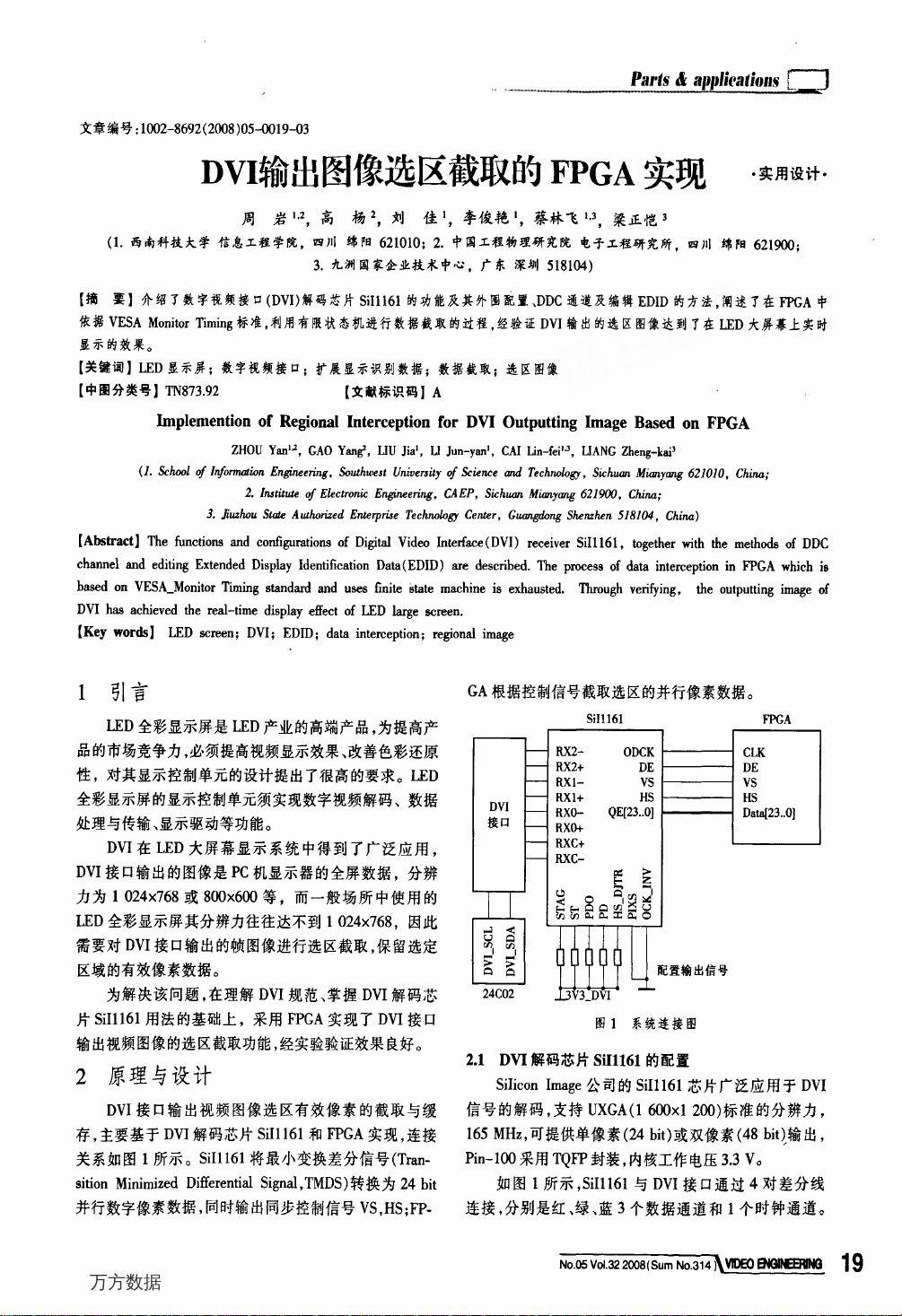

本文档主要探讨了如何在FPGA(Field-Programmable Gate Array)中实现DVI(Digital Video Interface)输出图像的选区截取技术。DVI是一种广泛用于计算机显示系统的接口标准,用于传输高清视频信号。Silll61是一款用于DVI解码的芯片,它在图形处理和视频传输中扮演着关键角色。

首先,作者详细介绍了Silll61芯片的功能及其外围配置,这包括了其基础架构、数据接收和处理能力,以及如何与显示器或其他输出设备连接。Silll61支持DDC(Display Data Channel)通信,这是一种用于控制显示器设置的低速串行接口,通过它可以获取和编辑EDID(Extended Display Identification Data),即显示器的自描述数据,以确保最佳的显示效果。

文章的核心部分着重于如何在FPGA中利用VESAMonitorTiming标准进行数据截取。VESA(Video Electronics Standards Association)Monitor Timing标准提供了一套规范,定义了视频信号的帧率、像素时序等重要参数,这对于确保图像同步和稳定性至关重要。在FPGA中,作者通过构建一个基于有限状态机(Finite State Machine, FSM)的模块,这个FSM负责监控和解析DVI数据流,根据预设的规则或用户指定的选区,动态地从数据流中提取并截取所需的图像区域。

设计过程可能涉及硬件描述语言(HDL)如Verilog或 VHDL 的编程,通过FPGA器件如Xilinx或Intel Altera的器件来实现。FSM会根据输入的时序信号和预设条件,选择性地存储或丢弃数据,从而生成选区图像。这个过程需要精确的时间同步和逻辑设计,以确保选区图像能够实时显示在LED显示屏上,满足高分辨率和高刷新率的需求。

总结起来,这篇论文提供了FPGA技术在DVI输出图像选区截取中的具体实现方法,包括硬件配置、DDC通道管理、EDID编辑,以及基于标准的实时数据处理策略。这对于在嵌入式系统、工业控制或视频处理应用中优化显示效果,提升用户体验具有重要意义。

2020-08-31 上传

2009-06-29 上传

2021-07-13 上传

2021-10-25 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

baidu_34639589

- 粉丝: 0

- 资源: 5

最新资源

- 数据通信基础知识——网络入门

- 51单片机Keil C语言入门教程\

- CSS网页布局开发小技巧24则

- tlc549pdf资料

- JavaMail开发手册

- MAXIMO扩展开发环境配置

- 在VisualBasic中构造OpenGL类模块实现三维图形设计

- ActionScript 3.0

- H.264_MPEG-4 Part 10 White Paper.pdf

- JavaConference

- Eclipse J2ME WTK开发教程

- More Effective C++(中文清晰版)

- Warehouse Layout Design

- Android Eclipse开发教程

- BlackBerry Eclipse开发教程

- Android Ant 开发入门教程