华为2020机试:数字芯片与Verilog编程考题解析

需积分: 0 131 浏览量

更新于2024-06-26

1

收藏 1.53MB PDF 举报

"华为2020届机试题目,主要涉及数字芯片设计与Verilog编程,适合有电子技术基础和Verilog编程经验的人群。试卷包含选择题和主观题,如撕代码题,测试考生对时序电路、门控时钟、触发器以及Verilog语法的理解和应用能力。"

在华为2020届机试中,涉及的知识点主要包括:

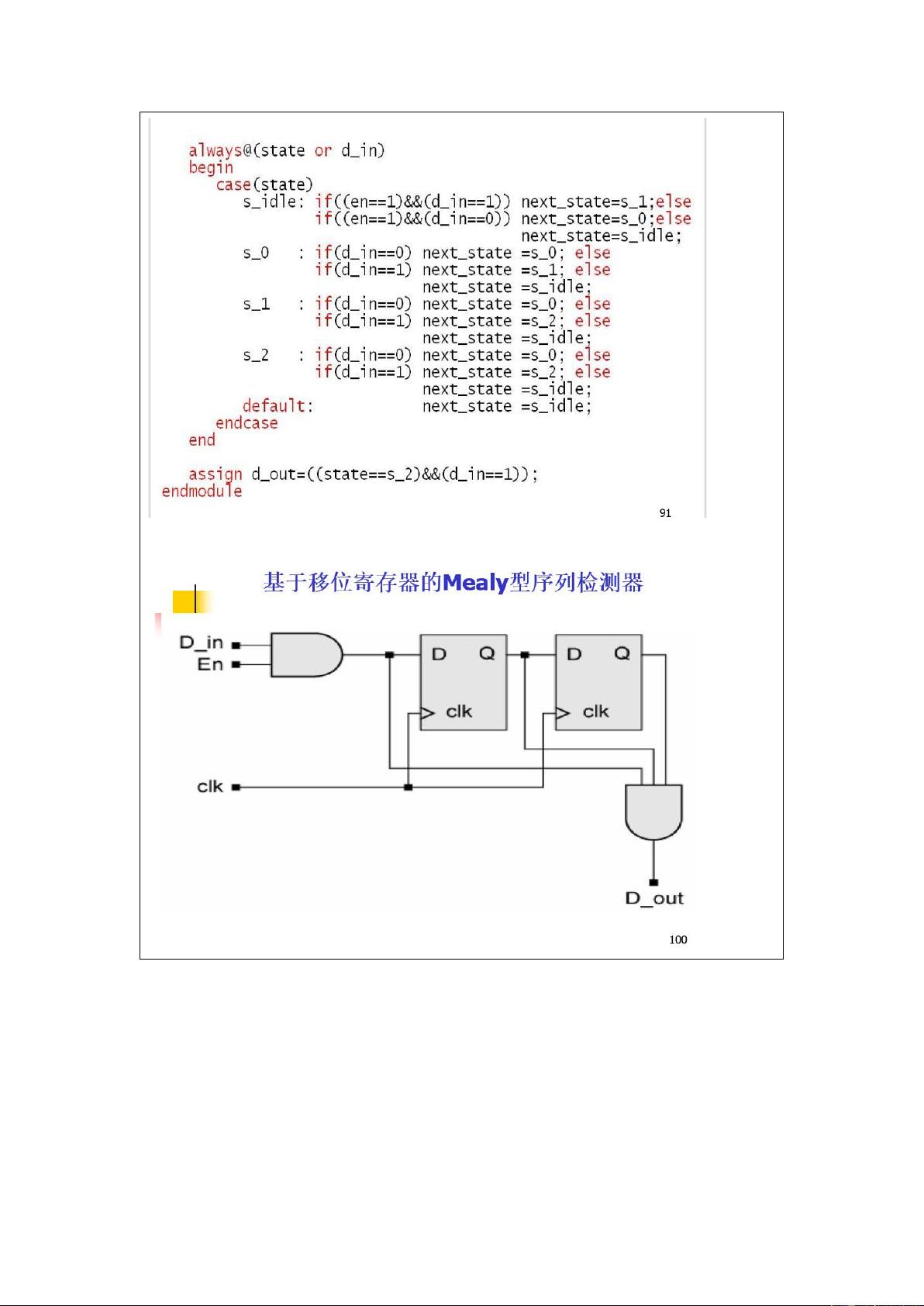

1. **状态机类型**:米利状态机(Mealy machine)和摩尔状态机(Moore machine)的区别。米利状态机的输出不仅取决于当前状态,还与输入信号有关,而摩尔状态机的输出仅由当前状态决定。

2. **存储器深度与位宽**:例如,Reg[255:0]mem[31:0]的深度是32,位宽是256。

3. **门控时钟**:门控时钟的控制原则,如NAND门和AND门的控制信号应在时钟低电平时跳变,OR门和NOR门的控制信号应在时钟高电平时跳变。门控时钟用于降低功耗。

4. **触发器**:触发器的分类,按功能可分为RS触发器、JK触发器、D触发器和T触发器,按结构可分为主从触发器和边沿触发器。每种触发器都有其特定的功能,如RS触发器支持保持、置0和置1,JK触发器支持保持、置0、置1和翻转,T触发器支持保持和翻转,D触发器支持置0和置1。

5. **Verilog语法**:在if语句中,如果无else分支,Verilog编译器可能会生成锁存器,而不是节省面积。这不符合综合优化的原则。

6. **异步信号处理**:处理异步信号时通常需要使用同步器,如单bit异步信号可能需要打两拍或三拍来确保正确同步,而异步总线则需要更复杂的同步机制。在跨时钟域处理中,需避免直接连接不同时钟域的信号,应先同步再处理。

7. **时钟域转换(CDC)**:在处理异步信号时,需要考虑寄存器输出和逻辑运算的同步问题。例如,将数据总线同步到地址总线,或者先进行逻辑运算再同步。

这些知识点反映了数字芯片设计中的核心概念,包括状态机设计、存储器属性、时序逻辑控制、硬件描述语言的应用以及时钟域之间的数据传输。掌握这些内容对于理解和设计数字集成电路至关重要。

2680 浏览量

2024-04-26 上传

147 浏览量

373 浏览量

1824 浏览量

Clock_926

- 粉丝: 153

最新资源

- Vue.js基本语法及其特性与扩展插件解析

- 黑白风格企业PPT模板下载

- 起亚概念车电脑主题XP版:科技与美学的融合

- 智能设备远程管理新体验:永红爱控软件v1.0.0515.11.21

- 自制恩智浦智能车带按键OLED显示屏编程教程

- ADS_Calculator: 掌握后缀表达式计算

- NISO2021大会:深入探讨JavaScript技术发展

- Java语言压缩包子文件管理与使用教程

- 掌握音乐同步魔法:TomorrowMusic让生活更有旋律

- 儿童钢琴兴趣班PPT模板免费下载

- 绿豆蛙xp主题:可爱桌面主题的完美呈现

- C++项目开发:POSGSOFT第一个项目分析

- Teorex.Inpaint 8.1:便捷的Windows去水印软件

- 猪拉丁翻译器:掌握Pig Latin语言转换技巧

- UI开发必备:MCU字体字库制作软件介绍

- simple-log-analyzer:打造高效Log4J日志解析到数据库解决方案