使用AbstractGenerator创建LEF模型以加速IP整合

需积分: 42 100 浏览量

更新于2024-09-13

1

收藏 478KB PDF 举报

"本文主要探讨了在集成电路设计中,如何利用Abstract Generator生成LEF(布局交换格式)模型,以支持System-on-Chip (SoC)的IP整合过程。随着芯片技术复杂度的不断增长,IP交易成为加快产品上市时间的重要手段。因此,IP供应商必须提供相关的模型,以促进IP的集成。LEF是描述物理库单元几何属性的标准格式,包括引脚位置、层定义和通孔,用于放置和布线等步骤。在完成设计的自动布局与布线(APR)并验证无误后,可以通过Abstract Generator生成LEF文件,便于其他设计在整合该IP时使用。"

在当前的集成电路设计领域,由于技术的快速发展,设计复杂度不断提高,使得投入更多的资源进行IC设计的同时,也需要通过知识产权(IP)的交易来加速产品开发。LEF(Library Exchange Format)作为描述物理库单元的一种标准格式,其重要性不言而喻。LEF文件包含了诸如单元的物理尺寸、引脚位置、使用的层信息、最小线宽和间距等关键数据,这些信息对于自动布局与布线工具至关重要,能够确保设计的正确性和可制造性。

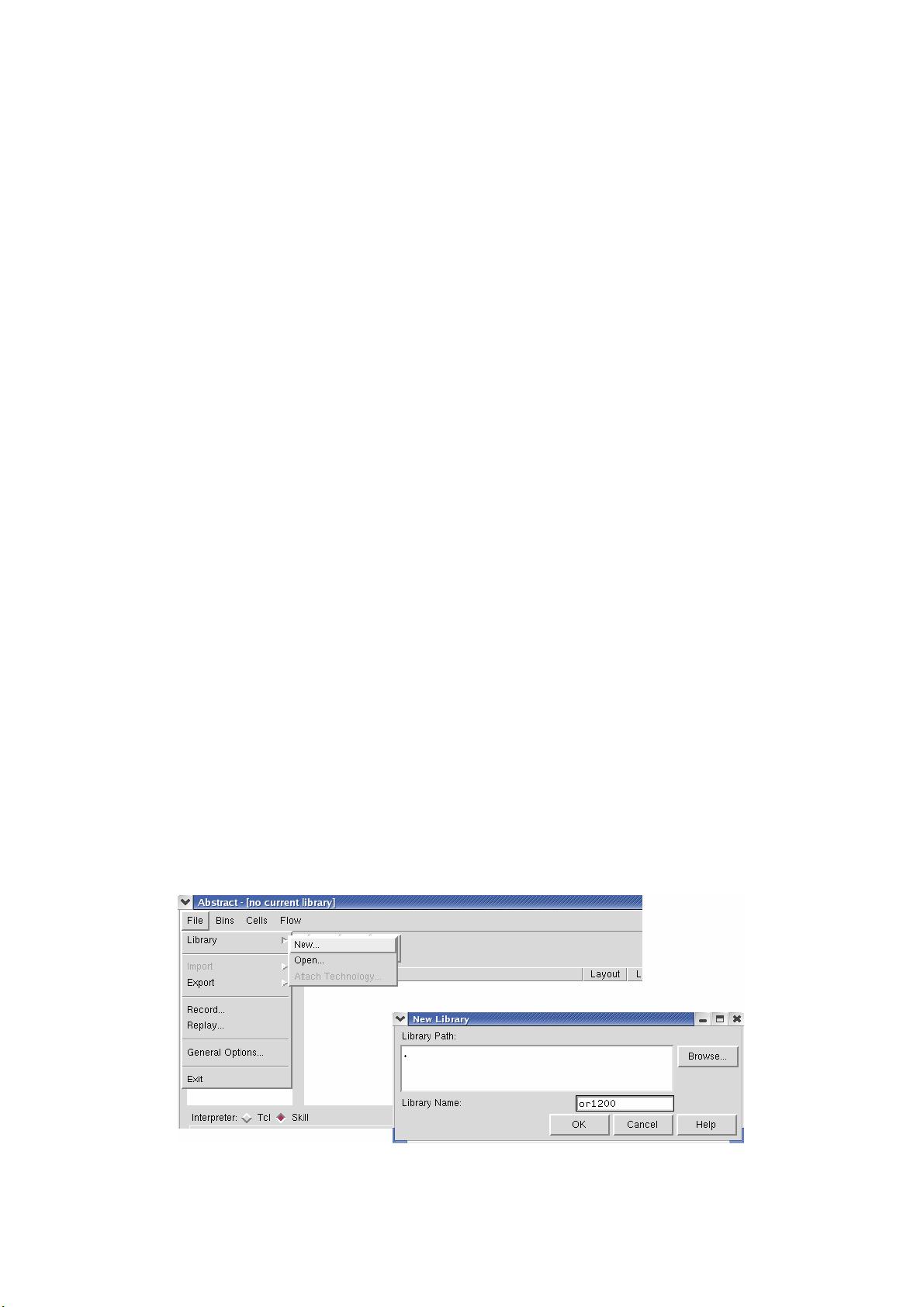

IP供应商在提供IP时,不仅要交付功能完善的逻辑描述,还需要提供LEF模型,这个模型是实现IP整合的关键。Abstract Generator就是用来生成这种LEF模型的工具,它可以帮助设计师从已完成的电路设计中提取必要的物理信息,生成符合标准的LEF文件。

在设计流程中,经过设计规则检查(DRC)、光刻相似性检查(LVS)、等效性检查(Equivalent Check)、时序分析(Timing Analysis)以及后仿真(Post Simulation)等一系列验证,确保设计无误后,Abstract Generator会被调用来生成LEF模型。这个LEF模型将用于下游的SoC集成阶段,确保其他设计能够顺利地将此IP融入到整体设计中,进行正确的布局和布线。

LEF模型在SoC IP整合中扮演着核心角色,Abstract Generator则是生成这些模型的必备工具,它简化了IP的复用和集成过程,提高了设计效率,降低了设计风险。理解并熟练运用LEF和Abstract Generator是现代集成电路设计工程师必须掌握的关键技能之一。

2021-09-01 上传

475 浏览量

2009-03-23 上传

1385 浏览量

351 浏览量

2022-06-16 上传

taoyr

- 粉丝: 2

- 资源: 15