使用Xilinx PCI Express解决方案实现总线主控设计

需积分: 48 107 浏览量

更新于2024-07-07

收藏 2.21MB PDF 举报

"XAPP1052(v3.3) - 使用Xilinx Endpoint PCI Express解决方案设计和实现总线主控设计的应用笔记"

这篇应用笔记详细介绍了如何利用Xilinx的Endpoint PCI Express解决方案设计和实现一个总线主控(Bus Master)设计。Xilinx是全球知名的可编程逻辑器件供应商,其Endpoint PCI Express解决方案旨在帮助开发者在FPGA(Field-Programmable Gate Array)上构建高效的数据传输系统。

总线主控(Bus Master)是一种硬件机制,它允许设备独立于CPU直接访问系统内存,进行DMA(Direct Memory Access)操作,提高数据传输效率。应用笔记中的性能演示参考设计包含了总线主控功能,用户可以根据此设计评估在不同系统中的可实现性能,并作为特定应用的总线主控DMA设计起点。

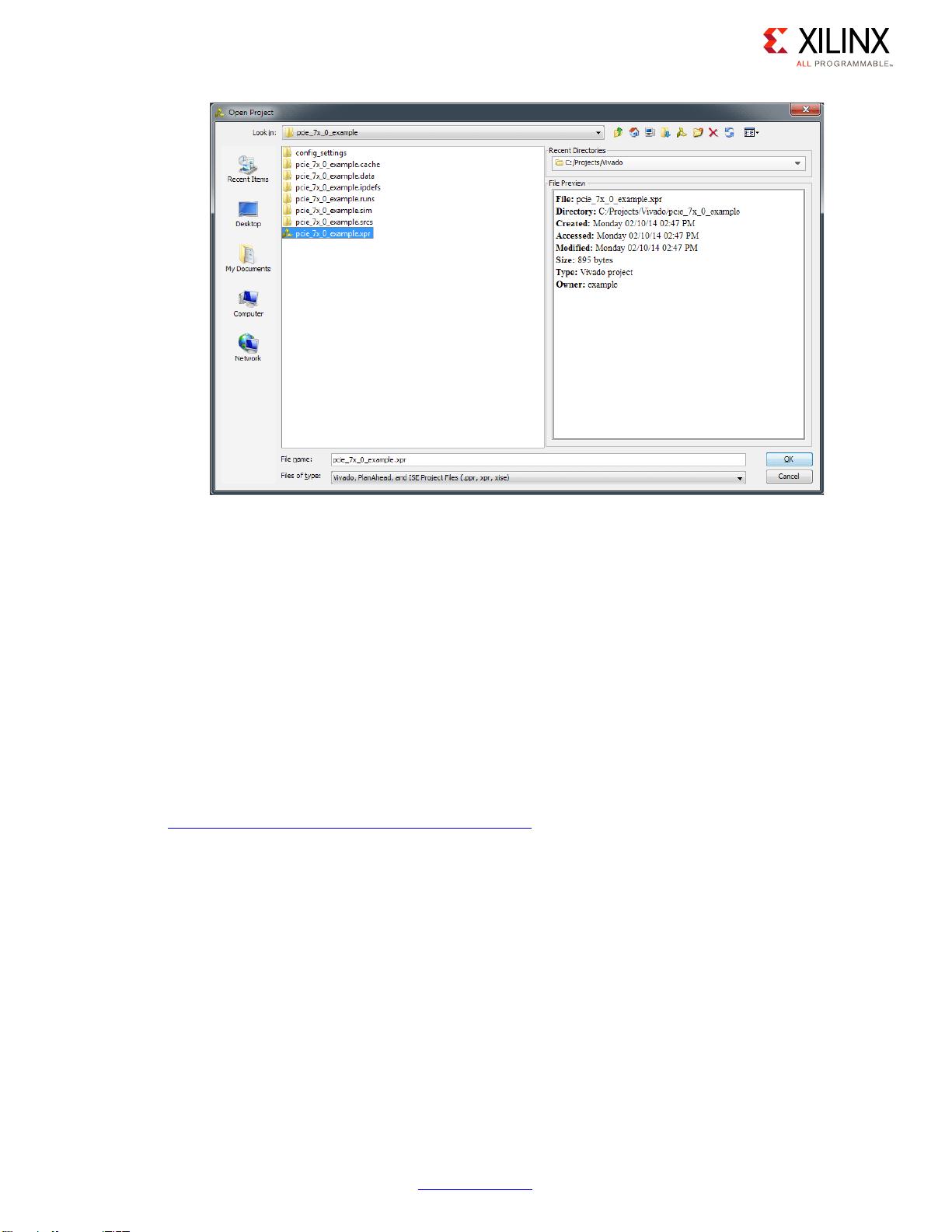

参考设计已更新,增加了对Kintex-7系列FPGA的支持,采用了Vivado Design Suite,这是一个先进的设计工具,目标平台是Xilinx KC705评估套件板。Vivado Design Suite提供了完整的硬件描述语言(HDL)综合、布局布线以及仿真等功能,使得设计过程更加高效。

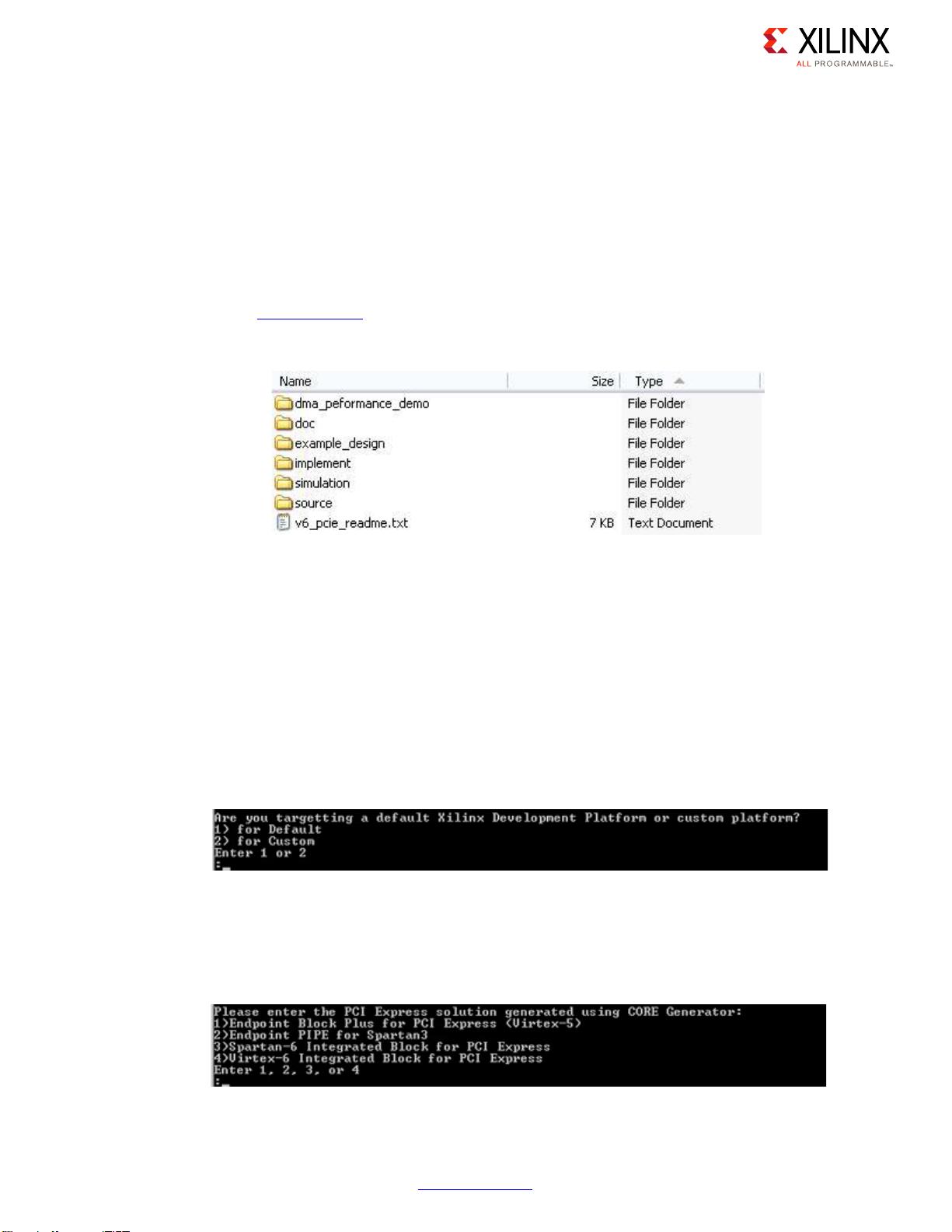

此外,该参考设计还包括了针对Virtex-6和Spartan-6 FPGA的PCI Express集成块,以及使用Virtex-5 FPGA的Endpoint Block Plus Wrapper Core的源代码。对于Xilinx Spartan-3系列器件,设计中还包含了Endpoint PIPE for PCI Express的相关文件。

除了硬件设计外,笔记还提供了与之配套的内核模式驱动程序,支持Windows和Linux操作系统。同时,为了验证和测试设计,还提供了32位Windows和Linux的软件应用程序源代码。这些软件工具和驱动程序对于在不同平台上测试和调试总线主控设计至关重要。

通过这份应用笔记,开发者可以获得有关如何实现PCI Express总线主控的详细步骤,包括硬件设计、软件开发和系统集成,从而提升基于Xilinx FPGA的PCI Express系统的性能。这对于需要高速数据传输的嵌入式系统和数据中心应用具有很高的价值。

2019-06-25 上传

2021-10-11 上传

2019-08-26 上传

2015-03-26 上传

2022-09-12 上传

一个早起的程序员

- 粉丝: 4255

- 资源: 37

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新