高能效混合浮点FFT硬件加速器的VLSI设计研究

版权申诉

117 浏览量

更新于2024-07-03

收藏 6.06MB PDF 举报

"该文档详细探讨了高能效混合浮点快速傅里叶变换(FFT)硬件加速器的架构设计与VLSI实现方法。它首先介绍了FFT在数字无线通信、生物医疗信号处理等领域的应用背景,强调了硬件实现FFT的需求。接着,文档概述了低功耗技术的发展现状和高能效FFT加速器的研究进展。然后,深入阐述了FFT的算法原理,包括离散傅里叶变换、基2的时域抽取和频域抽取算法、基4和基8算法,以及更复杂的基22和基23算法。此外,还对FFT架构进行了分析,并提出了运算流程的优化策略,如定点实现。"

正文:

快速傅里叶变换(FFT)是一种高效的计算离散傅里叶变换(DFT)的方法,在众多领域如数字信号处理、图像处理、通信系统中扮演着重要角色。本研究聚焦于高能效的混合浮点FFT硬件加速器的构建,旨在解决随着数据量增大和处理速度需求提高,CPU处理FFT效率不足的问题。

在数字无线通信系统中,FFT被广泛应用于正交频分复用(OFDM)技术,能够有效利用频谱资源,提高传输速率。而在生物医疗信号处理中,FFT有助于分析心电图、脑电图等复杂信号,揭示其隐藏的频率特征。随着这些应用的需求增加,对高效硬件实现FFT的需求也日益迫切。

低功耗技术是当前集成电路设计的关键考虑因素,尤其是在移动设备和嵌入式系统中。文档中提到,当前低功耗技术正不断发展,包括电路层面的优化、工艺技术的进步以及新的电源管理策略。而高能效FFT加速器的研究则着重于如何在保持计算性能的同时,降低能耗,提升系统整体的能效比。

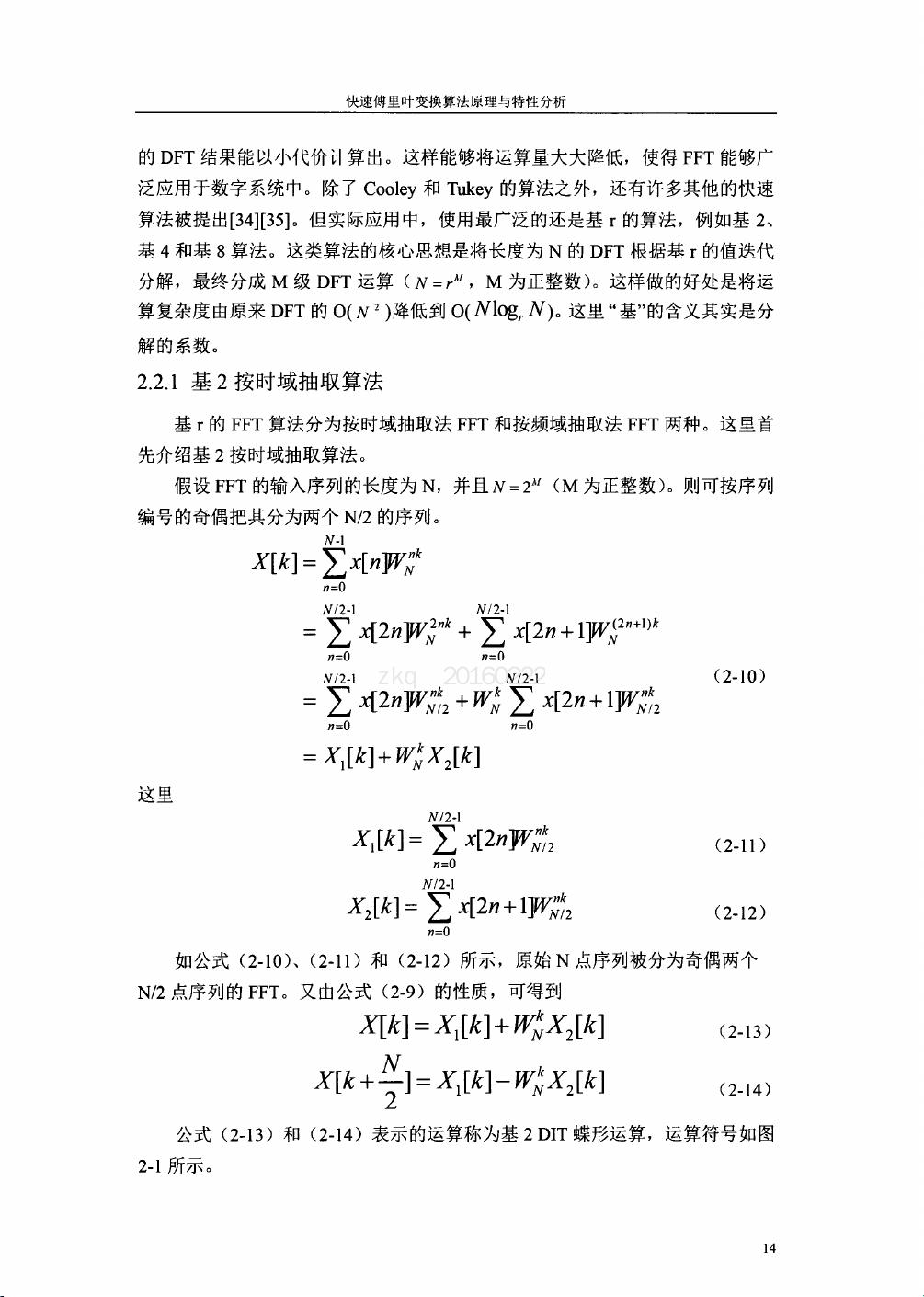

在算法层面,文档详细对比了各种FFT实现方式,包括基2的时域抽取和频域抽取算法,它们通过复用计算单元来减少计算量。基4和基8算法进一步提高了计算效率,适用于特定的数据长度。而基22和基23算法则适应了更广泛的输入大小,通过更精细的分解策略减少了计算复杂度。

在硬件架构上,设计者通常会考虑数据格式的选择,例如采用定点表示法,以减少硬件资源和功耗。同时,对运算流程进行优化,例如流水线设计、并行处理和存储结构的改进,都是为了提升运算速度和能效。

这篇研究详细阐述了FFT硬件加速器的设计与实现,从算法到硬件层面提供了全面的分析,对于理解和开发高性能、低功耗的FFT加速器具有重要的指导意义。通过对不同FFT算法的比较和硬件架构的优化,该研究为未来混合浮点FFT硬件加速器的进一步发展奠定了基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-06-17 上传

2021-09-25 上传

2021-07-13 上传

2021-09-25 上传

2021-07-13 上传

2019-08-22 上传

programmh

- 粉丝: 4

- 资源: 2162

最新资源

- DHCP-论文.zip

- Python库 | ladybug-rhino-1.33.2.tar.gz

- HCIP DAY1 静态路由与bfd联动实验拓扑

- dephpugger:Php Debugger可以在终端中运行以轻松调试代码

- python机器学习实例代码 - 交通流量预测.rar

- 易语言99乘法表代码-易语言

- Eindopdracht---Informatica---race-auto

- timeline_debug:时间轴调试

- 2023集创赛紫光同创杯一等奖项目.zip

- block_java_拦截短信_拦截_短信拦截_

- 平安保险微信小程序管理系统项目源码

- Python库 | ladybug-core-0.34.2.tar.gz

- klepto:持久缓存到内存,磁盘或数据库

- python-ffmpeg-音频格式转换程序(MP3-aac-wma-flac)(源代码)

- 易语言取QQkey源码-易语言

- valentinedifiore1729.github.io:adsfasdf