FPGA数字秒表:VHDL设计与EPlC6Q240实现

版权申诉

本文主要介绍了基于FPGA(Field-Programmable Gate Array)的数字秒表的设计,利用VHDL(Vera

HDL)这种高级硬件描述语言进行系统设计。VHDL的优势在于它允许在计算机上进行系统级的设计和仿真,显著减少了硬件设计周期,提升了开发效率。

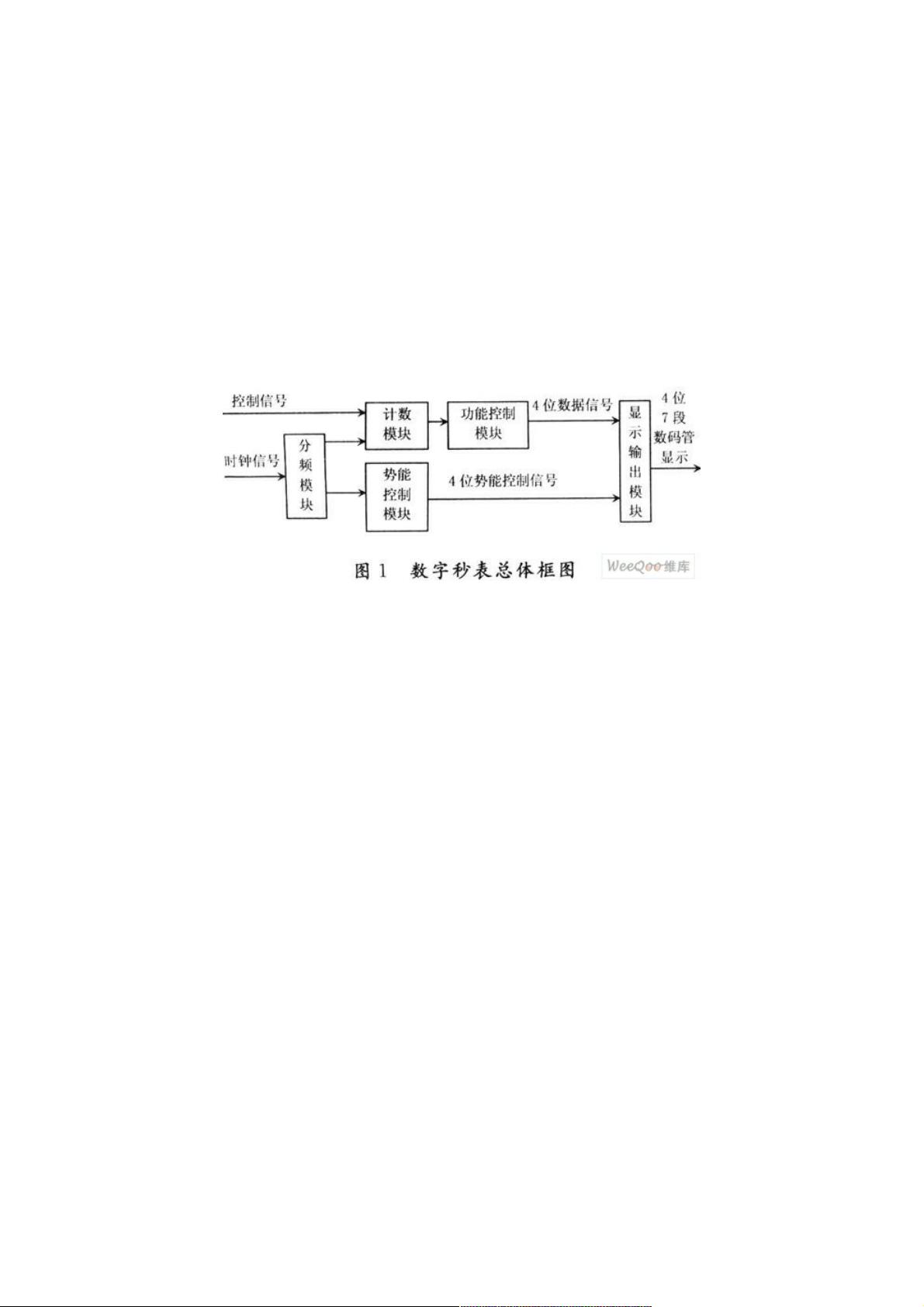

系统的核心组成部分包括:

1. 分频器:负责将主时钟信号进行分频,为计数模块和势能控制模块提供稳定的低频参考信号,使得秒表能够准确计数。

2. 计数模块:使用分频后的信号作为计数基准,实现对秒和百分秒的计数,采用60进制和100进制两种计数方式。

3. 功能控制模块:根据外部输入的控制信号,控制秒表在不同的功能状态间切换,如系统运行、归零和正常显示等。

4. 势能控制模块:管理系统的能源消耗,可能涉及定时器或电源管理,确保计数器和显示组件在需要时激活。

5. 显示输出模块:与4位7段数码管连接,负责将计数结果转换为可见的时间显示。

设计中使用的硬件平台是EPlC6Q240 FPGA开发板,它提供了丰富的外围电路和信号接口,便于系统集成。此外,该开发板还配备了4位7段数码管扩展板,为实际的显示功能提供了硬件支持。

通过VHDL设计,开发者可以编写详细的逻辑描述,然后在开发板上进行模拟和测试,确保系统的正确性和性能。源程序的公开使得其他研究人员可以复用或学习相关设计技巧。在整个设计过程中,作者强调了功能需求的明确性,如显示秒数、百分秒,以及灵活的功能切换和时间设定功能。

本文详细阐述了一个基于FPGA的数字秒表设计,涵盖了系统架构、功能模块划分、硬件平台选择以及VHDL编程和验证的全过程,对于理解和实践FPGA在数字系统设计中的应用具有较高的参考价值。

2020-10-19 上传

2023-06-24 上传

2022-02-09 上传

2023-09-06 上传

??2050

- 粉丝: 2

- 资源: 924

最新资源

- BGP协议首选值(PrefVal)属性与模拟组网实验

- C#实现VS***单元测试coverage文件转xml工具

- NX二次开发:UF_DRF_ask_weld_symbol函数详解与应用

- 从机FIFO的Verilog代码实现分析

- C语言制作键盘反应力训练游戏源代码

- 简约风格毕业论文答辩演示模板

- Qt6 QML教程:动态创建与销毁对象的示例源码解析

- NX二次开发函数介绍:UF_DRF_count_text_substring

- 获取inspect.exe:Windows桌面元素查看与自动化工具

- C语言开发的大丰收游戏源代码及论文完整展示

- 掌握NX二次开发:UF_DRF_create_3pt_cline_fbolt函数应用指南

- MobaXterm:超越Xshell的远程连接利器

- 创新手绘粉笔效果在毕业答辩中的应用

- 学生管理系统源码压缩包下载

- 深入解析NX二次开发函数UF-DRF-create-3pt-cline-fcir

- LabVIEW用户登录管理程序:注册、密码、登录与安全